# PFC/PWM Combo Controller with Integrated High Voltage Startup and Soft Skip Mode Standby Features

The NCP1603 is a Power Factor Correction (PFC) and Pulse Width Modulation (PWM) combo controller. It offers extremely low no-load standby power consumption that is suitable for the low-power consumer markets. The key features of the device are listed below.

#### **PFC Features**

- Near-Unity Power Factor in Discontinuous and Critical Mode (DCM and CRM)

- Voltage–Mode Operation

- Low Startup and Shutdown Current Consumption

- Programmable Switching Frequency for DCM

- Synchronization Capability

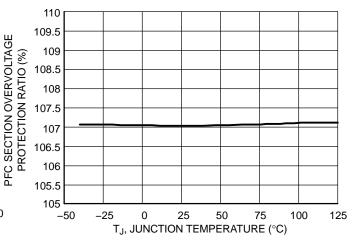

- Overvoltage Protection (107% of Nominal Output Level)

- Undervoltage Protection or Shutdown (8% of Nominal Output Level)

- Programmable Overcurrent Protection

- Thermal Shutdown with Hysteresis (95/140°C)

- Undervoltage Lockout with Hysteresis (9.0/10.5 V)

#### **PWM Features**

- Integrated Lossless High Voltage Startup Current Source

- 100 kHz PWM Current–Mode Operation with Soft Skip Mode Standby Skip Cycle Capability for Lower Audible Noise

- PFC Bias Voltage is Disabled in Standby Condition to Achieve Extremely Low No–Load Standby Power Consumption

- Fault Protection Implemented by a Timer and Independent of Badly Coupled Auxiliary Transformer Winding

- Primary Overcurrent Protection and Latched Overvoltage Protection

- Internal 2.5 ms Soft-Start

- ±6.4% Frequency Jittering for Improved EMI Performance

- Latched Thermal Shutdown with Hysteresis (140/165°C)

- Undervoltage Lockout with Hysteresis (5.6/7.7/12.6 V)

#### **Applications**

- Notebook Adapters

- TV/Monitors

http://onsemi.com

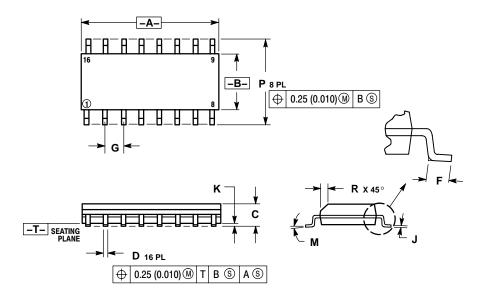

#### MARKING DIAGRAM

SO-16 D SUFFIX CASE 751B

A = Assembly Location

WL = Wafer Lot Y = Year

WW = Work Week

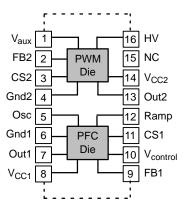

#### **PIN CONNECTIONS**

| $V_{\text{aux}}$ | 1 | 0 | 16 | HV               |

|------------------|---|---|----|------------------|

| FB2              | 2 |   | 15 | NC               |

| CS2              | 3 |   | 14 | $V_{\text{CC2}}$ |

| Gnd2             | 4 |   | 13 | Out2             |

| Osc              | 5 |   | 12 | Ramp             |

| Gnd1             | 6 |   | 11 | CS1              |

| Out1             | 7 |   | 10 | $V_{control}$    |

| $V_{\text{CC1}}$ | 8 |   | 9  | FB1              |

|                  |   |   |    |                  |

## (Top View) ORDERING INFORMATION

| Device        | Package | Shipping†        |  |  |

|---------------|---------|------------------|--|--|

| NCP1603D100R2 | SO-16   | 2500 Tape & Reel |  |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

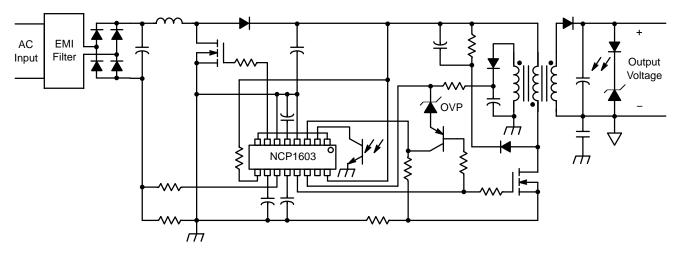

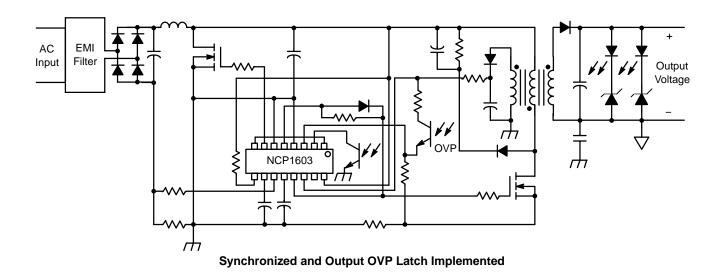

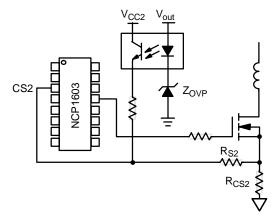

Not Synchronized and  $V_{\mbox{\scriptsize CC}}$  OVP Latch Implemented

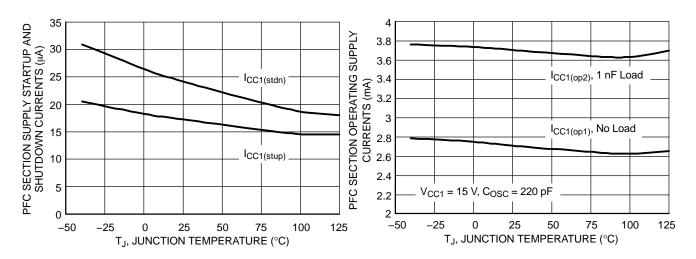

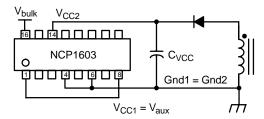

**Figure 1. Typical Application Circuits**

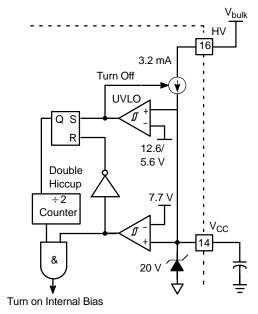

Figure 2. Functional Block Diagram

#### PIN FUNCTION DESCRIPTION

| 1  | V <sub>aux</sub>     | Auxiliary Supply    | This pin connects to the V <sub>CC1</sub> pin externally. It delivers a bias voltage from the V <sub>CC2</sub> to                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----|----------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

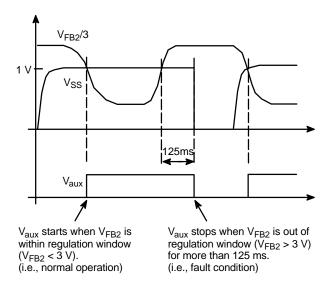

|    |                      |                     | the PFC section. The $V_{aux}$ is disabled when either one of the following conditions occurs: (1) $V_{aux}$ is initially off; (2) Fault ( $V_{FB2} > 3.0$ V for more than 125 ms); (3) Standby ( $V_{FB2} < 0.75$ V and then $V_{FB2}$ is smaller than 1.25 V for more than 125 ms); (4) Overvoltage protection latch activated from CS2 pin; (5) Thermal shutdown latch in the PWM section; (6) Insufficient supply voltage ( $V_{CC2} < 7.7$ V). The transistor turns on (or $V_{aux}$ is enabled) when $V_{FB2}$ is within the normal mode regulation window (0.75 V < $V_{FB2} < 3.0$ V). |

| 2  | FB2                  | PWM Feedback        | An external optocoupler collector pulls the voltage of this pin $V_{FB2}$ down to regulate the output voltage. The PWM regulation window between $V_{FB2} = 0.75$ V and $V_{FB2} = 3.0$ V. When $V_{FB2}$ drops below 0.75 V, the controller enters standby operation. When no feedback signal is received from the optocoupler, $V_{FB2}$ is internally pulled to be higher than 3.0 V. If this condition lasts for longer than 125 ms, the controller enters double–hiccup fault condition.                                                                                                  |

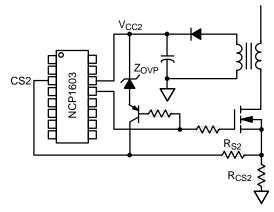

| 3  | CS2                  | PWM Current Sense   | This pin cumulates three different functions: current–mode PWM regulation, primary overcurrent protection and overvoltage protection (OVP). If the voltage of this pin is above 3.0 V for OVP, the circuit is latched off until $V_{CC2}$ resets. The PWM Drive Output is disabled.                                                                                                                                                                                                                                                                                                            |

| 4  | Gnd2                 | PWM Ground          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

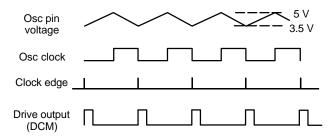

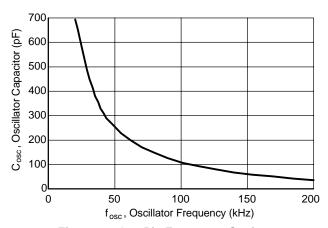

| 5  | Osc                  | PFC Oscillator      | In oscillator mode, this pin is connected to an external capacitor to set the oscillator frequency in DCM operation. In synchronization mode, this pin is connected to an external driving signal. However, if the PFC–stage inductor current is non–zero at the end of a switching period, the PFC–stage circuit will be forced to CRM and the Out1 is out of synchronization to the Osc pin signal.                                                                                                                                                                                          |

| 6  | Gnd1                 | PFC Ground          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7  | Out1                 | PFC Drive Output    | This pin provides an output to an external MOSFET in the PFC section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8  | V <sub>CC1</sub>     | PFC Supply Voltage  | This pin is the positive supply of the PFC section. the operating range is between 9.0 V and 18 V with UVLO start threshold 10.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

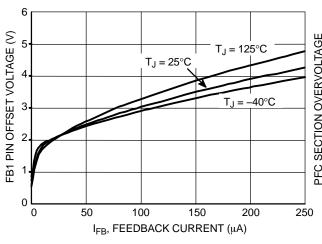

| 9  | FB1                  | PFC Feedback        | This pin receives a current I <sub>FB1</sub> that represents the PFC circuit output voltage. The current is for the output regulation, PFC section overvoltage protection (OVP) and PFC section output undervoltage protection (UVP). When I <sub>FB1</sub> goes above 107% I <sub>ref</sub> , OVP is activated and the Drive Output is disabled. When I <sub>FB1</sub> goes below 14 $\mu$ A, the PFC section enters a low–current consumption shutdown mode.                                                                                                                                 |

| 10 | V <sub>control</sub> | PFC Control Voltage | The control voltage $V_{control}$ directly controls the input impedance and hence the power factor of the circuit. This pin is connected to an external capacitor to limit the control voltage bandwidth typically below 20 Hz to achieve Power Factor Correction purpose.                                                                                                                                                                                                                                                                                                                     |

| 11 | CS1                  | PFC Current Sense   | This pin receives a current I <sub>S</sub> that is proportional to the inductor current. The current is for overcurrent protection (OCP), and zero current detection. When I <sub>S</sub> goes above 200 $\mu A$ , OCP is activated and the Drive Output (Out1) is disabled. When I <sub>S</sub> goes below 14 $\mu A$ , it is recognized to be a zero current for feedback regulation and DCM or CRM operation in the PFC oscillator section.                                                                                                                                                 |

| 12 | Ramp                 | PFC Ramp            | This pin is connected to an external capacitor to set a ramp signal. The capacitor value directly affects the input impedance of the PFC circuit and its maximum input power.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13 | Out2                 | PWM Drive Output    | This pin provides an output to an external MOSFET in the PWM section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14 | V <sub>CC2</sub>     | PWM Supply Voltage  | This pin is basically the positive supply of the PWM section. It is also the positive supply of the whole device because the PFC section is also supplied from this pin indirectly through $V_{aux}$ pin (Pin 1). The operating range is between 7.7 V and 18 V. The circuit resets when $V_{CC2}$ drops below 4.0 V.                                                                                                                                                                                                                                                                          |

| 15 | NC                   | No Connected        | This pin is for high voltage clearance of the HV pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16 | HV                   | High Voltage        | This pin connects to the bulk DC voltage to deliver power to the controller in startup or fault condition. The internal startup circuit is disabled in normal and standby condition for power saving purpose. The UVLO stop and start thresholds of the startup circuit are $V_{CC2} = 12.6 \text{ V}$ and $V_{CC2} = 5.6 \text{ V}$ .                                                                                                                                                                                                                                                         |

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                | Symbol                               | Value               | Unit    |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------|---------|

| V <sub>aux</sub> Pin (Pin 1) Maximum Voltage Range Maximum Continuous Current                                                         | V <sub>max</sub>                     | -0.3 to +18         | V       |

|                                                                                                                                       | I <sub>max</sub>                     | 35                  | mA      |

| FB2 and CS2 Pin (Pins 2–3)  Maximum Voltage Range  Maximum Current                                                                    | V <sub>max</sub>                     | -0.3 to +10         | V       |

|                                                                                                                                       | I <sub>max</sub>                     | 100                 | mA      |

| Ramp, CS1, V <sub>control</sub> , FB1, and Osc Pins (Pins 5, 9–12)<br>Maximum Voltage Range<br>Maximum Current                        | V <sub>max</sub><br>I <sub>max</sub> | -0.3 to +9.0<br>100 | V<br>mA |

| Out1 Pin (Pin 7) Maximum Voltage Range Maximum Current                                                                                | V <sub>max</sub>                     | -0.3 to +18         | V       |

|                                                                                                                                       | I <sub>max</sub>                     | -500 to +750        | mA      |

| V <sub>CC1</sub> and V <sub>CC2</sub> Pins (Pins 8, 14) Maximum Voltage Range Maximum Current                                         | V <sub>max</sub>                     | -0.3 to +18         | V       |

|                                                                                                                                       | I <sub>max</sub>                     | 100                 | mA      |

| Out2 Pin (Pin 13) Maximum Voltage Range Maximum Current                                                                               | V <sub>max</sub>                     | -0.3 to +17.5       | V       |

|                                                                                                                                       | I <sub>max</sub>                     | 1.0                 | A       |

| HV Pin (Pin 16) Maximum Voltage Range Maximum Current                                                                                 | V <sub>max</sub>                     | -0.3 to +500        | V       |

|                                                                                                                                       | I <sub>max</sub>                     | 100                 | mA      |

| Power Dissipation and Thermal Characteristics  Maximum Power Dissipation (T <sub>A</sub> = 25°C)  Thermal Resistance, Junction–to–Air | P <sub>D</sub>                       | 770                 | mW      |

|                                                                                                                                       | R <sub>0JA</sub>                     | 111                 | °C/W    |

| Operating Junction Temperature Range                                                                                                  | TJ                                   | -40 to +125         | °C      |

| Maximum Storage Temperature Range                                                                                                     | T <sub>stg</sub>                     | -60 to +150         | °C      |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

1. This device contains ESD protection and exceeds the following tests:

Pin 1–14: Human Body Model 2000 V per Mil–Std–883, Method 3015.

Machine Model Method 200 V.

Pin 16 is the HV startup of the device and is rated to the maximum rating of the part, or 500 V.

<sup>2.</sup> This device contains latchup protection and exceeds 100 mA per JEDEC Standard JESD78.

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_J = 25^{\circ}C$ , for min/max values,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC2} = 13$  V,  $HV = 30 \text{ V}, V_{CC1} = 15 \text{ V}, V_{control} = 100 \text{ nF}, Ramp = 330 \text{ pF}, Osc = 220 \text{ pF} unless otherwise specified}$ .

| Characteristic (PWM Section)                                                                                                                                                                                                                                                                                        | Pin | Symbol                                                   | Min              | Тур              | Max               | Unit           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------|------------------|------------------|-------------------|----------------|

| PWM Oscillator                                                                                                                                                                                                                                                                                                      | 1   | •                                                        |                  |                  |                   |                |

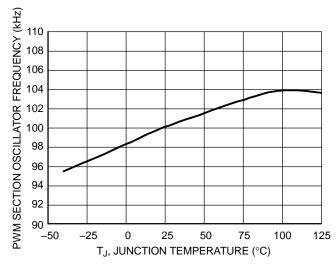

| Oscillation Frequency ( $T_J = 25^{\circ}C$ ) (Note 3)<br>Oscillation Frequency ( $T_J = 0^{\circ}C$ to +125°C)<br>Oscillation Frequency ( $T_J = -40^{\circ}C$ to +125°C)                                                                                                                                          | _   | f <sub>osc2</sub>                                        | 93<br>90<br>85   | 100<br>-<br>-    | 107<br>110<br>110 | kHz            |

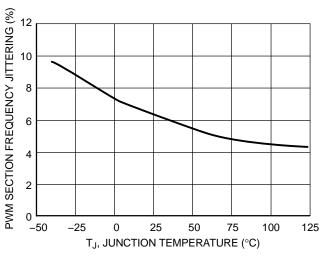

| Oscillator Modulation Swing, in Percentage of fosc2                                                                                                                                                                                                                                                                 | _   | -                                                        | _                | ±6.4             | -                 | %              |

| Oscillator Modulation Swing Period                                                                                                                                                                                                                                                                                  | _   | -                                                        | _                | 5.0              | -                 | ms             |

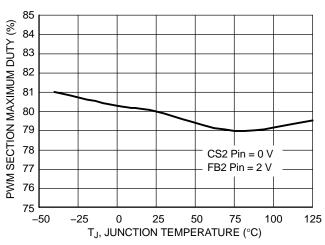

| Maximum Duty Ratio (V <sub>CS2</sub> = 0 V, V <sub>FB2</sub> = 2.0 V)                                                                                                                                                                                                                                               | _   | D <sub>max</sub>                                         | 75               | 80               | 85                | %              |

| PWM Gate Drive                                                                                                                                                                                                                                                                                                      |     |                                                          |                  |                  |                   |                |

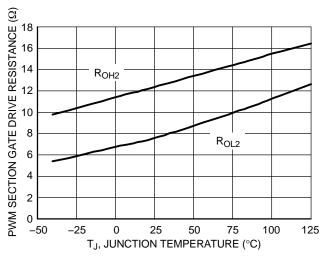

| Gate Drive Resistor<br>Output High ( $V_{CC2}$ = 13 V, Out2 = 300 $\Omega$ to Gnd2)<br>Output Low (Out2 = 1.0 V, $V_{FB2}$ = 0 V)                                                                                                                                                                                   | 13  | R <sub>OH2</sub><br>R <sub>OL2</sub>                     | 6.0<br>3.0       | 12.3<br>7.5      | 25<br>18          | Ω<br>Ω         |

| Gate Drive Rise Time from 10% to 90% (Out2 = 1.0 nF to Gnd2)                                                                                                                                                                                                                                                        | 13  | t <sub>r2</sub>                                          | _                | 40               | -                 | ns             |

| Gate Drive Fall Time from 90% to 10% (Out2 = 1.0 nF to Gnd2)                                                                                                                                                                                                                                                        | 13  | t <sub>f2</sub>                                          | -                | 15               | -                 | ns             |

| PWM Current Sense/Overvoltage Protection                                                                                                                                                                                                                                                                            |     |                                                          |                  |                  |                   |                |

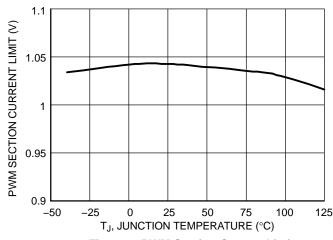

| Maximum Current Threshold ( $T_J = 25^{\circ}C$ )<br>Maximum Current Threshold ( $T_J = -40^{\circ}C$ to +125°C)                                                                                                                                                                                                    | 3   | l <sub>Limit</sub>                                       | 0.991<br>0.96    | 1.043<br>–       | 1.095<br>1.106    | V              |

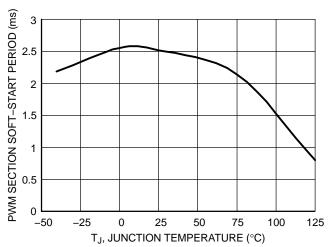

| Soft-Start/Soft-Skip Duration                                                                                                                                                                                                                                                                                       | -   | t <sub>SS</sub>                                          | 1                | 2.5              | -                 | ms             |

| Leading Edge Blacking Duration                                                                                                                                                                                                                                                                                      | 3   | t <sub>LEB</sub>                                         | 100              | 200              | 350               | ns             |

| Propagation Delay from CS Detected to Turn Out2 Off                                                                                                                                                                                                                                                                 | _   | T <sub>delay(CS)</sub>                                   | _                | 90               | 180               | ns             |

| Overvoltage Protection Threshold                                                                                                                                                                                                                                                                                    | 3   | V <sub>OVP</sub>                                         | 2.7              | 3.0              | 3.3               | V              |

| Internal Compensation Ramp (Peak-to-Peak) (Note 4)                                                                                                                                                                                                                                                                  | 3   | V <sub>comp</sub>                                        | -                | 2.3              | -                 | V              |

| Internal Resistor to Ramp (Note 4)                                                                                                                                                                                                                                                                                  | 3   | R <sub>comp</sub>                                        | 9.0              | 18               | 36                | kΩ             |

| PWM Standby Thresholds/Feedback                                                                                                                                                                                                                                                                                     |     |                                                          |                  |                  |                   |                |

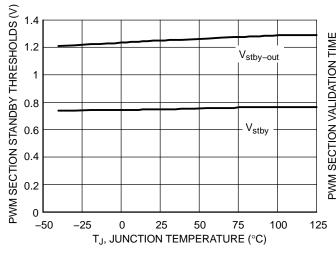

| Standby Thresholds Feedback Voltage V <sub>FB2</sub> to Start Standby Feedback Voltage V <sub>FB2</sub> to Stop Standby                                                                                                                                                                                             | 2   | V <sub>stby</sub><br>V <sub>stby-out</sub>               | 0.6<br>1.0       | 0.75<br>1.25     | 0.9<br>1.5        | V              |

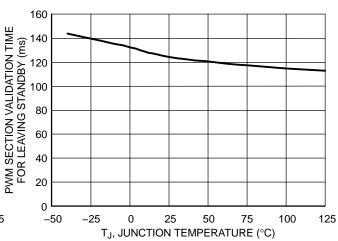

| Validation Time for Leaving Standby                                                                                                                                                                                                                                                                                 | 2   | t <sub>stby-aux</sub>                                    | _                | 125              | _                 | ms             |

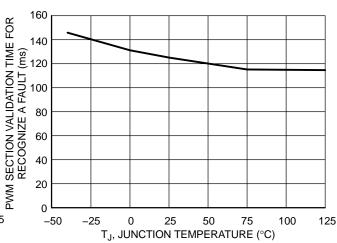

| Validation Time for Recognize a Fault                                                                                                                                                                                                                                                                               | 2   | t <sub>fault</sub>                                       | _                | 125              | -                 | ms             |

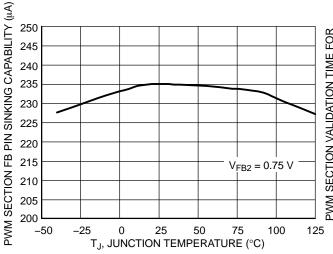

| Feedback Pin Sinking Capability (V <sub>FB2</sub> = 0.75 V)                                                                                                                                                                                                                                                         | 2   | I <sub>FB2</sub>                                         | 200              | 235              | 270               | μΑ             |

| Auxiliary Supply                                                                                                                                                                                                                                                                                                    |     |                                                          |                  |                  |                   |                |

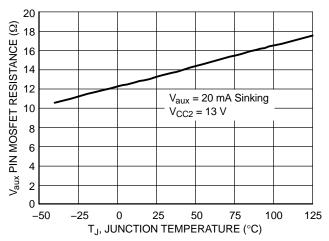

| $V_{aux}$ MOSFET Resistance ( $V_{CC2}$ = 13 V, $V_{FB}$ = 2.0 V, $V_{aux}$ = 20 mA Sinking)                                                                                                                                                                                                                        | 1   | R <sub>aux</sub>                                         | 6.0              | 11.7             | 23                | Ω              |

| PWM Thermal Shutdown                                                                                                                                                                                                                                                                                                |     |                                                          | •                |                  |                   |                |

| Thermal Shutdown Threshold (Note 4)                                                                                                                                                                                                                                                                                 | -   | T <sub>SD2</sub>                                         | 150              | 165              | -                 | °C             |

| Thermal Shutdown Hysteresis                                                                                                                                                                                                                                                                                         | _   | T <sub>H2</sub>                                          | -                | 25               | -                 | °C             |

| PWM Startup Current Source                                                                                                                                                                                                                                                                                          |     |                                                          |                  |                  |                   |                |

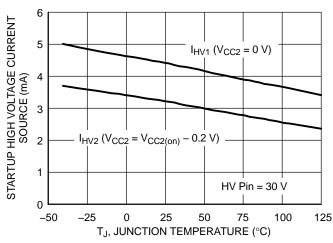

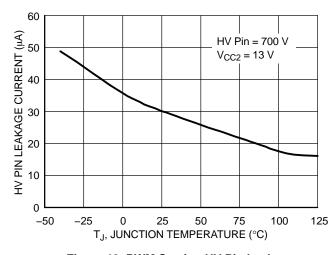

| $\begin{aligned} & \text{High-Voltage Current Source} \\ & \text{Startup (V}_{CC2} = \text{V}_{CC2(on)} - 0.2 \text{ V, V}_{FB2} = 2.0 \text{ V, HV} = 30 \text{ V)} \\ & \text{Startup (V}_{CC2} = 0 \text{ V, HV} = 30 \text{ V)} \\ & \text{Leakage (V}_{CC2} = 13 \text{ V, HV} = 700 \text{ V)} \end{aligned}$ | 16  | I <sub>HV1</sub><br>I <sub>HV2</sub><br>I <sub>HV3</sub> | 1.8<br>1.8<br>10 | 3.2<br>4.4<br>30 | 4.2<br>5.6<br>80  | mA<br>mA<br>μA |

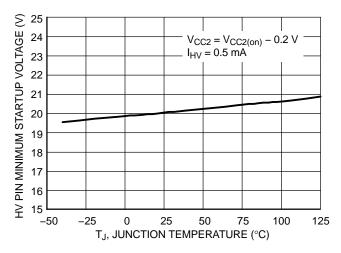

| Minimum Startup Voltage ( $V_{CC2} = V_{CC2(on)} - 0.2 \text{ V}, I_{HV} = 0.5 \text{ mA}$ )                                                                                                                                                                                                                        | 16  | V <sub>start(min)</sub>                                  | _                | 20               | 23                | V              |

Consult factory for other frequency options.

Guaranteed by design.

**ELECTRICAL CHARACTERISTICS (continued)** (For typical values  $T_J = 25^{\circ}$ C, for min/max values,  $T_J = -40^{\circ}$ C to +125°C,  $V_{CC2} = 13 \text{ V}$ ,  $V_{HV} = 30 \text{ V}$ ,  $V_{CC1} = 15 \text{ V}$ ,  $V_{Control} = 100 \text{ nF}$ , Ramp = 330 pF, Osc = 220 pF unless otherwise specified).

| Characteristic (PWM Section)                                                                                                                                                                                 | Pin | Symbol                                                              | Min                | Тур                       | Max                | Unit           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------|--------------------|---------------------------|--------------------|----------------|

| PWM Supply Section                                                                                                                                                                                           |     |                                                                     |                    |                           |                    |                |

| Supply Voltage Startup Threshold, V <sub>CC2</sub> Increasing Minimum Operating Valley Voltage after Turn–On Undervoltage Lockout Threshold Voltage, V <sub>CC2</sub> Decreasing Logic Reset Level           | 14  | VCC2(on)<br>VCC2(off)<br>VCC2(latch)<br>VCC2(reset)                 | 11.6<br>7.0<br>5.0 | 12.6<br>7.7<br>5.6<br>4.0 | 13.6<br>8.4<br>6.2 | V<br>V<br>V    |

| Supply Current Operating ( $V_{CC2}$ = 13 V, Out2 = Open, $V_{FB2}$ = 2.0 V) Operating ( $V_{CC2}$ = 13 V, Out2 = 1.0 nF to Gnd2, $V_{FB2}$ = 2.0 V) Latch–Off Phase ( $V_{CC2}$ = 6.5 V, $V_{FB2}$ = 2.0 V) | 14  | I <sub>CC2(op1)</sub> I <sub>CC2(op2)</sub> I <sub>CC2(latch)</sub> | 0.6<br>1.3<br>400  | 1.1<br>2.2<br>680         | 1.8<br>3.0<br>1000 | mA<br>mA<br>μA |

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_J = 25^{\circ}$ C, for min/max values,  $T_J = -40^{\circ}$ C to +125°C,  $V_{CC2} = 13$  V,  $V_{CC1} = 15$  V,  $V_{Control} = 100$  nF, Ramp = 330 pF, Osc = 220 pF unless otherwise specified).

| Characteristic (PFC Section)                                                                                                                                           | Pin | Symbol                               | Min        | Тур         | Max      | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------|------------|-------------|----------|------|

| PFC Oscillator                                                                                                                                                         |     |                                      |            | •           |          |      |

| Oscillator Frequency (Osc = 220 pF to Gnd)                                                                                                                             | 5   | f <sub>osc1</sub>                    | 52         | 58          | 64       | kHz  |

| Internal Capacitance of the Oscillator Pin                                                                                                                             | 5   | C <sub>osc(int)</sub>                | -          | 36          | -        | pF   |

| Maximum Oscillator Switching Frequency                                                                                                                                 | 5   | f <sub>osc1(max)</sub>               | -          | 405         | -        | kHz  |

| Oscillator Discharge Current (Osc = 5.5 V)                                                                                                                             | 5   | I <sub>odch</sub>                    | 40         | 49          | 60       | μΑ   |

| Oscillator Charge Current (Osc = 3.0 V)                                                                                                                                | 5   | I <sub>och</sub>                     | 40         | 45          | 60       | μΑ   |

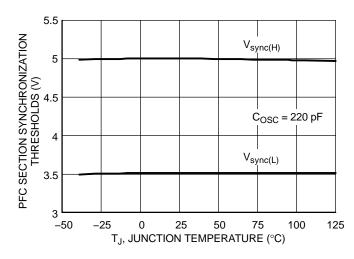

| Comparator Lower Threshold (Osc = 220 pF to Gnd) (Note 5)                                                                                                              | 5   | V <sub>sync(L)</sub>                 | 3.0        | 3.5         | 4.0      | V    |

| Comparator Upper Threshold (Osc = 220 pF to Gnd)                                                                                                                       | 5   | V <sub>sync(H)</sub>                 | 4.5        | 5.0         | 5.5      | V    |

| Synchronization Pulse Width for Detection                                                                                                                              | 5   | t <sub>sync(min)</sub>               | 500        | _           | -        | ns   |

| Synchronization Propagation Delay                                                                                                                                      | 5   | t <sub>sync(d)</sub>                 | -          | 371         | -        | ns   |

| PFC Gate Drive                                                                                                                                                         |     |                                      |            |             |          |      |

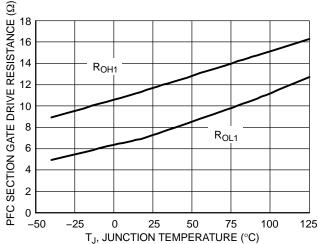

| Gate Drive Resistor Output High and Draw 100 mA out of Out1 Pin (I <sub>source</sub> = 100 mA) Output Low and Insert 100 mA into Out1 Pin (I <sub>sink</sub> = 100 mA) | 7   | R <sub>OH1</sub><br>R <sub>OL1</sub> | 5.0<br>2.0 | 11.6<br>7.2 | 20<br>18 | ΩΩ   |

| Gate Drive Rise Time from 1.5 V to 13.5 V (Out1 = 1.0 nF to Gnd)                                                                                                       | 7   | t <sub>r1</sub>                      | -          | 53          | -        | ns   |

| Gate Drive Fall Time from 13.5 V to 1.5 V (Out1 = 1.0 nF to Gnd)                                                                                                       |     | t <sub>f1</sub>                      | _          | 32          | _        | ns   |

| PFC Feedback/Overvoltage Protection/Undervoltage Protection                                                                                                            | on  |                                      |            |             |          |      |

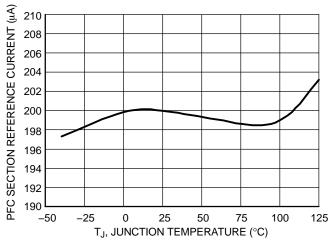

| Reference Current (T <sub>J</sub> = 0°C to +105°C)                                                                                                                     | 9   | I <sub>ref</sub>                     | 194        | 200         | 206      | μΑ   |

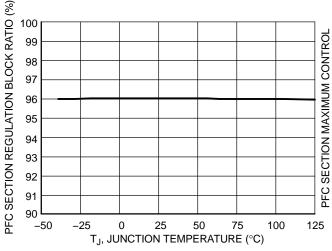

| Regulation Block Ratio                                                                                                                                                 | 9   | I <sub>regL</sub> /I <sub>ref</sub>  | 95         | 96          | 97       | %    |

| Vcontrol Pin Internal Resistor                                                                                                                                         | 10  | R <sub>control</sub>                 | -          | 300         | -        | kΩ   |

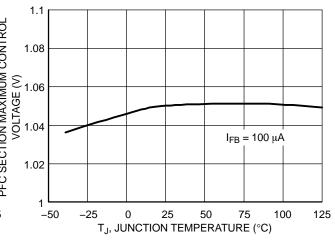

| Maximum Control Voltage (I <sub>FB1</sub> = 100 μA)                                                                                                                    | 10  | V <sub>control(max)</sub>            | 0.95       | 1.05        | 1.15     | V    |

| Feedback Pin Voltage (I <sub>FB1</sub> = 100 μA)                                                                                                                       | 9   | V <sub>FB1-100</sub>                 | -          | 3.0         | -        | V    |

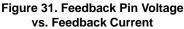

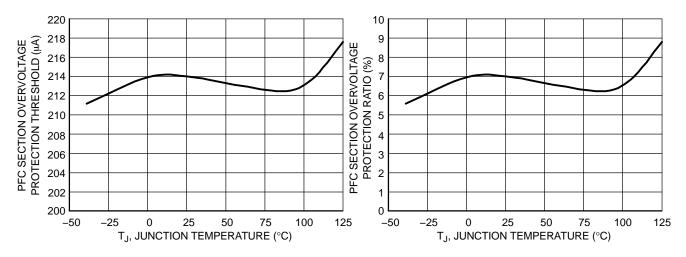

| Overvoltage Protection Current Ratio                                                                                                                                   | 9   | I <sub>OVP</sub> /I <sub>ref</sub>   | 104        | 107         | -        | %    |

| Overvoltage Protection Current Threshold                                                                                                                               | 9   | I <sub>OVP</sub>                     | -          | 214         | 225      | μΑ   |

| Undervoltage Protection Current Threshold                                                                                                                              | 9   | I <sub>UVP</sub> /I <sub>ref</sub>   | 4.0        | 8.0         | 15       | %    |

| PFC Current Sense                                                                                                                                                      |     |                                      |            |             |          |      |

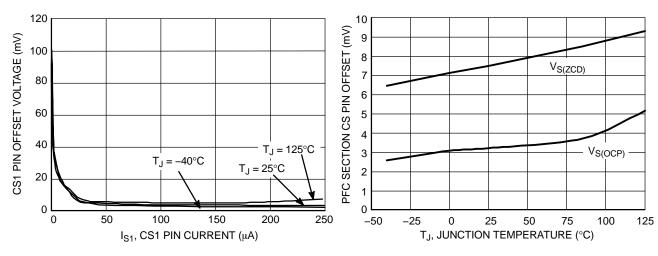

| Current Sense Pin Offset Voltage (I <sub>S</sub> = 100 μA)                                                                                                             | 11  | Vs                                   | -          | 4.0         | -        | mV   |

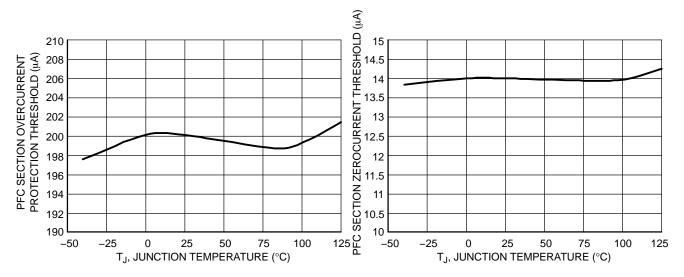

| Overcurrent Protection Level                                                                                                                                           | 11  | I <sub>S(OCP)</sub>                  | 190        | 200         | 210      | μΑ   |

| Current Sense Pin Offset Voltage at Overcurrent Level                                                                                                                  | 11  | V <sub>S(OCP)</sub>                  | 0          | 3.2         | 20       | mV   |

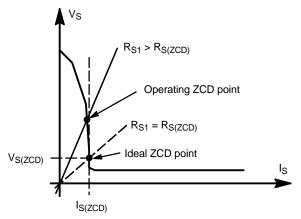

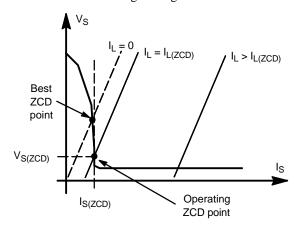

| Zero Current Detection Level                                                                                                                                           | 11  | I <sub>S(ZCD)</sub>                  | 9          | 14          | 19       | μΑ   |

| Current Sense Pin Offset Voltage at Zero Current Level                                                                                                                 | 11  | V <sub>S(ZCD)</sub>                  | 0          | 7.5         | 20       | mV   |

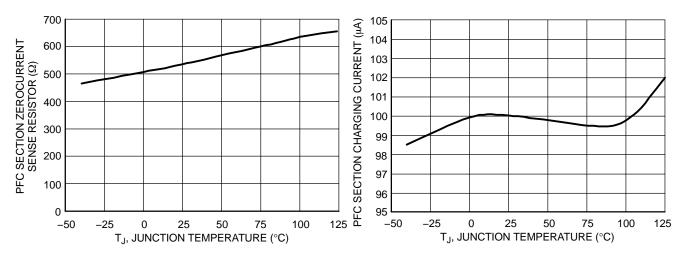

| Zero Current Sense Resistor (R <sub>S(ZCD)</sub> = V <sub>S(ZCD)</sub> /I <sub>S(ZCD)</sub> )                                                                          | 11  | R <sub>S(ZCD)</sub>                  | _          | 0.536       | 1.0      | kΩ   |

<sup>5.</sup> Comparator lower threshold is also the synchronization threshold.6. Guaranteed by design.

**ELECTRICAL CHARACTERISTICS (continued)** (For typical values  $T_J = 25^{\circ}C$ , for min/max values,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC2} = 13 \text{ V}$ , HV = 30 V,  $V_{CC1} = 15 \text{ V}$ ,  $V_{control} = 100 \text{ nF}$ , Ramp = 330 pF, Osc = 220 pF unless otherwise specified).

| Characteristic (PFC Section)                                                                                                                                                                                                       | Pin | Symbol                                                                                        | Min                | Тур                    | Max                    | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------|--------------------|------------------------|------------------------|----------------------|

| PFC Ramp                                                                                                                                                                                                                           |     |                                                                                               |                    |                        |                        |                      |

| Charging Current (Ramp = 0 V)                                                                                                                                                                                                      | 12  | I <sub>ch</sub>                                                                               | 95                 | 100                    | 105                    | μΑ                   |

| Maximum Power Resistance (R <sub>power</sub> = V <sub>control(max)</sub> /I <sub>ch</sub> )                                                                                                                                        | 12  | R <sub>power</sub>                                                                            | 9.5                | 10                     | 11.5                   | kΩ                   |

| Internal Clamping of Voltage V <sub>ton</sub>                                                                                                                                                                                      | _   | V <sub>ton(max)</sub>                                                                         | _                  | 3.9                    | _                      | V                    |

| Internal Capacitance of the Ramp Pin                                                                                                                                                                                               | 12  | C <sub>ramp(int)</sub>                                                                        | _                  | 22                     | _                      | pF                   |

| Ramp Pin Sink Resistance<br>(Osc = 0 V, Ramp = 1.0 mA sourcing)                                                                                                                                                                    |     | R <sub>ramp</sub>                                                                             | -                  | 71.5                   | _                      | Ω                    |

| PFC Thermal Shutdown                                                                                                                                                                                                               |     | •                                                                                             | <del>'</del>       |                        |                        | *                    |

| Thermal Shutdown Threshold (Note 7)                                                                                                                                                                                                | -   | T <sub>SD1</sub>                                                                              | 140                | 170                    | _                      | °C                   |

| Thermal Shutdown Hysteresis                                                                                                                                                                                                        |     | T <sub>H1</sub>                                                                               | _                  | 45                     | _                      | °C                   |

| PFC Supply Section                                                                                                                                                                                                                 |     |                                                                                               |                    |                        |                        |                      |

| Supply Voltage Startup Threshold (UVLO) Minimum Voltage for Operation after Turn-On UVLO Hysteresis                                                                                                                                | 8   | V <sub>CC1(on)</sub><br>V <sub>CC1(off)</sub><br>V <sub>H1</sub>                              | 9.6<br>8.25<br>1.0 | 10.5<br>9.0<br>1.5     | 11.4<br>9.75<br>–      | V<br>V<br>V          |

| Supply Current Start-Up ( $V_{CC1} = V_{CC1(on)}$ -0.2 V) Operating ( $V_{CC1} = 15$ V, Out1 = Open, Osc = 220 pF) Operating ( $V_{CC1} = 15$ V, Out1 = 1.0 nF to Gnd1, Osc = 220 pF) Shutdown ( $V_{CC1} = 15$ V, $I_{FB} = 0$ A) | 8   | I <sub>CC1</sub> (stup) I <sub>CC1</sub> (op1) I <sub>CC1</sub> (op2) I <sub>CC1</sub> (stdp) | -<br>-<br>-        | 17<br>2.7<br>3.7<br>24 | 40<br>5.0<br>5.0<br>50 | μΑ<br>mA<br>mA<br>μΑ |

<sup>7.</sup> Comparator lower threshold is also the synchronization threshold.8. Guaranteed by design.

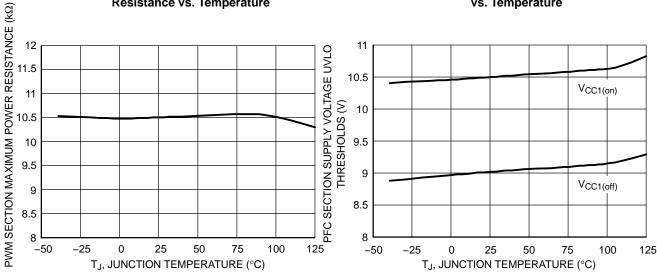

Figure 3. PWM Section Oscillator Frequency vs. Temperature

Figure 4. PWM Section Oscillator Frequency

Jittering vs. Temperature

Figure 5. PWM Section Maximum Duty vs. Temperature

Figure 6. PWM Section Gate Drive Resistance vs. Temperature

Figure 7. PWM Section Current Limit vs. Temperature

Figure 8. PWM Section Soft-Start/Soft-Skip Period vs. Temperature

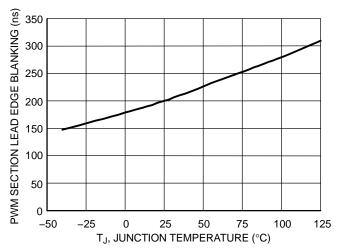

Figure 9. PWM Section Lead Edge Blanking vs. Temperature

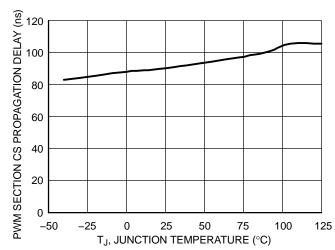

Figure 10. CS2 Pin Propagation Delay vs. Temperature

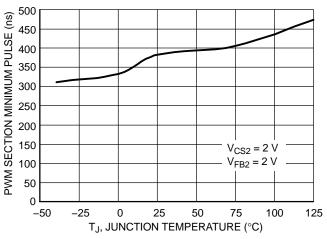

Figure 11. PWM Section Minimum Output Pulse vs. Temperature

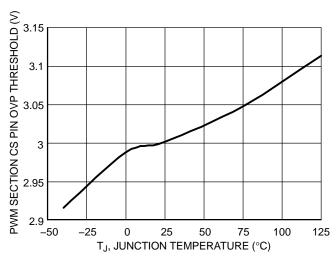

Figure 12. CS2 Pin Overvoltage Protection Threshold vs. Temperature

Figure 13. PWM Section Standby Thresholds vs. Temperature

Figure 14. PWM Section Validation Time for Leaving Standby vs. Temperature

Figure 15. FB2 Pin Sinking Capability vs. Temperature

Figure 16. PWM Section Validation Time for Recognizing a Fault vs. Temperature

Figure 17. V<sub>aux</sub> Pin Internal MOSFET Resistance vs. Temperature

Figure 18. PWM Section High Voltage Startup

Current Source vs. Temperature

Figure 19. PWM Section HV Pin Leakage Current vs. Temperature

Figure 20. PWM Section HV Pin Minimum Operating Voltage vs. Temperature

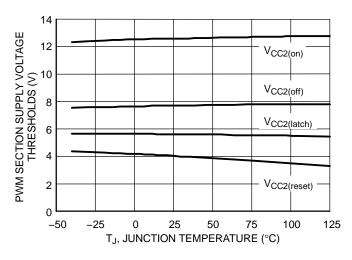

Figure 21. PWM Section Supply Voltage Thresholds vs. Temperature

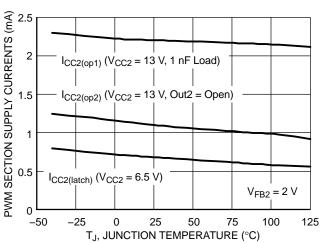

Figure 22. PWM Section Supply Currents vs. Temperature

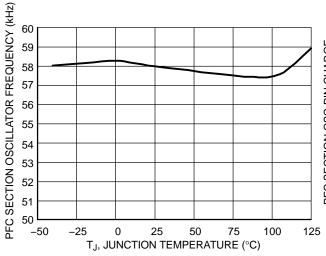

Figure 23. PFC Section Oscillator Frequency vs. Temperature

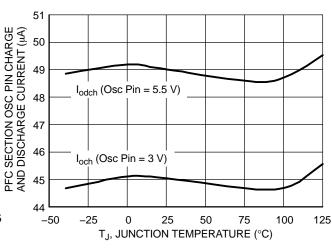

Figure 24. PFC Section Osc Pin Charge and Discharge Current vs. Temperature

Figure 25. PFC Section Synchronization Thresholds vs. Temperature

Figure 26. PFC Section Gate Drive Resistance vs. Temperature

PFC SECTION REGULATION BLOCK (V) 1.2 1  $T_J = 25^{\circ}C$ 8.0 0.6 0.4  $T_J = 125^{\circ}C$ 0.2 0 160 170 180 190 200 210 220 150  $I_{FB}$ , FEEDBACK CURRENT ( $\mu A$ )

Figure 27. PFC Section Reference Current vs. Temperature

Figure 28. PFC Section Regulation Block Transfer Function

Figure 29. PFC Section Regulation Block vs. Temperature

Figure 30. PFC Section Maximum Control Voltage vs. Temperature

Figure 32. PFC Section Overvoltage Protection Ratio vs. Temperature

Figure 33. PFC Section Overvoltage Protection Threshold vs. Temperature

Figure 34. PFC Section Overvoltage Protection Ratio vs. Temperature

Figure 35. CS1 Pin Offset Voltage vs. Current

Figure 36. PFC Section CS Pin Offset vs. Temperature

Figure 37. PFC Section Overcurrent Protection Threshold vs. Temperature

Figure 38. PFC Section Zerocurrent Threshold vs. Temperature

Figure 39. PFC Section Zerocurrent Sense Resistance vs. Temperature

Figure 40. PFC Section Charging Current vs. Temperature

Figure 41. PFC Section Maximum Power Resistance vs. Temperature

Figure 42. PFC Section Supply Voltage Undervoltage Lockout Thresholds vs. Temperature

Figure 43. PFC Section Supply Current in Startup and Shutdown Conditions vs. Temperature

Figure 44. PFC Section Operating Supply Currents vs. Temperature

#### OPERATING DESCRIPTION

Figure 45. Typical Application Circuit

#### Introduction

The NCP1603 is a PWM/PFC combo controller for two–stages PFC low–power application. A typical application circuit is listed in Figure 45. The first–stage PFC boost circuit draws a near–unity power factor current from the input but it also steps up the rectified input voltage  $V_{in}$  to a high bulk voltage  $V_{bulk}$  in the bulk capacitor  $C_{bulk}$ . Then, the second–stage PWM flyback circuit converts the bulk voltage  $V_{bulk}$  to a usable low voltage and isolated output voltage  $V_{out}$ . The controllers of the two stages are combined to become a single PWM/PFC combo controller. The advantages of NCP1603 are the following:

- 1. Integrated maximum 500 V lossless high voltage startup circuit that saves area and power loss.

- 2. Low standby power consumption because of PFC shutdown and skipping cycle operation.

- 3. Soft skip mode skipping cycle operation for minimizing audible noise in standby operation.

- Proprietary PFC methodology limits the maximum switching frequency and frequency jittering feature of the second–stage make the easier front–ended EMI filter design.

- 5. Internal ramp compensation for stability improvement in the second stage converter.

- 6. Minimum number of external components.

- Optional synchronization capability between the PFC and PWM sections for ripple current reduction.

- 8. Safety protection features.

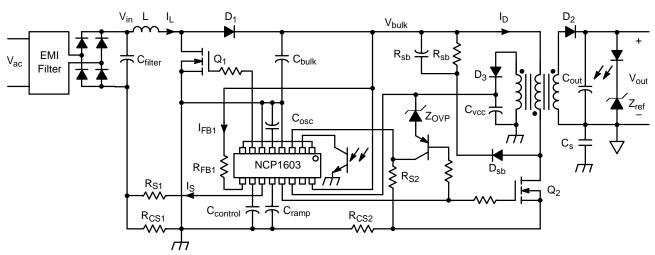

NCP1603 is a co-package of two individual IC dies. The PFC die links up pin 5 to pin 12 that are in the lower half of Figure 46. The PWM die links up the other pins that are in the upper half of Figure 46. For simplicity, the PFC pins are named with suffix one that stands for the first stage and the PWM pins are named with suffix two that stands for the second stage.

Figure 46. Internal Connection

#### Biasing the Controller

The PWM section is the master section that always operates. The PFC section is the slave section that is off in standby condition for power saving while the PWM section is still operating to deliver output voltage to the second–stage load. It is implemented by connecting  $V_{aux}$  pin (Pin 1) and  $V_{CC1}$  pin (Pin 8) together externally. The  $V_{CC1}$  pin generally requires a small decoupling external capacitor (0.1  $\mu$ F) or nothing. The PWM section powers the PFC section. The  $V_{CC}$  of the whole device refers to  $V_{CC2}$  (Pin 14) in the PWM section (i.e.,  $V_{CC} = V_{CC2}$ ).

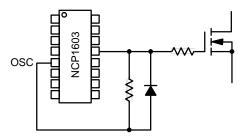

Figure 47. Bias Supply Schematic

The recommended biasing schematic of the controller is in Figure 47 while a typical completed application schematic can be referred to Figure 45. These two dies have their own individual supply voltages at Pin 8 and Pin 14. The grounds of the two dies are physically connected through the package substrate but they are needed to be connected externally. The bias voltage to the NCP1603 comes from the bulk voltage  $V_{bulk}$  through the HV pin (Pin 16) during startup. After startup, a second–stage flyback transformer auxiliary winding delivers the supply voltage to  $V_{CC}$ .

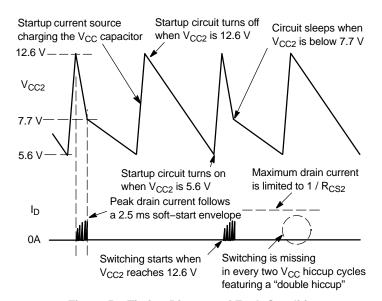

#### **Lossless High Voltage Startup Circuit**

Figure 48. V<sub>CC2</sub> Management

The HV pin (Pin 16) is capable of the maximum 500 V so that this pin can be directly connected to the bulk voltage  $V_{bulk}$  and delivers startup supply voltage to the controller. Figure 48 illustrates the block diagram of the startup circuit. An UVLO comparator monitors the  $V_{CC}$  at Pin 14. A startup current source is activated and deactivated whenever the voltage reaches  $V_{CC2(latch)}$  (5.6 V typical) and  $V_{CC2(on)}$  (12.6 V typical) thresholds respectively. Therefore, the  $V_{CC}$  never drops below  $V_{CC2(latch)}$  after powering up unless the circuit is unplugged (i.e.,  $V_{bulk}$  disappears or smaller than its minimum required operating threshold  $V_{start(min)}$  (20 V typical)). This feature makes the controller memorize the external latch off function in Pin 3.

This in–chip startup circuit can minimize the number of external components and Printed Circuit Board (PCB) area. It also minimizes the loss due to startup resistor because startup resistor always dissipates power but this startup circuit can be turned off when the  $V_{CC}$  voltage is sufficient. Actually, there is a small leakage current  $I_{HV3}$  (30  $\mu A$  typical at HV = 700~V) when the startup circuit is off.

The  $V_{CC}$  capacitor is recommended to be at least 47  $\mu F$  to ensure that  $V_{CC}$  is always above the minimum operating voltage  $V_{CC2(off)}$  (7.7 V typical) in the startup phase. For example, the PWM die consumes  $I_{CC2(op2)}$  (2.2 mA typical), a 47  $\mu F$   $V_{CC}$  capacitor can maintain the  $V_{CC}$  above 7.7 V for 105 ms. It is the available time to establish a  $V_{CC}$  voltage from the flyback transformer auxiliary winding.

$$t_{Startup} = \frac{CVCC\Delta V}{ICC2(op2)} = \frac{47 \ \mu F \cdot (12.6 \ V - 7.7 \ V)}{2.2 \ mA} = 105 \ ms$$

(eq. 1)

The PFC section does not consume any current in the startup phase since  $V_{aux}$  is disabled initially (i.e.,  $V_{aux} = V_{CC1} = 0$  V).

When  $V_{CC2}$  falls below  $V_{CC2(off)}$  (7.7 V typical) for whatever reason, the PWM section sleeps and it consumes  $I_{CC2(latch)}$  (680  $\mu A$  typical) until  $V_{CC2}$  reaches  $V_{CC2(latch)}$  (5.6 V typical). When  $V_{CC2}$  reaches  $V_{CC2(latch)}$  (5.6 V typical), the startup current source activates and  $V_{CC2}$  rises again.

#### Auxiliary Supply Vaux

The  $V_{aux}$  pin (Pin 1) connects to the  $V_{CC1}$  pin (Pin 8) externally. Internally, the  $V_{aux}$  pin is connected to  $V_{CC2}$  through an internal MOSFET. The MOSFET on–resistance is  $R_{aux}$  (11.7  $\Omega$  typical). It delivers a supply voltage from the PWM section to the PFC section. The  $V_{aux}$  is disabled when one of the following conditions occurs.

- V<sub>aux</sub> is initially disabled because of no feedback signal (V<sub>FB2</sub> > 3.0 V) initially.

- 2. Fault condition ( $V_{FB2} > 3.0 \text{ V}$  for more than 125 ms).

- 3. Standby condition ( $V_{FB2} < V_{stby}$  (0.75 V typical) and then  $V_{FB2} < V_{stby-out}$  (1.25 V typical) for more than 125 ms).

- 4. Insufficient operating supply voltage (V<sub>CC2</sub> < V<sub>CC2(off)</sub> (7.7 V typical)).

- 5. Overvoltage protection (OVP) latch activated from CS2 pin (Pin 3) ( $V_{CS2} > V_{OVP}$  (3.0 V typical)).

- Thermal shutdown latch in the PWM section activated when the junction temperature is over typical 150°C.

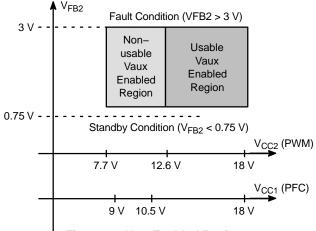

Figure 49. Vaux Enabled Regions

The UVLO start thresholds of  $V_{CC1}$  is  $V_{CC1(on)}$  (10.5 V typical) and the maximum allowable limit is 18 V. On the other hand, the  $V_{aux}$  is enabled when  $V_{CC2}$  is over  $V_{CC2(off)}$  (7.7 V typical). Hence, there are two possible operating regions in Figure 49. In the non–usable region the  $V_{aux}$  is not high enough to turn on the PFC section. **Therefore, the flyback transformer auxiliary winding must be between**  $V_{CC1(on)}$  (10.5 V typical) and 18 V.

#### **Regulation in the PWM Section**

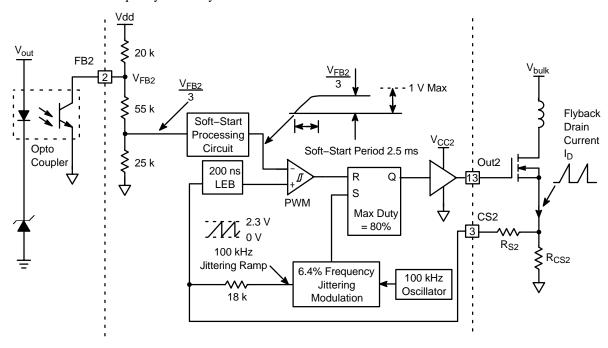

The PWM section (or second stage) of the NCP1603 is a current-mode fixed-frequency PWM flyback controller

with internal compensation ramp. The simplified block diagram of the duty cycle regulation section is in Figure 50. A 100 kHz clock oscillator is modulated by adding a frequency jittering feature. This modulated 100 kHz clock signal turns the output Out2 (pin 13) high in each switching cycle. The output goes low when the current–loop feedback signal intersects with the output voltage–loop feedback signal. A duty cycle is therefore generated. The maximum duty ratio is limited to  $D_{max}$  (80% typical).

Figure 50. Block Diagram of Duty Cycle Regulation in the PWM Section

The current–loop feedback circuit consists of a typical 200 ns Leading Edge Blanking (LEB) that is to prevent a premature reset of the output due to noise, a pair of sense resistors  $R_{\rm CS2}$  and  $R_{\rm S2}$  that sense the flyback drain current  $I_{\rm D}$ , and a 0–to–2.3 V jittering ramp that adds a ramp compensation for a stability improvement to the current–mode control in continuous mode operation.

The  $V_{FB2}$  is approximately divided by 3 by an internal pair of resistors (55 k $\Omega$  and 25 k $\Omega$ ). The soft–start processing circuit reduces the initial voltage–loop feedback signal ( $V_{FB2}$  / 3) for 2.5 ms. After this 2.5 ms, the soft–start disappears. As a result, the startup envelope of the peak drain current ramps up gradually for 2.5 ms.

Excessive output voltage causes more the optocoupler current. It pulls down the  $V_{FB2}$  through FB2 pin (Pin 2) and generates a lower duty ratio. The output voltage reduces. Insufficient output voltage reduces the optocoupler current. If the current is too small, the  $V_{FB2}$  is eventually pulled high than 3.0 V (3.8 V typical). The ( $V_{FB2}$ /3) signal

is then clamped to an internal 1.0 V limit. If the ramp is ignored (i.e.,  $R_{S2} = 0$ ), the maximum possible drain current is derived as:

$$I_{D(max)} = \frac{1 \text{ V}}{R_{CS2}}$$

(eq. 2)

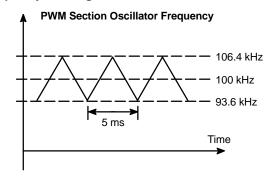

#### **Frequency Jittering**

Figure 51. Frequency Jittering of PWM Oscillator

Frequency jittering is a method used to soften the EMI signature by spreading the energy in the vicinity of the main switching component. The PWM Section offers a typical  $\pm 6.4\%$  deviation on the nominal switching frequency (100 kHz typical). A sweep sawtooth modulates the 100 kHz clock up and down with a 5.0 ms period. Figure 51 illustrates the  $\pm 6.4\%$  variation of the jittering oscillator frequency versus time.

#### $V_{FB2}$ Start Vaux 55 k $V_{FB2}$ Enable Vaux/PFC 125 ms Delay $v_{\rm SS}$ 25 k Fault Disable Vaux/PFC Soft-Star and Out2 1 V Max Soft-Start Period 2.5 ms

#### **Fault Condition**

Figure 52 illustrates the fault detection circuitry and its timing diagram. When fault (or output short circuit) happens, the output voltage collapses and the optocoupler is opened.  $V_{FB2}$  is internally pulled to be higher than 3.0 V (3.8 V typical). Then, the controller activates an error flag when  $(V_{FB2}/3)$  is greater than the soft–start voltage  $V_{SS}$  that is 1.0 V in steady state.

Figure 52. Block Diagram and Timing Diagram of Fault Detection

When the circuit is powering up in the beginning, the output voltage is not yet established and FB2 pin (Pin 2) is opened. Therefore, there is a 125 ms timer to allow the circuit to establish an initial output voltage. Then, a fault (or short circuit) condition is recognized when an error flag

$(V_{FB2} \ge 3.0 \text{ V})$  can last for 125 ms. When a fault is detected, Out2 pin (Pin 13) goes low. The power supply stops delivering power to the output. On the other hand, the  $V_{aux}$  (=  $V_{CC1}$ ) also goes low. The  $V_{aux}$  will restore immediately when the error flag disappears.

Figure 53. Timing Diagram of Fault Condition

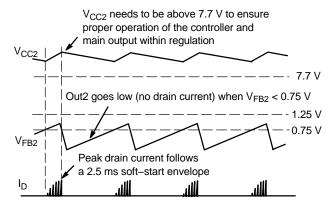

Figure 53 illustrates the timing diagram of  $V_{CC2}$  and the second–stage drain current  $I_D$  in fault condition. The  $V_{CC}$  drops because output voltage collapses. When  $V_{CC}$  drops below  $V_{CC(off)}$  (7.7 V typical), the Drive Output signal disappears and the  $V_{CC}$  continues to drop. When bias voltage  $V_{CC}$  drops to  $V_{CC(latch)}$  (5.6 V typical), the startup current source activates and charge up the  $V_{CC}$  until  $V_{CC}$  reaches  $V_{CC(on)}$  (12.6 V typical). The internal 2.5 ms soft–start activates after  $V_{CC}$  reaches  $V_{CC(on)}$  (12.6 V typical). The peak drain current follows its 2.5 ms envelope. The power supply dissipates some power due to the switching signal of Out2.

As shown in Figure 53, NCP1603 has a "double hiccup" feature that allows the drain current in every two  $V_{\rm CC}$  hiccup cycle in fault condition. The "double hiccup" feature offers fewer power dissipation and allows longer fault clearance time comparing to "single hiccup".

If the fault is cleared ( $V_{FB2}$  < 3.0  $V_{SS}$ ) and  $V_{CC}$  remains above  $V_{CC2(off)}$  (7.7 V typical), the circuit will resume its operation. Otherwise, the  $V_{CC}$  will continue this 12.6–7.7–5.6–12.6 V hiccup mode until the fault or bulk voltage is cleared.

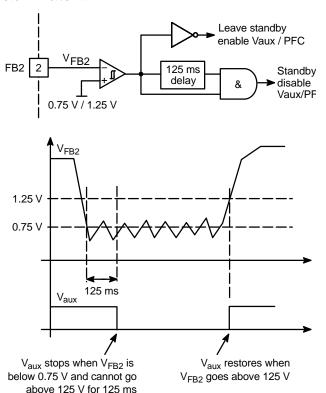

#### **PWM Operation in Standby Condition**

The output voltage rises up excessively in standby condition and the  $V_{FB2}$  drops. A set point of 25% of the maximum of  $V_{FB2}$  (i.e., 3.0 V) is defined to be the standby threshold. Hence, the standby threshold is  $V_{stby} = 25\% \times 3.0 \ V = 0.75 \ V$ .

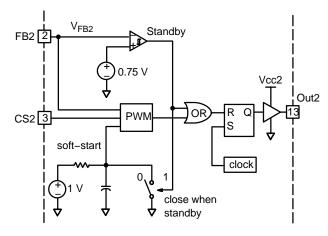

Figure 54. Block Diagram and Timing Diagram of Standby Detection

Figure 54 illustrates the standby detection circuitry and its timing diagram. When standby condition happens (i.e.,  $V_{FB2} < 0.75 \text{ V}$ ), the controller will wait for a typical 125 ms to ensure that the output power remains low for a while. Then, the  $V_{aux}$  is disabled to shut down the PFC section. The  $V_{aux}$  (or the PFC) restores when  $V_{FB2}$  goes above 1.25 V immediately because  $V_{FB2}$  can be possibly above or below the 0.75 V threshold during standby operation (referring to Figure 55 in the next section) and the PFC section needs to resume duty when  $V_{FB2}$  goes higher (i.e., output power becomes higher).

#### **PWM Soft Skip Mode Standby Operation**

Figure 55. Timing Diagram in Standby Condition

Figure 56. Block Diagram in Standby Operation

Figure 55 and 56 show the timing diagram and block diagram of the standby operation respectively. A skipping cycle behavior of the drain current is made by reset the latch whenever  $V_{FB2}$  is smaller than 0.75 V. When  $V_{FB2}$  is greater than 0.75 V, the duty ratio is modulated by the PWM block that is illustrated in Figure 50. The soft–start circuit is reset when  $V_{FB2}$  goes below 0.75 V and the drain current follows the 2.5 ms soft–start envelope every time when  $V_{FB2}$  is above 0.75 V again. This soft–start envelope drain current is called "Soft Skip Mode" Standby. It can reduce the low–frequency audible noise because the peaks of the drain current are reduced.

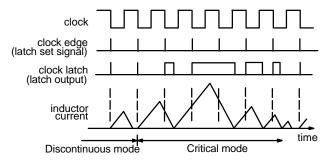

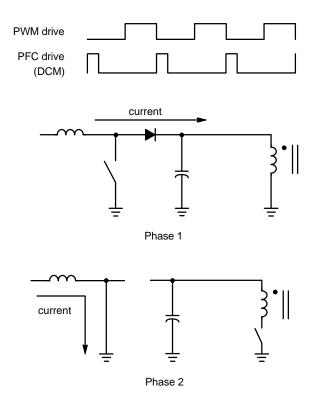

#### PFC in Discontinuous/Critical Mode

The PFC section of the NCP1603 is a PFC driver designed for low–power PFC boost circuit in DCM or CRM and takes advantages on both operating modes. DCM limits the maximum switching frequency. It simplifies the front–ended EMI filter design. CRM limits the maximum currents of diode, MOSFET and inductor. It reduces the costs and improves the reliability of the circuit. This device substantially exhibits unity power factor while operating in DCM and CRM. It minimizes the number of external components.

The PFC section primarily designed to operate in fixed-frequency DCM. In the most stressful conditions, CRM can be an alternative option that is without power factor degradation. On the other hand, the PFC section can be viewed as a CRM controller with a frequency clamp (maximum switching frequency limit) alternative option that is also without power factor degradation. In summary, the PFC section can cover both CRM and DCM without power factor degradation. Based on the selections of the boost inductor and the oscillator frequency, the circuit is capable of the following three applications.

- 1. "Mostly in CRM" with a frequency clamp set by the oscillator or synchronization frequency.

- 2. "Mostly in fixed-frequency mode DCM" and only run in CRM at high load and low line.

- 3. "Fixed-frequency DCM" only.

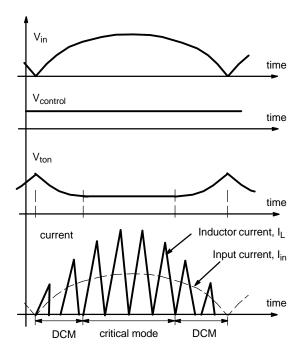

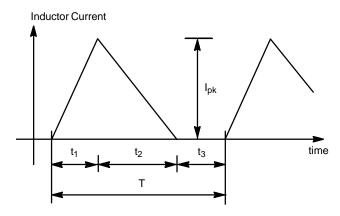

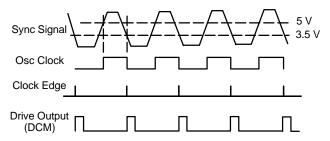

Figure 57. Timing Diagram of the PFC Stage

DCM needs higher peak inductor current comparing to CRM in the same averaged input current. Hence, CRM is generally preferred at around the sinusoidal peak for lower the maximum current stress but DCM is also preferred at the non-peak region to avoid excessive switching frequencies. Because of the variable-frequency feature of the CRM and constant-frequency feature of DCM, switching frequency is the maximum in the DCM region and hence the minimum switching frequency will be found at the moment of the sinusoidal peak.

#### **DCM PFC Circuit**

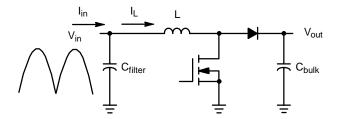

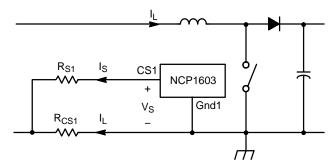

A DCM/CRM PFC boost converter is shown in Figure 58. Input voltage is a rectified 50 or 60 Hz sinusoidal signal. The MOSFET is switching at a high frequency (typically around  $100~\rm kHz$ ) so that the inductor current  $I_L$  basically consists of high–frequency and low–frequency components.

Figure 58. DCM/CRM PFC Boost Converter

Filter capacitor  $C_{\rm filter}$  is an essential and very small value capacitor in order to eliminate the high–frequency content of the DCM inductor current  $I_L$ . This filter capacitor cannot be too bulky because it can pollute the power factor by distorting of the rectified sinusoidal input voltage.

#### PFC Methodology

The PFC section uses a proprietary PFC methodology particularly designed for both DCM and CRM operation. The PFC methodology is described in this section.

Figure 59. Inductor Current in DCM

As shown in Figure 59, the inductor current  $I_L$  of each switching cycle starts from zero in DCM. CRM is a special case of DCM when  $t_3 = 0$ . When the PFC boost converter MOSFET is on, the inductor current  $I_L$  increases from zero to  $I_{pk}$  for a time duration  $t_1$  with inductance L and input voltage  $V_{in}$ . Equation 3 is formulated.

$$V_{in} = L \frac{lpk}{t_1}$$

(eq. 3)

The input filter capacitor  $C_{\rm filter}$  and the front-ended EMI filter absorb the high-frequency component of inductor current. It makes the input current  $I_{\rm in}$  a low-frequency signal.

$$I_{in} = \frac{I_{pk} (t_1 + t_2)}{2 T}$$

for DCM (eq. 4)

$$I_{in} = \frac{I_{pk}}{2}$$

for CRM (eq. 5)

From Equations 3, 4, and 5, the input impedance  $Z_{\text{in}}$  is formulated.

$$Z_{in} = \frac{V_{in}}{I_{in}} = \frac{2TL}{t_1(t_1 + t_2)}$$

for DCM (eq. 6)

$$Z_{in} = \frac{V_{in}}{I_{in}} = \frac{2L}{t_1} \quad \text{for CRM} \qquad \qquad (\text{eq. 7})$$

Power factor is corrected when the input impedance  $Z_{in}$  in Equations 6 and 7 are constant or slowly varying.

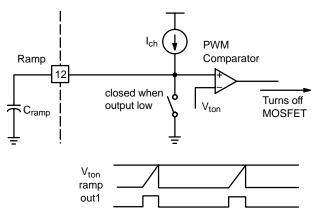

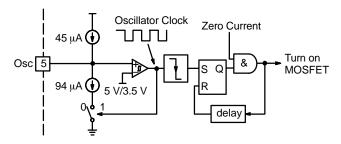

Figure 60. PFC Modulation Circuit and Timing Diagram

The MOSFET on time  $t_1$  of PFC modulation duty is generated by a feedback signal  $V_{ton}$  and a ramp. The PFC modulation circuit and timing diagram are shown in Figure 60. A relationship in Equation 8 is obtained.

$$t_1 = \frac{C_{ramp} V_{ton}}{I_{ch}}$$

(eq. 8)

The charging current  $I_{ch}$  is constant 100  $\mu A$  current and the ramp capacitor  $C_{ramp}$  is constant for a particular design.

Hence, according to Equation 8, the MOSFET on time  $t_1$  is proportional to  $V_{ton}$ .

In order to protect the PFC modulation comparator, the maximum voltage of  $V_{ton}$  is limited to internal clamp  $V_{ton(max)}$  (3.9 V typical) and the ramp pin (Pin 12) is with a 9.0 V ESD zener diode. The 3.9 V maximum limit of this  $V_{ton}$  indirectly limits the maximum on time.

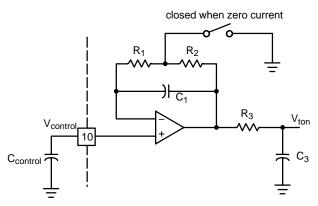

The  $V_{control}$  processing circuit generates  $V_{ton}$  from control voltage  $V_{control}$  and time information of zero inductor current. The circuit in Figure 61 makes Equations 9 and 10 where the value of resistor  $R_1$  is much higher than the value of resistor  $R_2$  ( $R_1 >> R_2$ ).

Figure 61. V<sub>control</sub> Processing Circuit

$$V_{ton} = \frac{T V_{control}}{t_1 + t_2}$$

for DCM (eq. 9)

$$V_{ton} = V_{control}$$

for CRM (eq. 10)

It is noted that  $V_{ton}$  is always greater than or equal to  $V_{control}$  ( $V_{ton} \ge V_{control}$ ).

In summary, the input impedance  $Z_{in}$  in Equation 11 is obtained from Equations 3 through 10.

$$Z_{in} = \frac{V_{in}}{I_{in}} = \frac{2LI_{ch}}{C_{ramp} V_{control}}$$

(eq. 11)

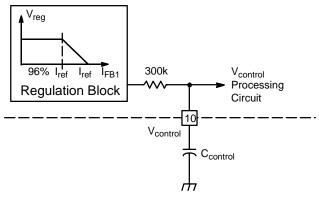

Control voltage  $V_{control}$  comes from the PFC boost circuit output voltage (i.e., bulk voltage  $V_{bulk}$ ) that is a slowly varying signal. The bandwidth of  $V_{control}$  can be additionally limited by inserting an external capacitor  $C_{control}$  to the  $V_{control}$  pin (Pin 10) in Figure 62. The internal 300 k $\Omega$  resistor and the capacitor  $C_{control}$  create a low–pass filter that has a bandwidth  $f_{control}$  in Equation 12. It is generally recommended to limit the bandwidth below 20 Hz to achieve power factor correction. Typical value of  $C_{control}$  is 0.1  $\mu$ F.

$$C_{control} > \frac{1}{2\pi 300 k\Omega} f_{control}$$

(eq. 12)

Figure 62. V<sub>control</sub> Low-Pass Filtering

If the bandwidth of V<sub>control</sub> is much less than the 50 or 60 Hz line frequency, the input impedance Zin is slowly varying or roughly constant. Then, the power factor correction is achieved in DCM and CRM.

#### **Maximum Power in PFC Section**

Input and output power (Pin and Pout) are derived in Equations 13 and 14 when the circuit efficiency  $\eta$  is obtained or assumed. The variable Vac stands for the RMS input voltage.

$$P_{in} = \frac{V_{ac}^2}{Z_{in}} = \frac{V_{ac}^2 C_{ramp} V_{control}}{2 L I_{ch}}$$

(eq. 13)

$$P_{out} = \eta P_{in} = \frac{\eta V_{ac}^{2} C_{ramp} V_{control}}{2 L I_{ch}}$$

(eq. 14)

From Equations 13 and 14, control voltage V<sub>control</sub> controls the amount of output power, input power, or input impedance. The maximum value of the control voltage  $V_{control}$  is 1.05 V (i.e.,  $V_{control(max)} = 1.05$  V). A parameter called maximum power resistor  $R_{power}$  (10.5 k $\Omega$  typical) is defined in Equation 18 and restricted to have a maximum  $\pm 10\%$  variation (i.e., 9.5 k $\Omega \leq R_{power} \leq 11.5 k\Omega$ ) for defining the maximum power in an application.

$$R_{power} = \frac{V_{control(max)}}{I_{ch}} = \frac{1.05 \text{ V}}{100 \text{ } \mu\text{A}} = 10.5 \text{ k}\Omega \qquad \text{(eq. 15)}$$

It means that the maximum input and output power  $(P_{in(max)})$  and  $P_{out(max)}$  are limited to  $\pm 10\%$  variation.

$$P_{in(max)} = \frac{V_{ac}^{2}C_{ramp}R_{power}}{2L}$$

(eq. 16)

$$P_{out(max)} = \frac{\eta V_{ac}^{2}C_{ramp}R_{power}}{2L}$$

(eq. 17)

$$P_{out(max)} = \frac{\eta V_{ac}^{2}C_{ramp}R_{power}}{2 L}$$

(eq. 17)

The maximum input current  $I_{ac(max)}$  to deliver the maximum input power P<sub>in(max)</sub> is also derived in (eq.14). The suffix ac stands for RMS value.

$$I_{ac(max)} = \frac{Pin(max)}{V_{ac}} = \frac{V_{ac}C_{ramp}R_{power}}{2 L}$$

(eq. 18

#### Feedback in PFC Section

The output voltage of the PFC circuit (i.e., bulk voltage V<sub>bulk</sub>) is sensed as a feedback current I<sub>FB1</sub> flowing into the FB1 pin (Pin 9) of NCP1603. The FB1 pin voltage V<sub>FB1</sub> is typically smaller than 5.0 V referring to Figure 31. It is much lower than V<sub>bulk</sub> that is typically 400 V. Therefore, V<sub>FB1</sub> is generally neglected.

$$I_{FB1} = \frac{V_{bulk} - V_{FB1}}{R_{FB1}} \approx \frac{V_{bulk}}{R_{FB1}}$$

(eq. 19)

where R<sub>FB1</sub> is the feedback resistor connected the FB1 pin (Pin 9) and the output voltage referring to Figure 45.

Then, the feedback current I<sub>FB1</sub> represents the bulk voltage V<sub>bulk</sub> and will be used in the PFC section voltage regulation, undervoltage protection (UVP), overvoltage protection (OVP).

#### **Bulk Voltage Regulation in PFC Section**

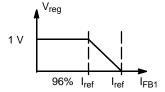

PFC-stage feedback current I<sub>FB1</sub>, that presents bulk voltage V<sub>bulk</sub> or the PFC-stage output voltage, is regulated with a reference current ( $I_{ref} = 200 \mu A$  typical) as shown in Figure 63. When I<sub>FB1</sub> is lower than 96% of I<sub>ref</sub>, the V<sub>reg</sub> that is the output of the regulation block is as high as V<sub>control(max)</sub> (1.05 V typical) that it gives the maximum value on Vton and the maximum MOSFET on time and V<sub>bulk</sub> increases. When I<sub>FB1</sub> is higher than I<sub>ref</sub>, the V<sub>reg</sub> becomes 0 V that gives no MOSFET on time and V<sub>bulk</sub> decreases. As a result, the bulk voltage V<sub>bulk</sub> is regulated around the range between 96% and 100% of the nominal value of  $R_{FB1} \times I_{ref}$ .

Figure 63. Regulation Block