2 MHz Dual 2A Integrated Switch Buck Regulator

## **General Description**

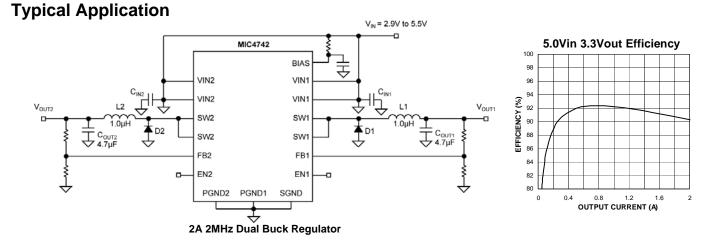

The Micrel MIC4742 is a high efficiency dual PWM buck (step-down) regulator that provides dual 2A current output. The MIC4742 operates at 2MHz. A proprietary internal compensation technique allows a closed loop bandwidth of over 200kHz.

The low on-resistance internal p-channel MOSFET of the MIC4742 allows efficiencies over 92%, reduces external components count and eliminates the need for an expensive current sense resistor.

The MIC4742 operates from 2.9V to 5.5V input and the output can be adjusted down to 0.6V. The device can operate with a maximum duty cycle of 100% for use in low-dropout conditions.

The MIC4742 is available in the exposed pad 16-pin  $3mm \times 3mm \text{ MLF}^{\textcircled{B}}$  and ETSSOP-16 packages with a junction operating range from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

All support documentation can be found on Micrel's web site at: www.micrel.com.

### Features

- 2.9 to 5.5V supply voltage

- 2MHz PWM mode

- 2A Dual output

- Greater than 92% efficiency

- 100% maximum duty cycle

- Adjustable output voltage option down to 0.6V

- Ultra-fast transient response

- Ultra-small external components Stable with a 1µH inductor and a 4.7µF output capacitor

- Fully integrated 2A MOSFET switches

- Micro-power shutdown

- Thermal shutdown and current limit protection

- Available in a 3mm x 3mm 16-pin  $\text{MLF}^{\textcircled{\text{B}}}$  and 16-pin ETSSOP

- –40°C to +125°C junction temperature range

### Applications

- Broadband: xDSL modems

- Automotive satellite radios

- HD STB, DVD/TV recorder

- Computer peripherals: printers and graphic cards

- FPGA/ASIC

- General point of load

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## **Ordering Information**

| Part Number | er Voltage Junction Temp. Range Package |                | Lead Finish                 |         |

|-------------|-----------------------------------------|----------------|-----------------------------|---------|

| MIC4742YML  | Adj.                                    | –40° to +125°C | 16-Pin 3x3 MLF <sup>®</sup> | Pb-Free |

| MIC4742YTSE | Adj.                                    | –40° to +125°C | 16-Pin EPAD TSSOP           | Pb-Free |

Note:

MLF® is a GREEN RoHS-compliant package. Lead finish is NiPdAu. Mold compound is Halogen Free.

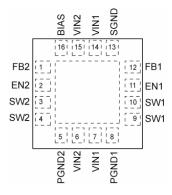

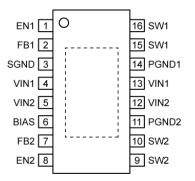

# **Pin Configuration**

16-Pin 3mm x 3mm MLF<sup>®</sup> (YML)

16-Pin ETSSOP (YTSE)

# **Pin Description**

| ite current draw to less than 5µA (both EN1 and EN2 are low).     3,4   9,10   SW2   Switch for output 2 (Output): Internal power P-Channel MOSFET output switch     5   11   PGND2   Power Ground for output 2. Provides the ground return path for the high-side drive current.     6,15   5,12   VIN2   Supply Voltage for output 2 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND.     7,14   4,13   VIN1   Supply Voltage for output 1 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND.     8   14   PGND1   Power Ground for output 1. Provides the ground return path for the high-side drive current.     9,10   15,16   SW1   Switch for output 2 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Number<br>(MLF <sup>®</sup> ) | Pin Number<br>(EPAD-TSSOP) | Pin Name | Pin Function                                                                                                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   0   End of the current draw to less than 5µA (both EN1 and EN2 are low).     3,4   9,10   SW2   Switch for output 2 (Output): Internal power P-Channel MOSFET output switcl for output 2.     5   11   PGND2   Power Ground for output 2. Provides the ground return path for the high-side drive current.     6,15   5,12   VIN2   Supply Voltage for output 2 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND. VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.     7,14   4,13   VIN1   Supply Voltage for output 1 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND. VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.     8   14   PGND1   Power Ground for output 1. Provides the ground return path for the high-side drive current. PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.     9,10   15,16   SW1   Switch for output 1. Provides the ground return path for the high-side drive current. PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.     9,10   15,16   SW1   Switch for output 1. Provides the ground return path for the high-side drive current. PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.     11 <sup>(11)</sup> 1 <sup>(11)</sup> EN1 | 1                                 | 7                          | FB2      |                                                                                                                                                     |  |

| 5 11 PGND2 Power Ground for output 2. Provides the ground return path for the high-side drive current.   5 11 PGND2 Power Ground for output 2. Provides the ground return path for the high-side drive current.   6,15 5,12 VIN2 Supply Voltage for output 2 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND.   7,14 4,13 VIN1 Supply Voltage for output 1 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND.   7,14 4,13 VIN1 Supply Voltage for output 1 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND.   8 14 PGND1 Power Ground for output 1. Provides the ground return path for the high-side drive current.   9,10 15,16 SW1 Switch for output 1 (Output): Internal power P-Channel MOSFET output switcl   11 <sup>(1)</sup> 1 <sup>(1)</sup> EN1 Enable for output 1 (Input). Logic level low, will shutdown the device, reducing the current draw to less than 5µA (both EN1 and EN2 are low).   12 2 FB1 Feedback for output 1 (Input). Input to the error amplifier, connect to the external resistor divider network to set the output voltage.   13 3 SGND Signal (Analog) Ground. Provides return path for control                                                                                                    | 2 <sup>(1)</sup>                  | 8 <sup>(1)</sup>           | EN2      | Enable for output 2 (Input). Logic level low, will shutdown the device, reducing the current draw to less than $5\mu A$ (both EN1 and EN2 are low). |  |

| drive current. PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.   6,15 5,12 VIN2 Supply Voltage for output 2 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND. VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.   7,14 4,13 VIN1 Supply Voltage for output 1 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND. VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.   8 14 PGND1 Power Ground for output 1. Provides the ground return path for the high-side drive current. PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.   9,10 15,16 SW1 Switch for output 1 (Input): Internal power P-Channel MOSFET output switch for output 1 (Input). Logic level low, will shutdown the device, reducing the current draw to less than 5µA (both EN1 and EN2 are low).   12 2 FB1 Feedback for output 1 (Input). Input to the error amplifier, connect to the external resistor divider network to set the output voltage.   13 3 SGND Signal (Analog) Ground. Provides return path for control circuitry and internal reference.   16 6 BIAS Internal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor to SGND. Biased through a 10Ω resistor to VIN.                                      | 3,4                               | 9,10                       | SW2      | Switch for output 2 (Output): Internal power P-Channel MOSFET output switch                                                                         |  |

| 6,155,12VIN2Supply Voltage for output 2 (Input): Supply voltage for the source of the<br>internal P-channel MOSFET and driver. Requires bypass capacitor to GND.<br>VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.7,144,13VIN1Supply Voltage for output 1 (Input): Supply voltage for the source of the<br>internal P-channel MOSFET and driver. Requires bypass capacitor to GND.<br>VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.814PGND1Power Ground for output 1. Provides the ground return path for the<br>high-side drive current.<br>PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.9,1015,16SW1Switch for output 1 (Output): Internal power P-Channel MOSFET output switch<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                 | 11                         | PGND2    |                                                                                                                                                     |  |

| internal P-channel MOSFET and driver. Requires bypass capacitor to GND.<br>VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.7,144,13VIN1Supply Voltage for output 1 (Input): Supply voltage for the source of the<br>internal P-channel MOSFET and driver. Requires bypass capacitor to GND.<br>VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.814PGND1Power Ground for output 1. Provides the ground return path for the<br>high-side drive current.<br>PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.9,1015,16SW1Switch for output 1 (Output): Internal power P-Channel MOSFET output switch<br>11 <sup>(1)</sup> 11 <sup>(1)</sup> 1 <sup>(1)</sup> EN1Enable for output 1 (Input). Logic level low, will shutdown the device, reducing<br>the current draw to less than 5µA (both EN1 and EN2 are low).122FB1Feedback for output 1 (Input). Input to the error amplifier, connect to the<br>external resistor divider network to set the output voltage.133SGNDSignal (Analog) Ground. Provides return path for control circuitry and internal<br>reference.166BIASInternal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor<br>to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                |                                   |                            |          | PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.                                                                           |  |

| 7,14 4,13 VIN1 Supply Voltage for output 1 (Input): Supply voltage for the source of the internal P-channel MOSFET and driver. Requires bypass capacitor to GND. VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.   8 14 PGND1 Power Ground for output 1. Provides the ground return path for the high-side drive current. PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.   9,10 15,16 SW1 Switch for output 1 (Output): Internal power P-Channel MOSFET output switch 11 <sup>(1)</sup> 11 <sup>(1)</sup> 1 <sup>(1)</sup> EN1 Enable for output 1 (Input). Logic level low, will shutdown the device, reducing the current draw to less than 5µA (both EN1 and EN2 are low).   12 2 FB1 Feedback for output 1 (Input). Input to the error amplifier, connect to the external resistor divider network to set the output voltage.   13 3 SGND Signal (Analog) Ground. Provides return path for control circuitry and internal reference.   16 6 BIAS Internal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                             | 6,15                              | 5,12                       | VIN2     |                                                                                                                                                     |  |

| internal P-channel MOSFET and driver. Requires bypass capacitor to GND.<br>VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.814PGND1Power Ground for output 1. Provides the ground return path for the<br>high-side drive current.<br>PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.9,1015,16SW1Switch for output 1 (Output): Internal power P-Channel MOSFET output switch<br>11 <sup>(1)</sup> 11 <sup>(1)</sup> 1 <sup>(1)</sup> EN1Enable for output 1 (Input). Logic level low, will shutdown the device, reducing<br>the current draw to less than 5µA (both EN1 and EN2 are low).122FB1Feedback for output 1 (Input). Input to the error amplifier, connect to the<br>external resistor divider network to set the output voltage.133SGNDSignal (Analog) Ground. Provides return path for control circuitry and internal<br>reference.166BIASInternal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor<br>to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                            |          | VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.                                                                           |  |

| 8 14 PGND1 Power Ground for output 1. Provides the ground return path for the high-side drive current.<br>PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.   9,10 15,16 SW1 Switch for output 1 (Output): Internal power P-Channel MOSFET output switch to routput 1 (Input). Logic level low, will shutdown the device, reducing the current draw to less than 5µA (both EN1 and EN2 are low).   12 2 FB1 Feedback for output 1 (Input). Input to the error amplifier, connect to the external resistor divider network to set the output voltage.   13 3 SGND Signal (Analog) Ground. Provides return path for control circuitry and internal reference.   16 6 BIAS Internal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7,14                              | 4,13                       | VIN1     |                                                                                                                                                     |  |

| high-side drive current.<br>PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.9,1015,16SW1Switch for output 1 (Output): Internal power P-Channel MOSFET output switch<br>the current draw to less than 5µA (both EN1 and EN2 are low).111(1)EN1Enable for output 1 (Input). Logic level low, will shutdown the device, reducing<br>the current draw to less than 5µA (both EN1 and EN2 are low).122FB1Feedback for output 1 (Input). Input to the error amplifier, connect to the<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |                            |          | VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes.                                                                           |  |

| 9,1015,16SW1Switch for output 1 (Output): Internal power P-Channel MOSFET output switch11(1)1(1)EN1Enable for output 1 (Input). Logic level low, will shutdown the device, reducing<br>the current draw to less than 5µA (both EN1 and EN2 are low).122FB1Feedback for output 1 (Input). Input to the error amplifier, connect to the<br>external resistor divider network to set the output voltage.133SGNDSignal (Analog) Ground. Provides return path for control circuitry and internal<br>reference.166BIASInternal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor<br>to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                 | 14                         | PGND1    |                                                                                                                                                     |  |

| 11(1)1(1)EN1Enable for output 1 (Input). Logic level low, will shutdown the device, reducing<br>the current draw to less than 5µA (both EN1 and EN2 are low).122FB1Feedback for output 1 (Input). Input to the error amplifier, connect to the<br>external resistor divider network to set the output voltage.133SGNDSignal (Analog) Ground. Provides return path for control circuitry and internal<br>reference.166BIASInternal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor<br>to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |                            |          | PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes.                                                                           |  |

| the current draw to less than 5µA (both EN1 and EN2 are low).   12 2 FB1 Feedback for output 1 (Input). Input to the error amplifier, connect to the external resistor divider network to set the output voltage.   13 3 SGND Signal (Analog) Ground. Provides return path for control circuitry and internal reference.   16 6 BIAS Internal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9,10                              | 15,16                      | SW1      | Switch for output 1 (Output): Internal power P-Channel MOSFET output switch                                                                         |  |

| 13 3 SGND Signal (Analog) Ground. Provides return path for control circuitry and internal reference.   16 6 BIAS Internal circuit bias supply. Must be bypassed with a 0.1µF ceramic capacitor to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 <sup>(1)</sup>                 | 1 <sup>(1)</sup>           | EN1      | Enable for output 1 (Input). Logic level low, will shutdown the device, reducing the current draw to less than $5\mu A$ (both EN1 and EN2 are low). |  |

| Internal circuit bias supply. Must be bypassed with a 0.1μF ceramic capacitor to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                | 2                          | FB1      |                                                                                                                                                     |  |

| to SGND. Biased through a 10Ω resistor to VIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                | 3                          | SGND     |                                                                                                                                                     |  |

| EP EP GND Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                | 6                          | BIAS     |                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EP                                | EP                         | GND      | Connect to ground.                                                                                                                                  |  |

Note:

1. Do not float Enable Input.

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>IN</sub> )                                          | 0.3V to +6V             |

|----------------------------------------------------------------------------|-------------------------|

| Output Switch Voltage (V <sub>SW1</sub> , V <sub>SW2</sub> )               |                         |

| Output Switch Current (I <sub>SW1</sub> , I <sub>SW2</sub> )               | Internally Limited      |

| Input Voltage (V <sub>EN</sub> ), (V <sub>FB</sub> ), (V <sub>BIAS</sub> ) | 0.3V to V <sub>IN</sub> |

| Storage Temperature (T <sub>s</sub> )                                      | 60°C to +150°C          |

| Junction Temperature                                                       | 150°C                   |

| ESD Rating <sup>(3)</sup>                                                  | 2KV                     |

# **Operating Ratings**<sup>(2)</sup>

| +2.9V to +5.5V        |

|-----------------------|

| 0V to V <sub>IN</sub> |

| –40°C to +125°C       |

|                       |

| 60°C/W                |

| 35°C/W                |

|                       |

# Electrical Characteristics<sup>(4)</sup>

$V_{IN} = V_{EN} = 3.6V; L = 1.0 \mu H; C_{OUT} = 4.7 \mu F; T_A = 25^{\circ}C, \text{ unless noted. Bold values indicate } -40^{\circ}C \leq T_J \leq +125^{\circ}C.$

| Parameter                       | Condition                                                 | Min   | Тур  | Max   | Units |

|---------------------------------|-----------------------------------------------------------|-------|------|-------|-------|

| Supply Voltage Range            |                                                           | 2.9   |      | 5.5   | V     |

| Under-Voltage Lockout Threshold | Turn-on                                                   | 2.45  | 2.6  | 2.7   | V     |

| UVLO Hysteresis                 |                                                           |       | 100  |       | mV    |

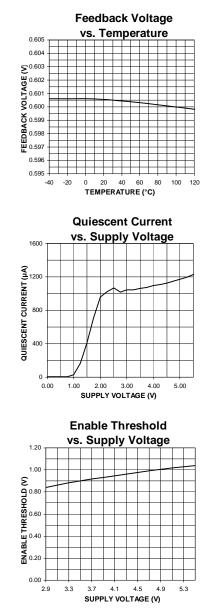

| Quiescent Current               | $V_{FB} = 0.9 * V_{NOM}$ (not switching); $V_{IN} = 5.5V$ |       | 1.4  | 3.0   | mA    |

|                                 | $V_{FB} = 0.9 * V_{NOM}$ (not switching); $V_{IN} = 3.6V$ |       | 1.0  |       | mA    |

| Shutdown Current                | $V_{EN} = 0V$                                             |       | 1.6  | 10    | μA    |

| [Adjustable] Feedback Voltage   | $\pm$ 2% (over temperature) I <sub>LOAD</sub> = 100µA     | 0.588 | 0.6  | 0.612 | V     |

| FB pin input current            |                                                           |       | 1    |       | nA    |

| Current Limit                   | $V_{FB} = 0.9 * V_{NOM}$                                  | 2.5   | 4.3  |       | А     |

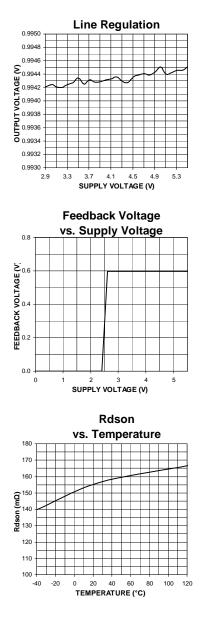

| Output Voltage Line Regulation  | $V_{IN}$ = 2.9V to 5.5V; $I_{LOAD}$ = 100 $\mu$ A         |       | 0.07 |       | %     |

| Output Voltage Load Regulation  | 20mA < I <sub>LOAD</sub> < 2A                             |       | 0.2  |       | %     |

| Maximum Duty Cycle              | $V_{FB} \le 0.9 * V_{NOM}$                                | 100   |      |       | %     |

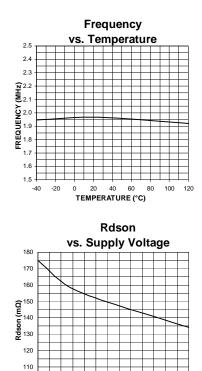

| Switch ON-Resistance            | I <sub>SW</sub> = 50mA V <sub>FB</sub> =GND               |       | 155  |       | mΩ    |

| Oscillator Frequency            |                                                           | 1.5   | 2    | 2.3   | MHz   |

| Switching Phase                 |                                                           |       | 180  |       | Deg   |

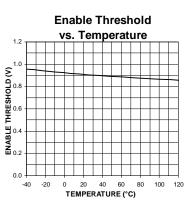

| Enable Threshold                |                                                           | 0.5   | 0.9  | 1.3   | V     |

| Enable Hysteresis               |                                                           |       | 55   |       | mV    |

| Enable Input Current            |                                                           |       | 0.1  | 2     | μA    |

| Over-Temperature Shutdown       |                                                           |       | 153  |       | °C    |

| Over-Temperature Hysteresis     |                                                           |       | 18   |       | °C    |

#### Notes:

1. Exceeding the absolute maximum rating may damage the device.

2. The device is not guaranteed to function outside its operating rating.

3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

4. Specification for packaged product only.

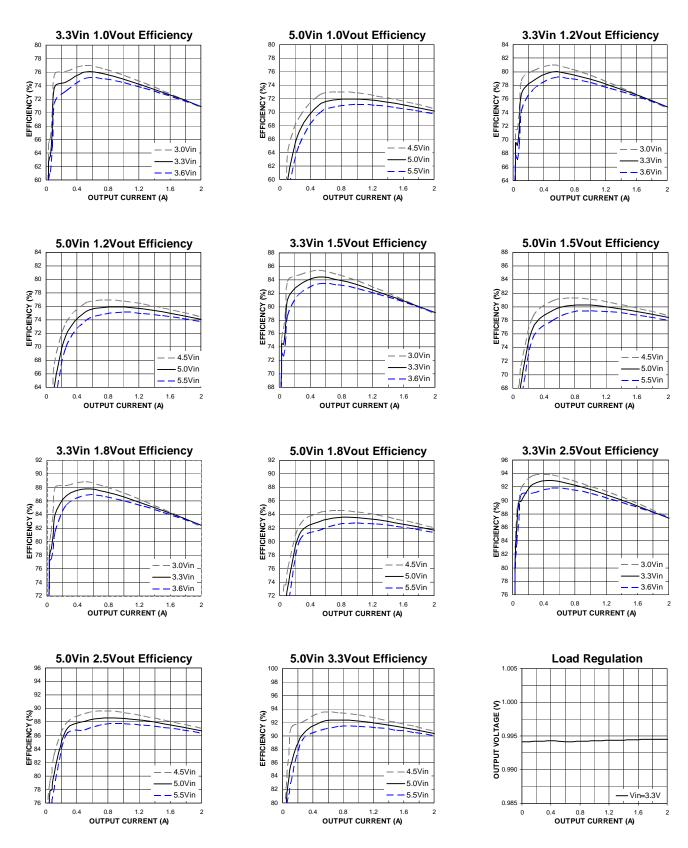

# **Typical Characteristics**

# Typical Characteristics (continue)

5.3

100

# **Functional Characteristics**

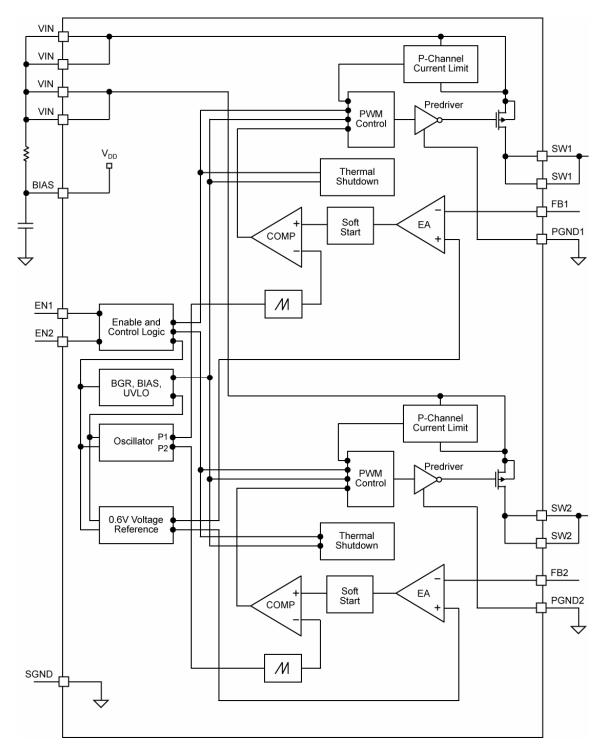

## **Functional Diagram**

MIC4742 Block Diagram

### VIN1/VIN2

VIN pins (two pins for VIN1 and two pins for VIN2) provide power to the source of the internal P-channel MOSFET along with the current limiting sensing. VIN1 pins and VIN2 pins are internally connected by anti-parallel diodes. The VIN operating voltage range is from 2.9V to 5.5V. Due to the high switching speeds, a  $10\mu$ F capacitor is recommended close to VIN and the power ground (PGND) for each pin for bypassing. Please refer to layout recommendations for more details.

### BIAS

The bias (BIAS) provides power to the internal reference and control sections of the MIC4742. A 10 $\Omega$  resistor from VIN to BIAS and a 0.1µF from BIAS to SGND are required for clean operation.

### EN1/EN2

The enable pins (EN1 and EN2) provides a logic level control of the outputs 1 and 2. In the off state, supply current of the device is greatly reduced (typically  $<2\mu$ A). Do not drive the enable pin above the supply voltage.

### FB1/FB2

The feedback pins (FB1 and FB2) provides the control path to control the outputs 1 and 2. A resistor divider connecting the feedback to the output is used to adjust the desired output voltage. The output voltage is calculated as follows:

$$V_{OUT} = V_{REF} \times \left(\frac{R1}{R2} + 1\right)$$

where  $V_{REF}$  is equal to 0.6V.

A feed-forward capacitor is recommended for most designs. To reduce current draw, 10K feedback resistors are recommended from the outputs to the FB pins (R1 in the equation). Also, feed-forward capacitors should be connected between the outputs and feedback pins (across R1). The large resistor value and the parasitic capacitance of the FB pin can cause a high frequency pole that can reduce the overall system phase margin. By placing a feed-forward capacitor, these effects can be significantly reduced. Feed-forward capacitance ( $C_{FF}$ ) can be calculated as follows:

$$C_{FF} = \frac{1}{2\pi \times R1 \times 200 kHz}$$

#### SW1/SW2

The switch pins (SW1 and SW2) connect directly to the inductor and provide the switching current necessary to operate in PWM mode. Due to the high speed switching on these pins, the switch nodes should be routed away from sensitive nodes. These pins also connect to the cathodes of the free-wheeling diodes.

### PGND1/PGND2

Power ground pins (PGND1 and PGND2) are the ground paths for the MOSFET drive current. PGND1 pin and PGND2 pin are internally connected by anti-parallel diodes. The current loop for the power ground should be as small as possible and separate from the Signal ground (SGND) loop. Refer to the layout recommendation for more details.

### SGND

Signal ground (SGND) is the ground path for the biasing and control circuitry. The current loop for the signal ground should be separate from the power ground (PGND) loop. Refer to the layout recommendation for more details.

# **Application Information**

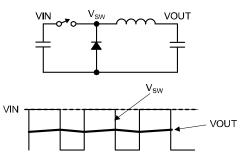

The MIC4742 is a dual 2A PWM non-synchronous buck regulator. By switching an input voltage supply, and filtering the switched voltage through an inductor and capacitor, a regulated DC voltage is obtained. Figure 1 shows a simplified example of a non-synchronous buck converter.

Figure 1. Example of Non-synchronous Buck Converter

For a non-synchronous buck converter, there are two modes of operation; continuous and discontinuous. Continuous or discontinuous refer to the inductor current. If current is continuously flowing through the inductor throughout the switching cycle, it is in continuous operation. If the inductor current drops to zero during the off time, it is in discontinuous operation. Critically continuous is the point where any decrease in output current will cause it to enter discontinuous operation. The critically continuous load current can be calculated as follows;

$$I_{OUT} = \frac{\left[V_{OUT} - \frac{V_{OUT}^2}{V_{IN}}\right]}{f_{SW} \times 2 \times L}$$

Continuous or discontinuous operation determines how we calculate peak inductor current.

#### **Continuous Operation**

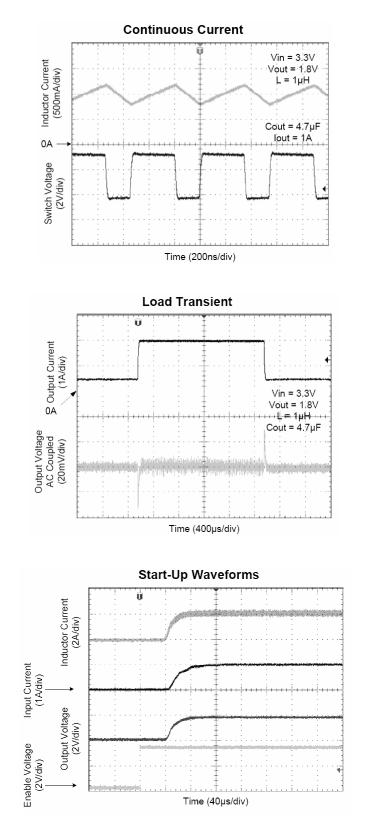

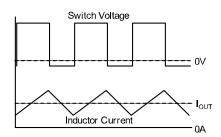

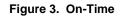

Figure 2 illustrates the switch voltage and inductor current during continuous operation.

Figure 2. Continuous Operation

The output voltage is regulated by pulse width modulating (PWM) the switch voltage to the average required output voltage. The switching can be broken up into two cycles; On and Off.

**During the On-Time,** Figure 3 illustrates the high side switch is turned on, current flows from the input supply through the inductor and to the output. The inductor current is charged at the rate;

To determine the total on-time, or time at which the inductor charges, the duty cycle needs to be calculated. The duty cycle can be calculated as;

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}}}$$

and the On time is;

$$T_{ON} = \frac{D}{f_{SW}}$$

Therefore, peak to peak ripple current is;

$$I_{pk-pk} = \frac{\left(V_{IN} - V_{OUT}\right) \times \frac{V_{OUT}}{V_{IN}}}{f_{sw} \times L}$$

Since the average peak to peak current is equal to the load current. The actual peak (or highest current the inductor will see in a steady-state condition) is equal to the output current plus  $\frac{1}{2}$  the peak-to-peak current.

$$I_{pk} = I_{OUT} + \frac{\left(V_{IN} - V_{OUT}\right) \times \frac{V_{OUT}}{V_{IN}}}{2 \times fsw \times L}$$

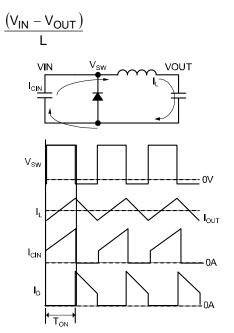

Figure 4 demonstrates the off-time. During the off-time, the high-side internal P-channel MOSFET turns off. Since the current in the inductor has to discharge, the current flows through the free-wheeling Schottky diode to the output. In this case, the inductor discharge rate is (where  $V_D$  is the diode forward voltage);

$$\frac{\left(V_{OUT} + V_{D}\right)}{L}$$

The total off time can be calculated as;

$$T_{OFF} = \frac{1 - D}{fsw}$$

Figure 4. Off-Time

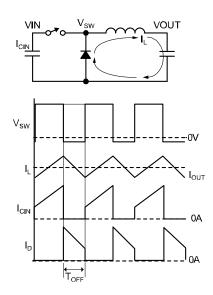

#### **Discontinuous Operation**

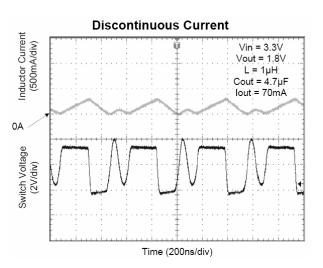

Discontinuous operation is when the inductor current discharges to zero during the off cycle. Figure 5 demonstrates the switch voltage and inductor currents during discontinuous operation.

Figure 5. Discontinuous Operation

When the inductor current (IL) has completely discharged, the voltage on the switch node rings at the frequency determined by the parasitic capacitance and the inductor value. In Figure 5, it is drawn as a DC voltage, but to see actual operation (with ringing) refer to the functional characteristics.

Discontinuous mode of operation has the advantage over full PWM in that at light loads, the MIC4742 will skip pulses as necessary, reducing gate drive losses, drastically improving light load efficiency.

### **Efficiency Considerations**

Calculating the efficiency is as simple as measuring power out and dividing it by the power in;

Efficiency =

$$\frac{P_{OUT}}{P_{IN}} \times 100$$

Where input power (P<sub>IN</sub>) is;

$$\mathsf{P}_{\mathsf{IN}} = \mathsf{V}_{\mathsf{IN}} \times \mathsf{I}_{\mathsf{IN}}$$

and output power (P<sub>OUT</sub>) is calculated as;

$$P_{OUT} = V_{OUT} \times I_{OUT}$$

The Efficiency of the MIC4742 is determined by several factors.

- Rdson (Internal P-channel Resistance)

- Diode conduction losses

- Inductor Conduction losses

- Switching losses

Rdson losses are caused by the current flowing through the high side P-channel MOSFET. The amount of power loss can be approximated by;

$$\mathsf{P}_{\mathsf{SW}} = \mathsf{R}_{\mathsf{DSON}} \times \mathsf{I}_{\mathsf{OUT}}^2 \times \mathsf{D}$$

Where D is the duty cycle.

Since the MIC4742 uses an internal P-channel MOSFET, Rdson losses are inversely proportional to supply voltage. Higher supply voltage yields a higher gate to source voltage, reducing the Rdson, reducing the MOSFET conduction losses. A graph showing typical Rdson vs input supply voltage can be found in the typical characteristics section of this datasheet.

Diode conduction losses occur due to the forward voltage drop ( $V_F$ ) and the output current. Diode power losses can be approximated as follows;

$$P_{D} = V_{F} \times I_{OUT} \times (1 - D)$$

For this reason, the Schottky diode is the rectifier of choice. Using the lowest forward voltage drop will help reduce diode conduction losses, and improve efficiency.

Duty cycle, or the ratio of output voltage to input voltage, determines whether the dominant factor in conduction losses will be the internal MOSFET or the Schottky diode. Higher duty cycles place the power losses on the high side switch, and lower duty cycles place the power losses on the Schottky diode.

Inductor conduction losses  $(P_L)$  can be calculated by multiplying the DC resistance (DCR) times the square of the output current;

$$P_L = DCR \times I_{OUT}^2$$

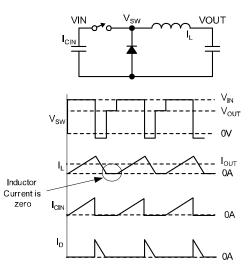

Also, be aware that there are additional core losses associated with switching current in an inductor. Since most inductor manufacturers do not give data on the type of material used, approximating core losses becomes very difficult, so verify inductor temperature rise. Switching losses occur twice each cycle, when the switch turns on and when the switch turns off. This is caused by a non-ideal world where switching transitions are not instantaneous, and neither are currents. Figure 6 demonstrates how switching losses due to the transitions dissipate power in the switch.

Figure 6. Switching Transition Losses

Normally, when the switch is on, the voltage across the switch is low (virtually zero) and the current through the switch is high. This equates to low power dissipation. When the switch is off, voltage across the switch is high and the current is zero, again with power dissipation being low. During the transitions, the voltage across the switch ( $V_{S-D}$ ) and the current through the switch ( $I_{S-D}$ ) are at middle, causing the transition to be the highest instantaneous power point. During continuous mode, these losses are the highest. Also, with higher load currents, these losses are higher. For discontinuous operation, the transition losses only occur during the "off" transition since the "on" transitions there is no current flow through the inductor.

## **Component Selection**

### **Input Capacitor**

A 10µF ceramic is recommended on each VIN pin for bypassing. X5R or X7R dielectrics are recommended for the input capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore, not recommended. Also, tantalum and electrolytic capacitors alone are not recommended due to their reduced RMS current handling, reliability, and ESR increases.

An additional  $0.1\mu$ F is recommended close to the VIN and PGND pins for high frequency filtering. Smaller case size capacitors are recommended due to their lower ESR and ESL. Please refer to layout recommendation for proper layout of the input capacitor.

### **Output Capacitor**

The MIC4742 is designed for a  $4.7\mu$ F output capacitor. X5R or X7R dielectrics are recommended for the output capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore not recommended.

In addition to a  $4.7\mu$ F, a small  $0.1\mu$ F is recommended close to the load for high frequency filtering. Smaller case size capacitors are recommended due to there lower equivalent series ESR and ESL.

The MIC4742 utilizes type III voltage mode internal compensation and utilizes an internal zero to compensate for the double pole roll off of the LC filter. For this reason, larger output capacitors can create instabilities. In cases where a 4.7 $\mu$ F output capacitor is not sufficient, other values of capacitance can be used but the original LC filter pole frequency determined by C<sub>OUT</sub> = 4.7 $\mu$ F and L = 1 $\mu$ H (which is approximately 73.4KHz) must remain fixed. Increasing C<sub>OUT</sub> forces L to decrease and vice versa.

#### **Inductor Selection**

The MIC4742 is designed for use with a 1 $\mu$ H inductor. Proper selection should ensure the inductor can handle the maximum average and peak currents required by the load. Maximum current ratings of the inductor are generally given in two methods; permissible DC current and saturation current. Permissible DC current can be rated either for a 40°C temperature rise or a 10% to 20% loss in inductance. Ensure the inductor selected can handle the maximum operating current. When saturation current is specified, make sure that there is enough margin that the peak current will not saturate the inductor.

#### **Diode Selection**

Since the MIC4742 is non-synchronous, a free-wheeling diode is required for proper operation. A Schottky diode is recommended due to the low forward voltage drop and their fast reverse recovery time. The diode should be rated to be able to handle the average output current. Also, the reverse voltage rating of the diode should exceed the maximum input voltage. The lower the forward voltage drop of the diode the better the efficiency. Please refer to the layout recommendation to minimize switching noise.

### Feedback Resistors

The feedback resistor set the output voltage by dividing down the output and sending it to the feedback pin. The feedback voltage is 0.6V. Calculating the set output voltage is as follows;

$$V_{OUT} = V_{FB} \left( \frac{R1}{R2} + 1 \right)$$

Where R1 is the resistor from  $V_{OUT}$  to FB and R2 is the resistor from FB to GND. The recommended feedback resistor values for common output voltages are available in the bill of materials on page 17. Although the range of resistance for the FB resistors is very wide, R1 is recommended to be 10K. This minimizes the effect the parasitic capacitance of the FB node.

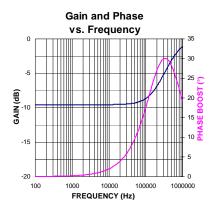

#### Feedforward Capacitor (C<sub>FF</sub>)

A capacitor across the resistor from the output to the feedback pin (R1) is recommended for most designs. This capacitor can give a boost to phase margin and increase the bandwidth for transient response. Also, large values of feedforward capacitance can slow down the turn-on characteristics, reducing inrush current. For maximum phase boost,  $C_{FF}$  can be calculated as follows;

$$C_{FF} = \frac{1}{2\pi \times 200 \text{kHz} \times \text{R1}}$$

Large values of feedforward capacitance may introduce negative FB pin voltage during load shorting, which will cause latch-off. In that case, a Schottky diode from FB pin to the ground is recommended.

#### **Bias Filter**

A small 10 $\Omega$  resistor is recommended from the input supply to the bias pin along with a small 0.1 $\mu$ F ceramic capacitor from bias to ground. This will bypass the high frequency noise generated by the violent switching of high currents from reaching the internal reference and control circuitry. Tantalum and electrolytic capacitors are not recommended for the bias, these types of capacitors lose their ability to filter at high frequencies.

## Loop Stability and Bode Analysis

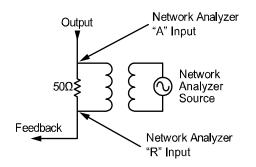

Bode analysis is an excellent way to measure small signal stability and loop response in power supply designs. Bode analysis monitors gain and phase of a control loop. This is done by breaking the feedback loop and injecting a signal into the feedback node and comparing the injected signal to the output signal of the control loop. This will require a network analyzer to sweep the frequency and compare the injected signal to the output signal. The most common method of injection is the use of transformer. Figure 7 demonstrates how a transformer is used to inject a signal into the feedback network.

Figure 7. Transformer Injection

A  $50\Omega$  resistor allows impedance matching from the network analyzer source. This method allows the DC loop to maintain regulation and allow the network analyzer to insert an AC signal on top of the DC voltage. The network analyzer will then sweep the source while monitoring A and R for an A/R measurement.

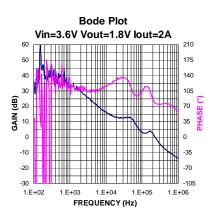

The following Bode analysis show the small signal loop stability of the MIC4742, it utilizes type III compensation. This is a dominant low frequency pole, followed by 2 zeros and finally the double pole of the inductor capacitor filter, creating a final 20dB/decade roll off. Bode analysis gives us a few important data points; speed of response (Gain Bandwidth or GBW) and loop stability. Loop speed or GBW determines the response time to a load transient. Faster response times yield smaller voltage deviations to load steps.

Instability in a control loop occurs when there is gain and positive feedback. Phase margin is the measure of how stable the given system is. It is measured by determining how far the phase is from crossing zero when the gain is equal to 1 (0dB).

Typically for 3.6Vin and 1.8Vout at 2A;

- Phase Margin=77.8 Degrees

- GBW=229KHz

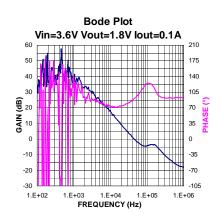

Being that the MIC4742 is non-synchronous; the regulator only has the ability to source current. This means that the regulator has to rely on the load to be able to sink current. This causes a non-linear response at light loads. The following plot shows the effects of the pole created by the nonlinearity of the output drive during light load (discontinuous) conditions.

3.6Vin, 1.8Vout lout=0.1A;

- Phase Margin=89.9 Degrees

- GBW= 43.7kHz

### **Feed Forward Capacitor**

The feedback resistors are a gain reduction block in the overall system response of the regulator. By placing a capacitor from the output to the feedback pin, high frequency signal can bypass the resistor divider, causing a gain increase up to unity gain.

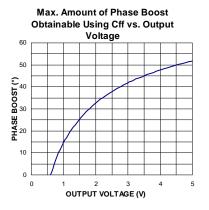

The graph above shows the effects on the gain and phase of the system caused by feedback resistors and a feedforward capacitor. The maximum amount of phase boost achievable with a feedforward capacitor is graphed below.

By looking at the graph, phase margin can be affected to a greater degree with higher output voltages.

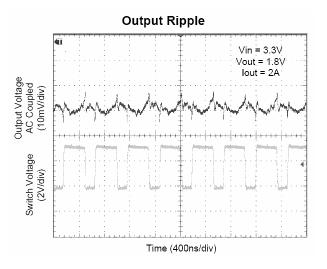

### **Ripple Measurements**

To properly measure ripple on either input or output of a switching regulator, a proper ring in tip measurement is required. Standard oscilloscope probes come with a grounding clip, or a long wire with an alligator clip. Unfortunately, for high frequency measurements, this ground clip can pick-up high frequency noise and erroneously inject it into the measured output ripple.

The standard evaluation board accommodates a home made version by providing probe points for both the input and output supplies and their respective grounds. This requires the removing of the oscilloscope probe sheath and ground clip from a standard oscilloscope probe and wrapping a non-shielded bus wire around the oscilloscope probe. If there does not happen to be any non-shielded bus wire immediately available, the leads from axial resistors will work. By maintaining the shortest possible ground lengths on the oscilloscope probe, true ripple measurements can be obtained.

# **Bill of Materials**

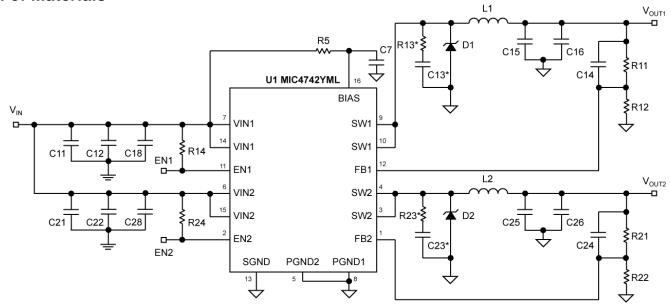

MIC4742YML Schematic for 2A Output

| Item                  | Part Number       | Manufacturer          | Description                                          | Qty |

|-----------------------|-------------------|-----------------------|------------------------------------------------------|-----|

| C11,C12               | GRM188R60J106M    | Murata <sup>(1)</sup> |                                                      |     |

| C21,C22               | C1608X5R0J106M    | TDK <sup>(2)</sup>    | 10μF Ceramic Capacitor X5R 0603 6.3V                 |     |

|                       | 06036D106KMAT2A   | AVX <sup>(3)</sup>    |                                                      |     |

| C13*,C23*             | VJ0603A681KXXCW   | Vishay <sup>(4)</sup> | 680pF Ceramic Capacitor NPO 0603 6.3V                | 2   |

| C14,C24               | VJ0603A820KXXCW   | Vishay <sup>(4)</sup> | 82pF Ceramic Capacitor NPO 0603 10V                  | 2   |

| C15,C25               | GRM188R60J475K    | Murata <sup>(1)</sup> |                                                      |     |

|                       | C1608 X5R0J475M   | TDK <sup>(2)</sup>    | 4.7µF Ceramic Capacitor X5R 0603 6.3V                | 2   |

|                       | 0603D475MAT       | AVX <sup>(3)</sup>    |                                                      |     |

| C16,C26,C7<br>C18,C28 | VJ0603Y104KXXAT   | Vishay <sup>(4)</sup> | 0.1µF Ceramic Capacitor X7R 0603 25V                 | 5   |

| D1,D2                 | SS2P3L            | Vishay <sup>(4)</sup> |                                                      |     |

|                       | SSA23L            | Vishay <sup>(4)</sup> | 2A Schottky 30V                                      | 2   |

|                       | B230A             | Diodes <sup>(5)</sup> |                                                      |     |

| L1,L2                 | IHLP2525AH-01 1R0 | Vishay <sup>(4)</sup> | 1µH Inductor 17.5mΩ 6.86mm(L) x 6.47mm(W) x 1.8mm(H) |     |

|                       | RLF7030-1R0 N     | TDK <sup>(2)</sup>    | 1µH Inductor 8.8mΩ 7.3mm(L) x 6.8mm(W) x 3.2mm(H)    | 2   |

|                       | HCP0703-1R0       | COOPER <sup>(6)</sup> | 1µH Inductor 10mΩ 7.3mm(L) x 7.0mm(W) x 3.0mm(H)     |     |

| R11,R12               | CRCW060310K0FKXX  | Vishay <sup>(4)</sup> | 10KΩ1% 0603 resistor                                 | 2   |

| R12,R22               | CRCW06033K16FKXX  |                       | 3.16kΩ 1% 0603 For 2.5V <sub>OUT</sub>               |     |

|                       | CRCW06034K99FKXX  |                       | 4.99kΩ 1% 0603 For 1.8 V <sub>OUT</sub>              |     |

|                       | CRCW06036K65FKXX  | Vishay <sup>(4)</sup> | 6.65kΩ 1% 0603 For 1.5 V <sub>OUT</sub>              | 2   |

|                       | CRCW060310K0FKXX  |                       | 10kΩ 1% 0603 For 1.2 V <sub>OUT</sub>                |     |

|                       | CRCW060315K0FKXX  |                       | 15kΩ 1% 0603 For 1.0 V <sub>OUT</sub>                |     |

\* only for ultra-low noise applications.

| ltem       | Part Number      | Manufacturer                | Description                                   | Qty |

|------------|------------------|-----------------------------|-----------------------------------------------|-----|

| R13*, R23* | CRCW06032R70FKXX | Vishay <sup>(4)</sup>       | 2.7Ω1% 0603 resistor                          | 2   |

| R14, R24   | CRCW060349K9FKXX | Vishay <sup>(4)</sup>       | 49.9kΩ1% 0603 resistor                        | 2   |

| R5         | CRCW060310R0FKXX | Vishay <sup>(4)</sup>       | 10Ω1% 0603 resistor                           | 1   |

| U1         | MIC4742YML       | Micrel, Inc. <sup>(7)</sup> | Dual 2A 2MHz Integrated Switch Buck Regulator | 1   |

Notes:

1. Murata: www.murata.com

2. TDK: www.tdk.com

3. AVX: www.avx.com

4. Vishay: www.vishay.com

5. Cooper: www.cooperbussmann.com

6. Diode: www.diodes.com

7. Micrel, Inc: www.micrel.com

\* only for ultra-low noise applications.

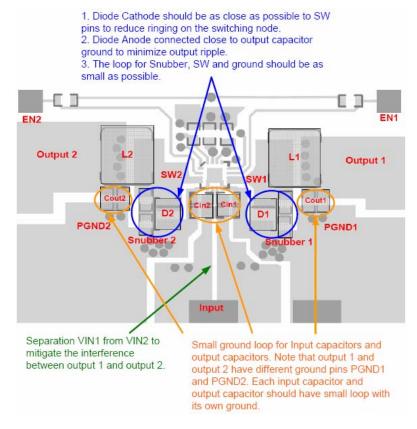

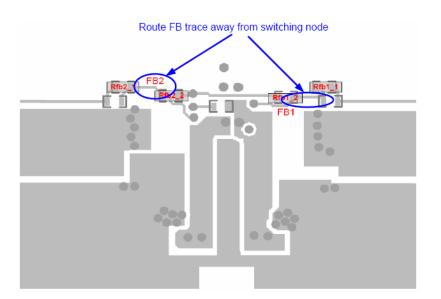

## MIC4742YML Layout Recommendation: 2A Evaluation Board

#### **Recommended TOP Layout**

**Recommended Bottom Layout**

## **Package Information**

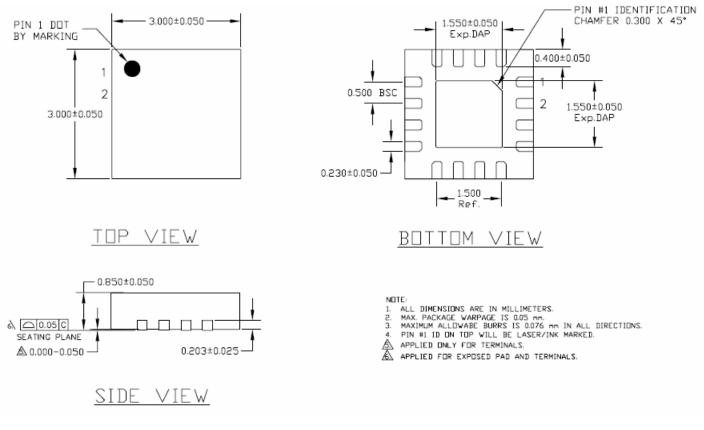

16-Pin 3mm x 3mm MLF<sup>®</sup> (ML)

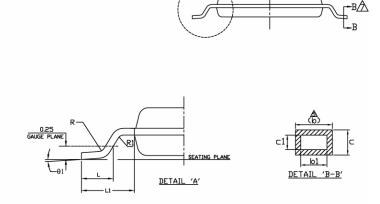

DETAIL 'A'

TOP VIEW

# BOTTOM VIEW

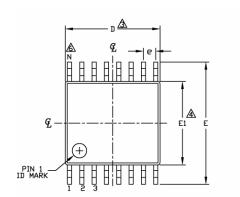

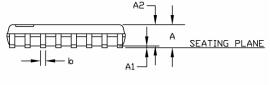

| SYMBOL     | 14L TSSOP<br>Thermally Enhanced         |              |            | 16L TSSOP<br>Thermally Enhanced |                      |            |

|------------|-----------------------------------------|--------------|------------|---------------------------------|----------------------|------------|

| Ś          | MIN                                     | NDM.         | MAX        | MIN                             | NDM.                 | MAX        |

| A          | —                                       | _            | 1.20       | —                               |                      | 1.20       |

| A1         | 0.025                                   | _            | 0.100      | 0.025                           | _                    | 0.100      |

| A2         | 0.80                                    | 0.90         | 1.05       | 0.80                            | 0.90                 | 1.05       |

| D          | 4.9                                     | 5.0          | 5.1        | 4.9                             | 5.0                  | 5.1        |

| D<br>E1    | 4.3                                     | 4.4          | 4.5        | 4.3                             | 4.4                  | 4.5        |

| E          | 6,2                                     | 6.4          | 6.6        | 6.2                             | 6.4                  | 6,6        |

| L          | 0.45                                    | 0.60         | 0.75       | 0.45                            | 0.60                 | 0.75       |

| R          | 0.09                                    | _            | _          | 0.09                            | _                    | —          |

| R1         | 0.09                                    | _            | —          | 0.09                            | —                    |            |

| b          | 0.19                                    | _            | 0.30       | 0.19                            | _                    | 0.30       |

| b1         | 0.19                                    | 0.22         | 0.25       | 0.19                            | 0.22                 | 0.25       |

| C          | 0.09                                    | _            | 0.20       | 0.09                            | _                    | 0.20       |

| c1         | 0.09                                    |              | 0.16       | 0.09                            | —                    | 0.16       |

| θ1         | 0°                                      |              | 8°         | 0*                              | —                    | 8*         |

| L1         | 1.0 REF                                 |              |            | 1.0 REF                         |                      |            |

| e          | 0.65 BSC                                |              |            | 0.65 BSC                        |                      |            |

| N          | 14                                      |              |            | 16                              |                      |            |

| Ref.       | Jedec MD-153 Issue C<br>Variation ABT-1 |              |            |                                 | MD-153 Is<br>ion ABT | ssue C     |

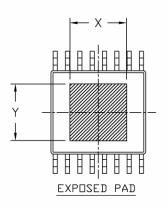

| EP<br>Area | Pad Size<br>Op 1                        | × χ<br>2.997 | Y<br>3.200 | Pad Size<br>Op 1                | × X<br>2.997         | Y<br>2.997 |

### <u>Notes</u>

- 1. AU DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M-1982.

- $\textcircled{\mbox{\sc def}}$  DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH ,PROTRUSIONS OR GATE BURRS.

- ▲ DIMENSION 'E1' DOES NOT INCLUDE INTERNAL FLASH OR PROTRUSION.

- ▲ DIMENSION 'b' DOES NOT INCLUDE DAMBAR PROTRUSION.

- ▲ 'N' IS THE MAXIMUM NUMBER OF LEAD TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

- FOR THE SPECIFIED PACKAGE LENGTH. A CROSS SECTION B-B TO BE DETERMINED AT 0.10 TO 0.25MM FROM THE LEAD TIP.

- 8. EXPOSED PAD WILL BE DEPEND ON THE PAD SIZE OF THE L/F.

#### 16-Pin ETSSOP

#### **MICREL, INC.** 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2008 Micrel, Incorporated.