# M30620T2-RPD-E

Emulation Pod for M16C/62,62A Group MCUs

User's Manual

\* IC61-1004-051 is a trademark of Yamaichi Electronics Co., Ltd.

\* NQPACK, YQPACK, YQSOCKET, YQ-Guide, HQPACK, TQPACK and TQSOCKET are trademarks of Tokyo Eletech Corporation.

#### **Keep safety first in your circuit designs!**

- Renesas Technology Corporation and Renesas Solutions Corporation put the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### **Notes regarding these materials**

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation, Renesas Solutions Corporation or a third party.

- Renesas Technology Corporation and Renesas Solutions Corporation assume no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation and Renesas Solutions Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation, Renesas Solutions Corporation or an authorized Renesas Technology product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation and Renesas Solutions Corporation assume no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corporation and Renesas Solutions Corporation by various means, including the Renesas home page (<http://www.renesas.com>).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation and Renesas Solutions Corporation assume no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Renesas Technology semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation, Renesas Solutions Corporation or an authorized Renesas Technology product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation and Renesas Solutions Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Renesas Technology Corporation or Renesas Solutions Corporation for further details on these materials or the products contained therein.

#### **Precautions to be taken when using this product**

- This product is a development supporting unit for use in your program development and evaluation stages. In mass-producing your program you have finished developing, be sure to make a judgment on your own risk that it can be put to practical use by performing integration test, evaluation, or some experiment else.

- In no event shall Renesas Solutions Corporation be liable for any consequence arising from the use of this product.

- Renesas Solutions Corporation strives to cope with the issues given below at some charge or without charge.

- (1) Repairing or replacing a flawed product. There can be instances in which a product cannot be repaired if more than one year have passed since the discontinuance of its marketing.

- (2) Renovating or providing a workaround for product malfunction. This does not necessarily mean that Renesas Solutions Corporation guarantees the renovation or the provision under any circumstances.

- This product has been developed by assuming its use for program development and evaluation in laboratories. Therefore, it does not fall under the application of Electrical Appliance and Material Safety Law and protection against electromagnetic interference when used in Japan.

- Do not attempt to modify this equipment. If modified, your authority to operate this equipment might be voided by FCC.

Note: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

Warning: This is a Class A product. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

For inquiries about the contents of this document or product, fill in the text file the installer of the emulator debugger generates in the following directory and email to your local distributor.

\SUPPORT\Product-name\SUPPORT.TXT

Renesas Tools Homepage <http://www.renesas.com/en/tools>

# Preface

The M30620T2-RPD-E is an emulation pod for the M16C/62 and M16C/62A Groups of 16-bit microcomputers. It's used with a PC4701 emulator.

This user's manual mainly describes functions of the M30620T2-RPD-E emulation pod and how to operate it. For details on the following products, which are used with M30620T2-RPD-E, refer to each product's user's manual.

- Emulator: PC4701M/PC4701HS/PC4701L User's Manual

- Emulator debugger: M3T-PD30 User's Manual

All the components of this product are shown in "2.2 Package Components" (page 19) of this user's manual. If there is any question or doubt about this product, contact your local distributor.

## To use the product properly

### Precautions for Safety

- In both this user's manual and on the product itself, several icons are used to insure proper handling of this product and also to prevent injuries to you or other persons, or damage to your properties.

- The icons' graphic images and meanings are given in "Chapter 1. Precautions for Safety". Be sure to read this chapter before using the product.

## When using outside Japan

- When using in Europe, the United States, or Canada, be sure to use both the emulator (PC4701M, PC4701HS or PC4701L) and the emulation pod which meet overseas standards. EMI standards are not met when the M30620T2-RPD-E is used with the PC4700H or PC4700L emulator.

# Contents

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| Chapter 1. Precautions for Safety .....                                       | 7  |

| 1.1 Safety Symbols and Meanings .....                                         | 8  |

| Chapter 2. Preparation .....                                                  | 17 |

| 2.1 Terminology .....                                                         | 18 |

| 2.2 Package Components .....                                                  | 19 |

| 2.3 Other Tool Products Required for Development .....                        | 19 |

| 2.4 Name of Each Part .....                                                   | 20 |

| (1) System Configuration .....                                                | 20 |

| (2) Inside of Emulation Pod .....                                             | 21 |

| 2.5 When Using the Emulator for the First Time .....                          | 22 |

| Chapter 3. Setting Up .....                                                   | 23 |

| 3.1 Removing the Upper Cover .....                                            | 24 |

| 3.2 Setting Switches and Pullup Resistor .....                                | 25 |

| 3.3 Selecting Clock Supply .....                                              | 29 |

| (1) Using the Oscillator Circuit on Target System .....                       | 30 |

| (2) Changing the Internal Oscillator Circuit of Emulation Pod .....           | 31 |

| (3) Replacing the Oscillator Circuit Boards .....                             | 32 |

| 3.4 Connecting the PC4701 and Emulation Pod .....                             | 33 |

| (1) Connecting the Cable to the PC4701 .....                                  | 33 |

| (2) Connecting the Cable to the Emulation Pod .....                           | 34 |

| 3.5 Connecting the Target System .....                                        | 35 |

| Chapter 4. Usage .....                                                        | 37 |

| 4.1 Turning On the Power .....                                                | 38 |

| (1) Checking the Connection of the Emulator System .....                      | 38 |

| (2) Turning On the Power .....                                                | 38 |

| (3) LED Display When PC4701 Starts Up Normally .....                          | 39 |

| 4.2 Downloading Firmware .....                                                | 40 |

| (1) When It is Necessary to Download Firmware .....                           | 40 |

| (2) Downloading Firmware in Maintenance Mode .....                            | 40 |

| 4.3 Self-check .....                                                          | 41 |

| (1) Self-check Procedure .....                                                | 41 |

| (2) If an Error is Detected in the Self-check .....                           | 41 |

| Chapter 5. Specifications .....                                               | 43 |

| 5.1 Specifications .....                                                      | 44 |

| 5.2 Operation Timing in Memory Expansion and Microprocessor Modes (5 V) ..... | 45 |

| (1) Separate Bus, No-wait .....                                               | 45 |

|                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------|----|

| (2) Separate Bus, With Wait, Accessing External Memory Area .....                                        | 47 |

| (3) Multiplex Bus, With Wait, Accessing External Memory Area .....                                       | 49 |

| (4) Timing Requirements .....                                                                            | 51 |

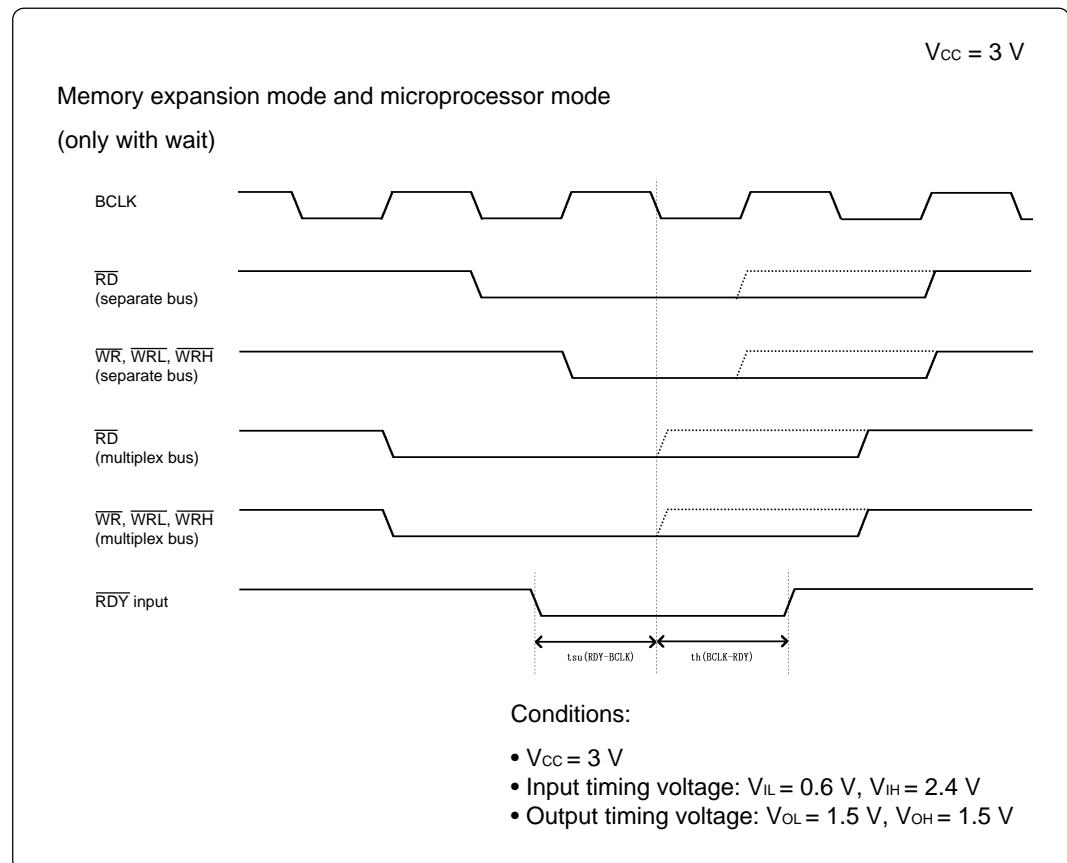

| 5.3 Operation Timing of Memory Expansion and Microprocessor Modes (3 V) .....                            | 53 |

| (1) Separate Bus, No-wait .....                                                                          | 53 |

| (2) Separate Bus, With Wait, Accessing External Memory Area .....                                        | 55 |

| (3) Multiplex Bus, With Wait, Accessing External Memory Area .....                                       | 57 |

| (4) Timing Requirements .....                                                                            | 59 |

| 5.4 Electrical Characteristics .....                                                                     | 61 |

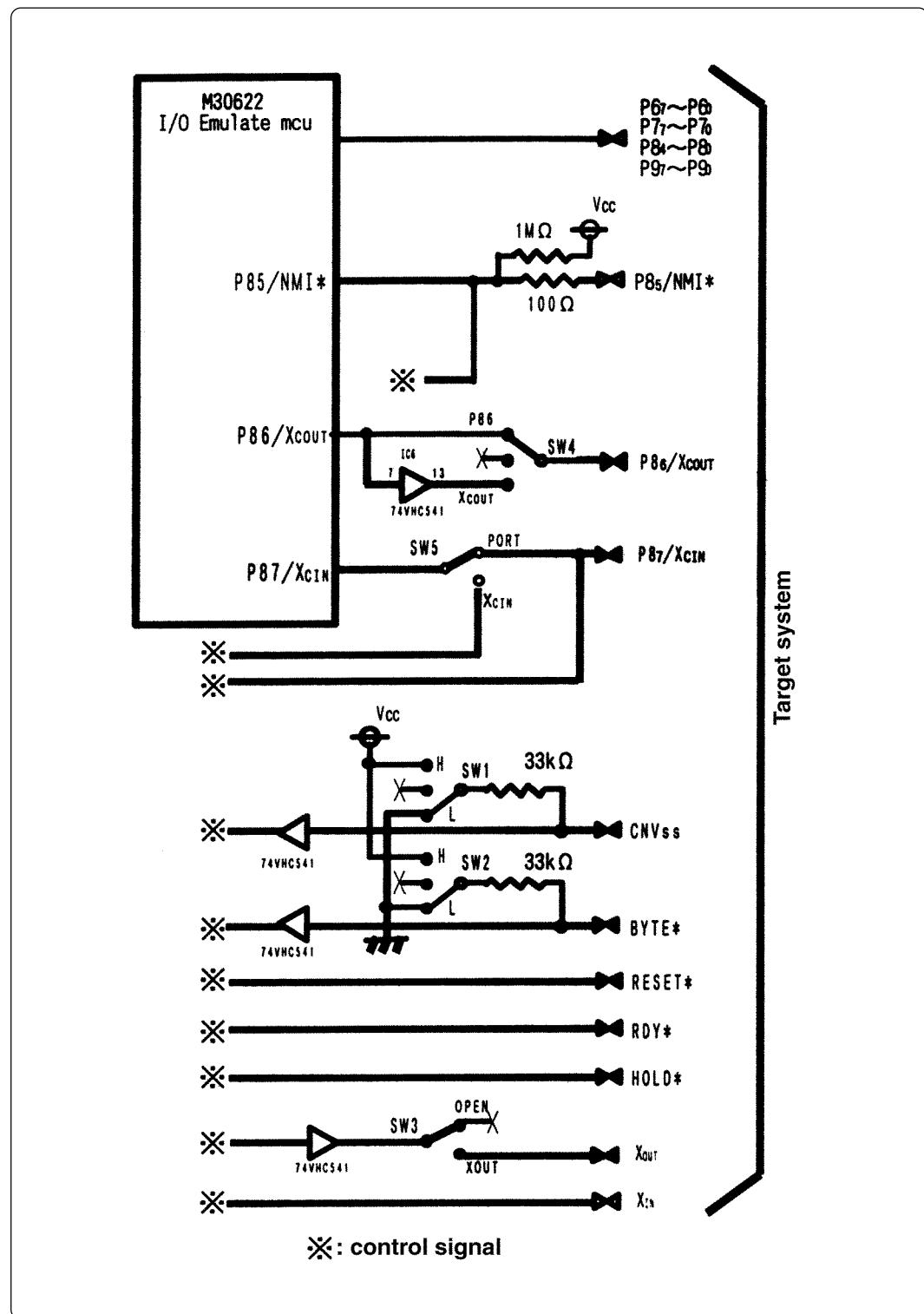

| 5.5 Connection Diagram .....                                                                             | 62 |

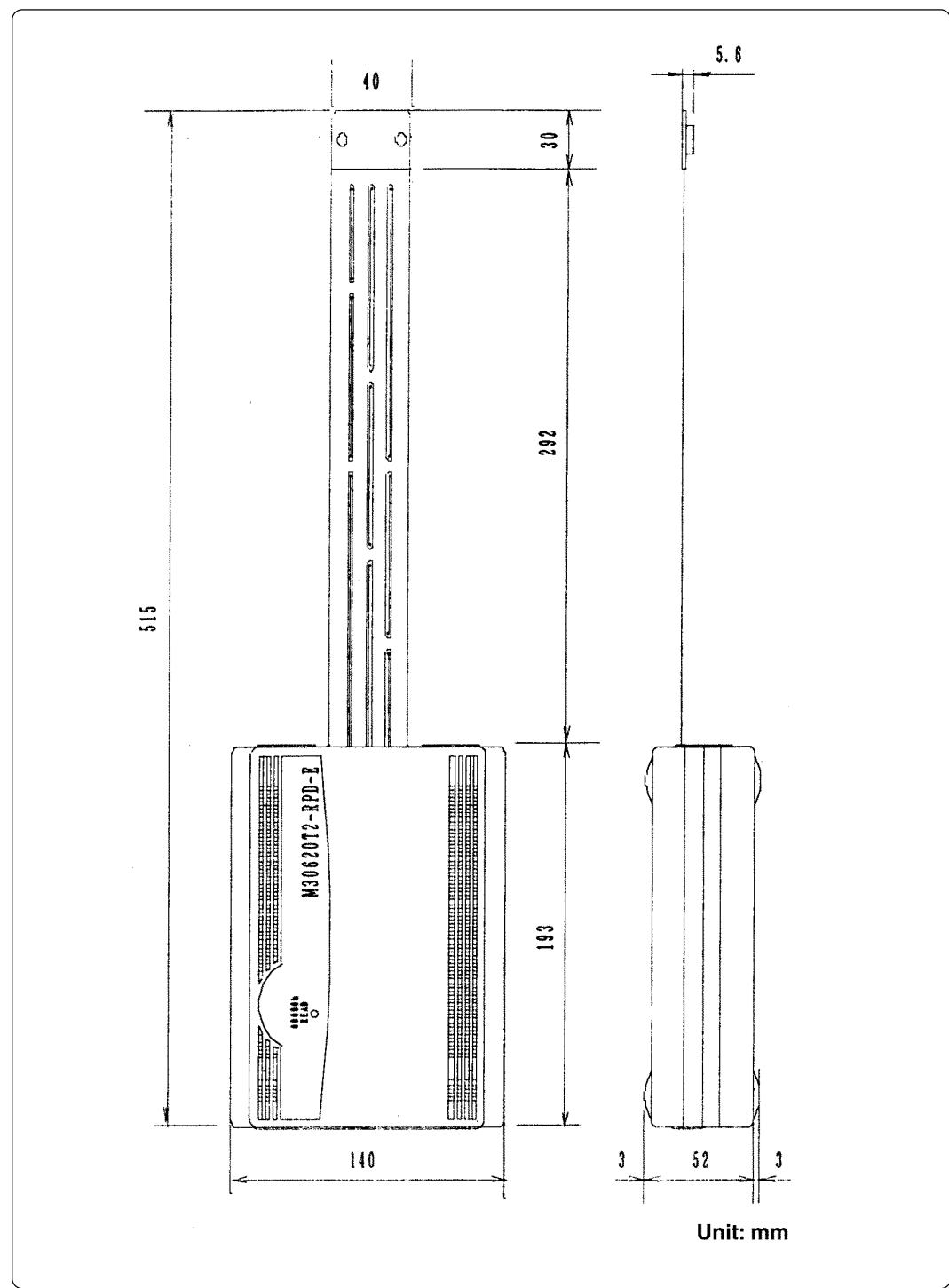

| 5.6 External Dimensions .....                                                                            | 64 |

| (1) External Dimensions of Emulation Pod .....                                                           | 64 |

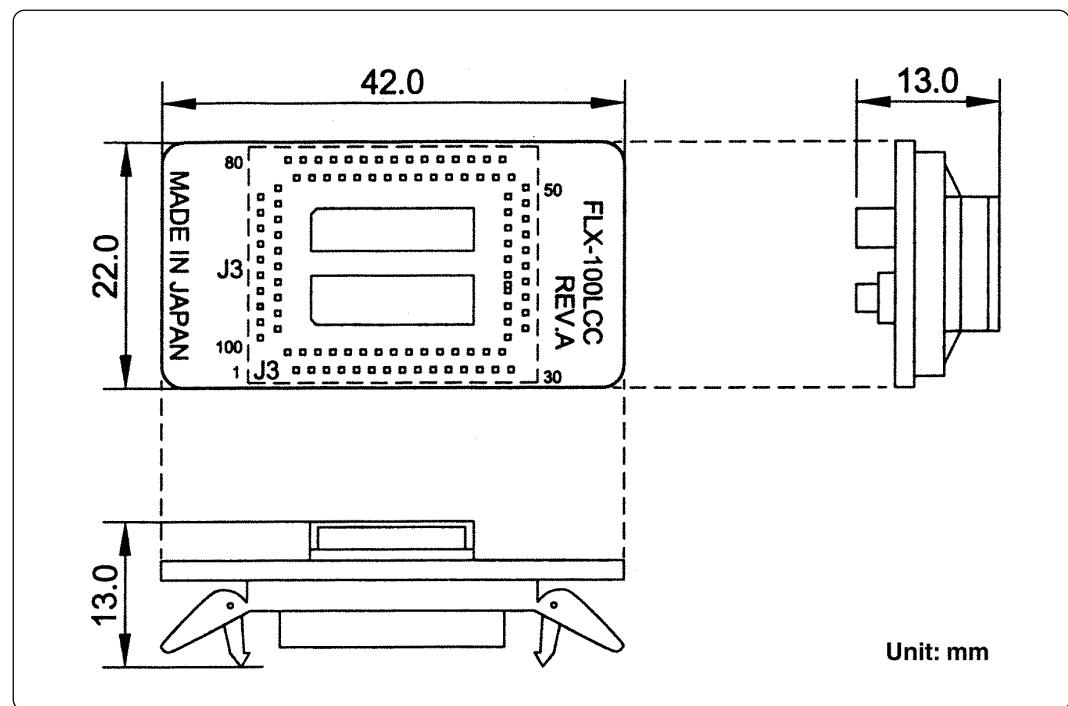

| (2) External Dimensions of Pitch Converter Board (FLX-100LCC) .....                                      | 65 |

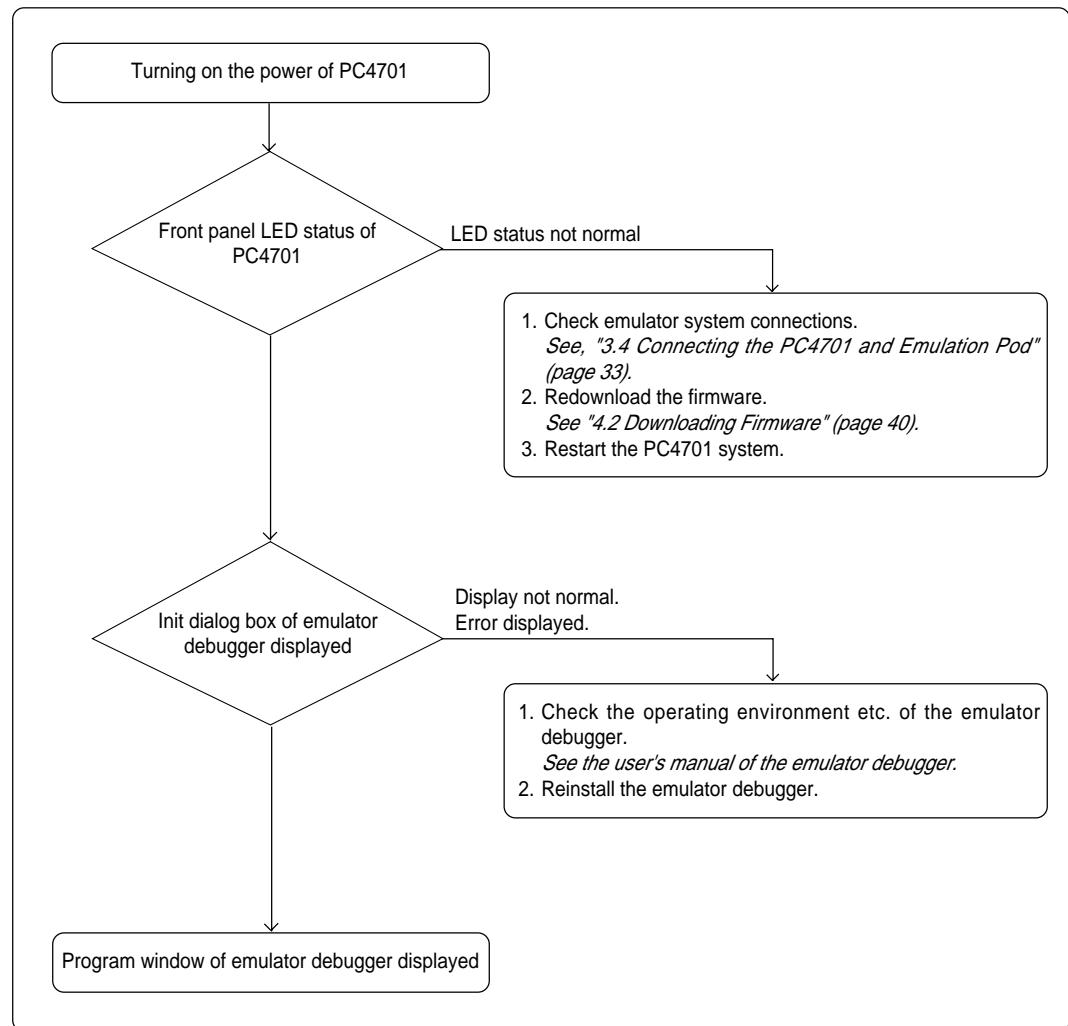

| Chapter 6. Troubleshooting .....                                                                         | 67 |

| 6.1 Flowchart to Remedy the Troubles .....                                                               | 68 |

| 6.2 When the Emulator Debugger Does Not Start Up Properly .....                                          | 69 |

| (1) When the LED Display of PC4701 is Abnormal .....                                                     | 69 |

| (2) Errors Occur When the Emulator Debugger Starts up<br>(When the target system is connected) .....     | 70 |

| (3) Errors Occur When the Emulator Debugger Starts up<br>(When the target system is not connected) ..... | 71 |

| 6.3 Operation Differs from That of PROM Version MCUs .....                                               | 71 |

| (1) Does Not Operate with Operating Frequencies (3.6 V to 5.5 V) Properly ..                             | 71 |

| (2) Does Not Operate with Operating Frequencies (2.7 V to 3.6 V) Properly ..                             | 71 |

| (3) Cannot Reset from Target System .....                                                                | 71 |

| (4) Data Values of ROM Area at Power-on Are Different .....                                              | 72 |

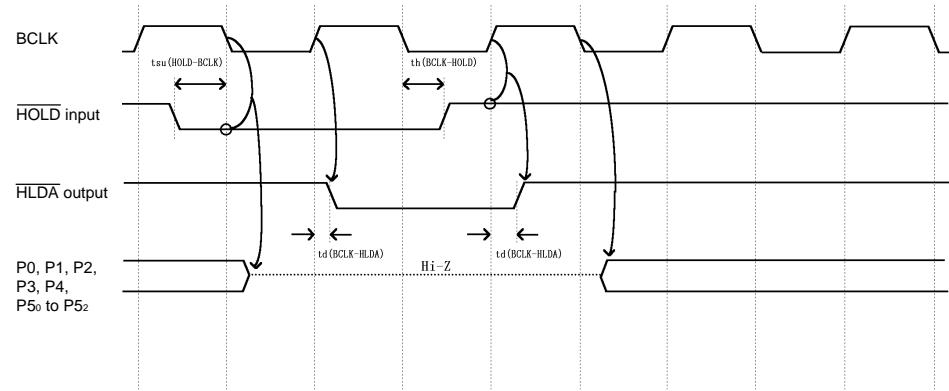

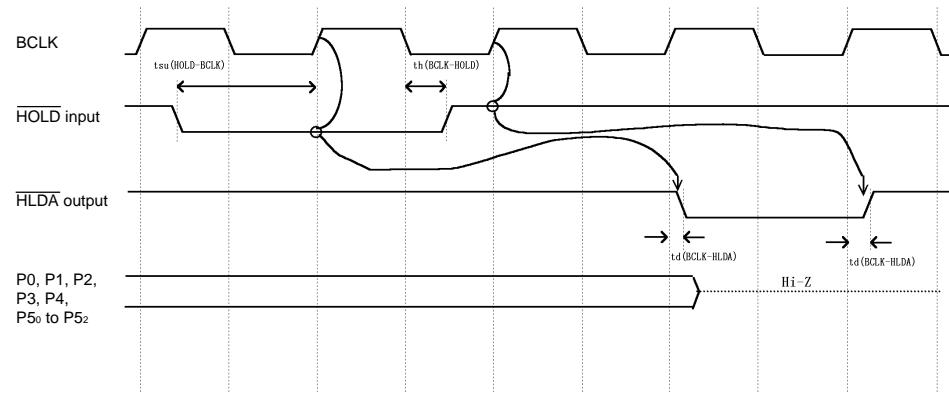

| (5) HOLD* control .....                                                                                  | 72 |

| (6) A-D Conversion Values are Different from Expected Values .....                                       | 72 |

| (7) Outputs of ALE, Address and Others are Different from Those of Actual MCUs ..                        | 72 |

| Chapter 7. Maintenance and Guarantee .....                                                               | 73 |

| 7.1 Maintenance .....                                                                                    | 74 |

| 7.2 Guarantee .....                                                                                      | 74 |

| 7.3 Repair Provisions .....                                                                              | 74 |

| 7.4 How to Request for Repair .....                                                                      | 75 |

# MEMO

# Chapter 1. Precautions for Safety

This chapter describes precautions for using this product safely and properly. For precautions for the emulator main unit and the emulator debugger, refer to each user's manual included with your product.

|                                       |                                                              |    |

|---------------------------------------|--------------------------------------------------------------|----|

| 1.1 Safety Symbols and Meanings ..... | 8                                                            |    |

| <b>WARNING</b>                        | Warning for Installation .....                               | 9  |

|                                       | Warnings for Use Environment .....                           | 9  |

| <b>CAUTION</b>                        | Caution to Be Taken for Modifying This Product .....         | 9  |

|                                       | Cautions to Be Taken for This Product .....                  | 9  |

| <b>IMPORTANT</b>                      | Note on Malfunctions in the PC4701 System .....              | 9  |

|                                       | Notes on Downloading Firmware .....                          | 10 |

|                                       | Notes on Target System .....                                 | 10 |

|                                       | Note on Reset Input .....                                    | 10 |

|                                       | Notes on Watchdog Function .....                             | 10 |

|                                       | Note on When the Emulator Debugger Ends .....                | 10 |

|                                       | Note on DMA Transfer .....                                   | 11 |

|                                       | Note on Setting the Work Area .....                          | 11 |

|                                       | Notes on Stack Area .....                                    | 11 |

|                                       | Note on Address 0 Access .....                               | 11 |

|                                       | Note on Stop and Wait Modes .....                            | 11 |

|                                       | Notes on MAP References and Settings .....                   | 12 |

|                                       | Notes on Software Breaks and Hardware Breaks .....           | 12 |

|                                       | Note on BRK Instruction .....                                | 12 |

|                                       | Note on NMI* Input .....                                     | 13 |

|                                       | Note on HOLD* Input .....                                    | 13 |

|                                       | Notes on Address Match Interrupt .....                       | 13 |

|                                       | Note on Software Reset .....                                 | 13 |

|                                       | Note on Protect Resistor (PRC2) .....                        | 13 |

|                                       | Note on Pullup Control Resistor .....                        | 13 |

|                                       | Note on Differences between Actual MCU and Emulator .....    | 14 |

|                                       | Note on Switch Settings According to Operation Voltage ..... | 16 |

# Chapter 1. Precautions for Safety

In both the user's manual and on the product itself, several icons are used to insure proper handling of this product and also to prevent injuries to you or other persons, or damage to your properties.

This chapter describes the precautions which should be taken in order to use this product safely and properly. Be sure to read this chapter before using this product.

## 1.1 Safety Symbols and Meanings

### **WARNING**

If the requirements shown in the "WARNING" sentences are ignored, the equipment may cause serious personal injury or death.

### **CAUTION**

If the requirements shown in the "CAUTION" sentences are ignored, the equipment may malfunction.

### **IMPORTANT**

It means important information on using this product.

In addition to the three above, the following are also used as appropriate.

△ means WARNING or CAUTION.

Example:  **CAUTION AGAINST AN ELECTRIC SHOCK**

○ means PROHIBITION.

Example:  **DISASSEMBLY PROHIBITED**

● means A FORCIBLE ACTION.

Example:  **UNPLUG THE POWER CABLE FROM THE RECEPTACLE.**

The following pages describe the symbols "WARNING", "CAUTION", and "IMPORTANT".

## ⚠ WARNING

### Warning for Installation:

- Do not set this product in water or areas of high humidity. Spilling water or some other liquid into the main unit can cause an unrepairable damage.

### Warnings for Use Environment:

- The emulation pod is air-cooled with the ventilation slot. Therefore, do not block the ventilation slot. When heated to high temperatures, the emulation pod may not work properly.

- This equipment is to be used in an environment with a maximum ambient temperature of 35°C. Care should be taken that this temperature is not exceeded.

## ⚠ CAUTION

### Caution to Be Taken for Modifying This Product:

- Do not disassemble or modify this product. Disassembling or modifying this product can cause damage. Disassembling and modifying the product will void your warranty.

### Cautions to Be Taken for This Product:

- Use caution when handling the main unit. Be careful not to apply a mechanical shock.

- Do not touch the connector pins of the emulator main unit and the target MCU connector pins directly with your hand. Static electricity may damage the internal circuits.

- Do not pull the emulation pod main unit by the flexible cable (FLX120-RPD) for connecting to the emulator main unit or the flexible cable (FLX64, FLX100 or FLX160) for connecting the target system. The cable may cause a break.

- Flexible cable (FLX120-RPD) for connecting to the emulator main unit and the flexible cable (FLX64, FLX100 or FLX160) for connecting the target system are different from earlier models. The slits make them more flexible. However, excessive flexing or force may break conductors.

- Do not use inch-size screws for this equipment. The screws used in this equipment are all ISO (meter-size) type screws. When replacing screws, use same type screws as equipped before.

## IMPORTANT

### Note on Malfunctions in the PC4701 System

- If the emulator malfunctions because of interference like external noise, do the following to remedy the trouble.

- (1) Press the RESET switch on the emulator front panel.

- (2) If normal operation is not restored after step (1), shut OFF power to the emulator once and then reactivate it.

## IMPORTANT

### Notes on Downloading Firmware:

- Before using this product for the first time, it is necessary to download the dedicated firmware (control software for the emulation pod built into the PC4701). Please note that, to do this, it is necessary to start up the PC4701 in the maintenance mode. For firmware download procedures, see "4.2 Downloading Firmware" (page 40). Once the firmware has been downloaded, the product can be used by simply turning on the power.

- Do not shut off the power while downloading the firmware. If this happens, the product will not start up properly. If power is shut off unexpectedly, redownload the firmware.

- Except when a target status error occurs, if the self-check is not completed successfully, there may be trouble with the product. In such case, contact your sales representative. However, perform the self-check in the below setup.

- (1) Target system: Not connected

- (2) Emulation pod internal switches: At their factory settings

### Notes on Target System:

- The Vcc pin of emulator is connected to the target system to observe the voltage of the target system. Therefore design your system so that the emulator MCU is powered by the target system.

- The voltage of the target system should be within the range of the MCU specification.

- Do not change the voltage of the target system after turning on the power.

- Before powering on your emulator system, check that the host machine, the emulator main unit, the converter board and target system are all connected correctly. Next, turn on the power to each equipment following the procedure below.

- (1) Turn ON/OFF the target system and the PC4701 emulator as simultaneously as possible.

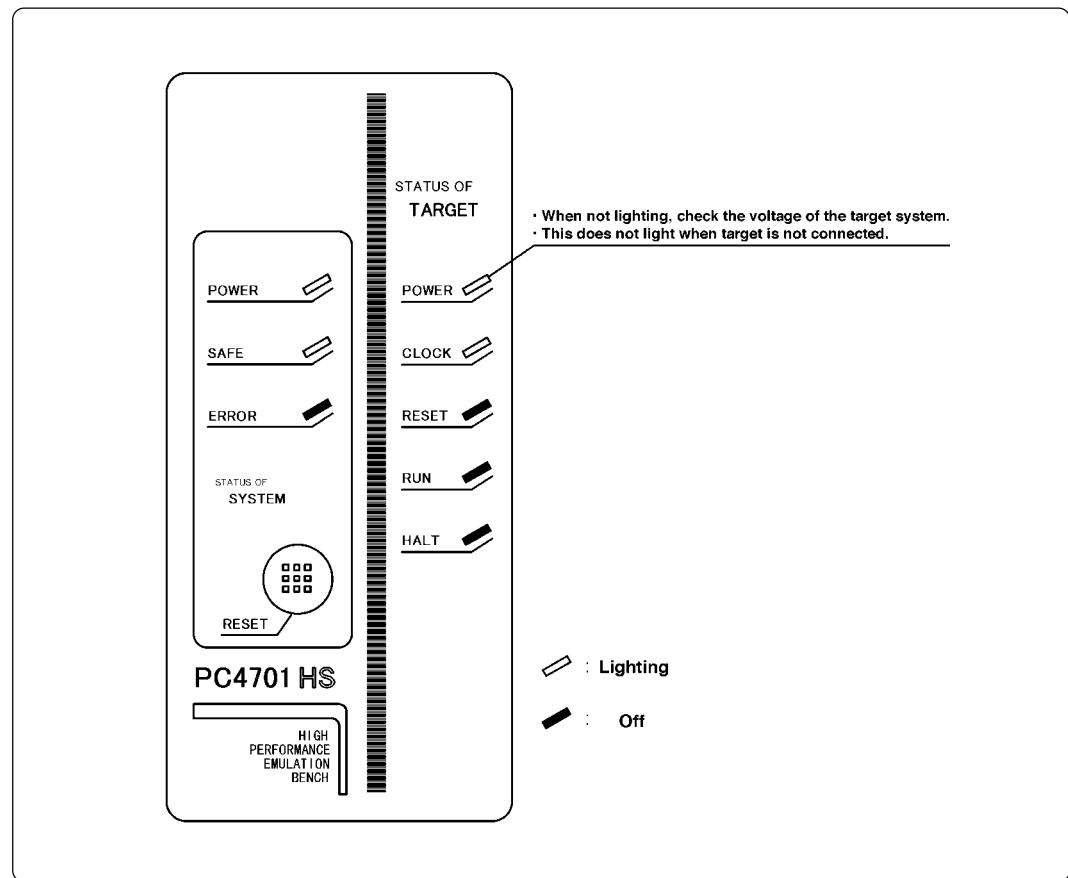

- (2) When the PC4701 and emulator debugger start up, check the target status LEDs on the emulator main unit's front panel to see if this product is ready to operate.

- Is the power supplied? Check that target status LED (POWER) is ON.

For details, refer to "Chapter 4. Usage" (page 37).

### Note on Reset Input:

- The reset input from the target system is accepted only while a user program is being executed (only while the RUN status LED on the PC4701's front panel is lit).

### Notes on Watchdog Function:

- The MCU's watchdog timer can be used only while programs are being executed. To use it otherwise, disable the timer.

- If the reset circuit of the target system has a watchdog timer, disable it when using the emulator.

### Note on When the Emulator Debugger Ends:

- To restart the emulator debugger after it ends, always shut power to the emulator module off once and then on again.

## IMPORTANT

### Note on DMA Transfer:

- With this product, the program is stopped with a loop program to a specific address. Therefore, if a DMA request is generated by a timer or other source while the program is stopped, DMA transfer is executed. However, make note of the fact that DMA transfer while the program is stopped may not be performed correctly. Also note that the below registers have been changed to generate DMA transfer as explained here even when the program is stopped.

DMA0 transfer counter register TCR0

DMA1 transfer counter register TCR1

### Note on Setting the Work Area:

- To use this product, it is necessary to set the work area in the internal reserved area of the MCU. However, do not set it in the last 10 bytes of the internal reserved area. And be sure to set the internal reserved area to INTERNAL. (Set the work area by INIT window of the emulator debugger M3T-PD30.)

Example 1: When debugging the program of the MCU whose internal reserved area is  $02C00_{16}$  to  $03FFF_{16}$  address, set the work area within the range of  $02C00_{16}$  to  $03FF6_{16}$  address.

Example 2: When debugging the program of the MCU whose internal reserved area is  $05400_{16}$  to  $05FFF_{16}$  address, set the work area within the range of  $05400_{16}$  to  $05FF6_{16}$  address.

For instance, when setting the work area at  $05C00_{16}$ , the emulator uses 10 bytes area of  $05C00_{16}$  to  $05C09_{16}$ .

### Notes on Stack Area:

- With this product, a maximum 8 bytes of the user stack is consumed.

- If the user stack does not have enough area, do not use areas which cannot be used as stack (SFR area, RAM area which stores data, or ROM area) as work area. Using areas like this is a cause of user program crashes and destabilized emulator control. Therefore, ensure the +8 bytes maximum capacity used by the user program as the user stack area.

### Note on Address 0 Access:

- With the M16C/62 and 62A Group MCUs, when a maskable interrupt is generated, the interrupt data (interrupt No. and interrupt request level) stored in address 0 is read out. Also, the interrupt request bit is cleared when address 0 is read out. Consequently, when the address 0 readout instruction is executed or when address 0 is read out in the cause of a program runaway, a malfunction occurs in that the interrupt is not executed despite the interrupt request, because the request bit of the highest priority interrupt factor enabled is cleared.

For this malfunction, when the reading out to the 0 address is generated excluding the interrupt, the yellow LED lights up to alarm. When this LED lights, there is a possibility of wrong access, therefore check the program. This LED is turned off by the RESET switch of the emulator main unit.

### Note on Stop and Wait Modes:

- Do not perform step execution at addresses in the stop or wait mode. It may cause communication errors.

## IMPORTANT

### Notes on MAP References and Settings:

- For details on referencing and setting MAP information, see User's Manual of the emulator debugger M3T-PD30.

- Be sure to set the SFR area to EXTERNAL (an external section).

- When setting  $0FFFC_{16}$  to  $0FFFF_{16}$  to EXTERNAL :

This product uses the 4 byte area  $0FFFC_{16}$  through  $0FFFF_{16}$  as the stack area. If this 4 byte memory cannot be read or written to, reset cannot be properly effected. As a result, you need to alter the map settings if the condition given below is met.

- (1) With the system which shifts from the single-chip mode to the memory expansion (or microprocessor) mode, using the 4 byte area of  $0FFFC_{16}$  to  $0FFFF_{16}$  set to EXTERNAL.

- (2) With the system which starts up in microprocessor mode, using the 4 byte area of  $0FFFC_{16}$  to  $0FFFF_{16}$  set to EXTERNAL and there is not enough memory to read or write.

The procedures to alter the MAP settings when the conditions (1) or (2) above are met.

- (1) Set the 4 byte area of  $0FFFC_{16}$  to  $0FFFF_{16}$  to INTERNAL.

- (2) Execute the RESET command by use of the emulator debugger M3T-PD30.

- (3) Set the stack pointer.

(Example)

RESET:

|      |                                                     |

|------|-----------------------------------------------------|

| FCLR | I                                                   |

| LDC  | #480H, SP <-- Set the stack pointer                 |

| .    | (Stop the program after executing this instruction) |

- (4) Set the 4 byte area  $0FFFC_{16}$  through  $0FFFF_{16}$  to EXTERNAL.

### Notes on Software Breaks and Hardware Breaks:

- Software breaks generate BRK interrupts by substituting the proper instruction to the BRK instruction. Therefore, when referencing the result of a trace in bus mode, " $00_{16}$ " is displayed for the instruction fetch address where a software break is set, and when referencing in reverse assemble mode, "BRK" instruction is displayed.

- It is not possible to use a software break and a hardware break at the same time. If doing so, it may not operate normally.

- In the area where the MAP setting is EXTERNAL, software breaks cannot be used.

### Note on BRK Instruction:

- BRK instruction cannot be used.

## IMPORTANT

### Note on NMI\* Input:

- NMI\* input from the target system is accepted only while a user program is being executed (only while the RUN status LED on the PC4701's front panel is lit).

### Note on HOLD\* Input:

- Be sure to input "L" to the HOLD\* pin of the target system during the user program executing. Inputting "L" to the HOLD pin when stopping the user program or when run-time debugging may cause a malfunction of the emulator.

### Notes on Address Match Interrupt:

- Do not set software breaks at the same addresses as address-match interrupts as the program may run out of control.

- Do not set a hardware break within 4 instructions before an address at which an address-match interrupt occurs. If you do set a hardware break in this range, the program will run out of control.

- When an address at which an address-match interrupt occurs is executed in one-step mode, the program stops after executing the first instruction after returning from the address-match interrupt processing.

### Note on Software Reset:

- Do not use a software reset.

### Note on Protect Resistor (PRC2):

- Make note of the fact that the protect is not canceled when protect register (PRC2), which enables writing in the port P9 direction register and the SI/O3, 4 control register, is changed with the below procedure.

- (1) Step execution of the "instruction for setting ("1") PRC2"

- (2) Setting the break point from the "instruction for setting ("1") PRC2" to when the "setting the register for the protect"

- (3) Setting "("1") PRC2" from the dump window or script window

### Note on Pullup Control Resistor:

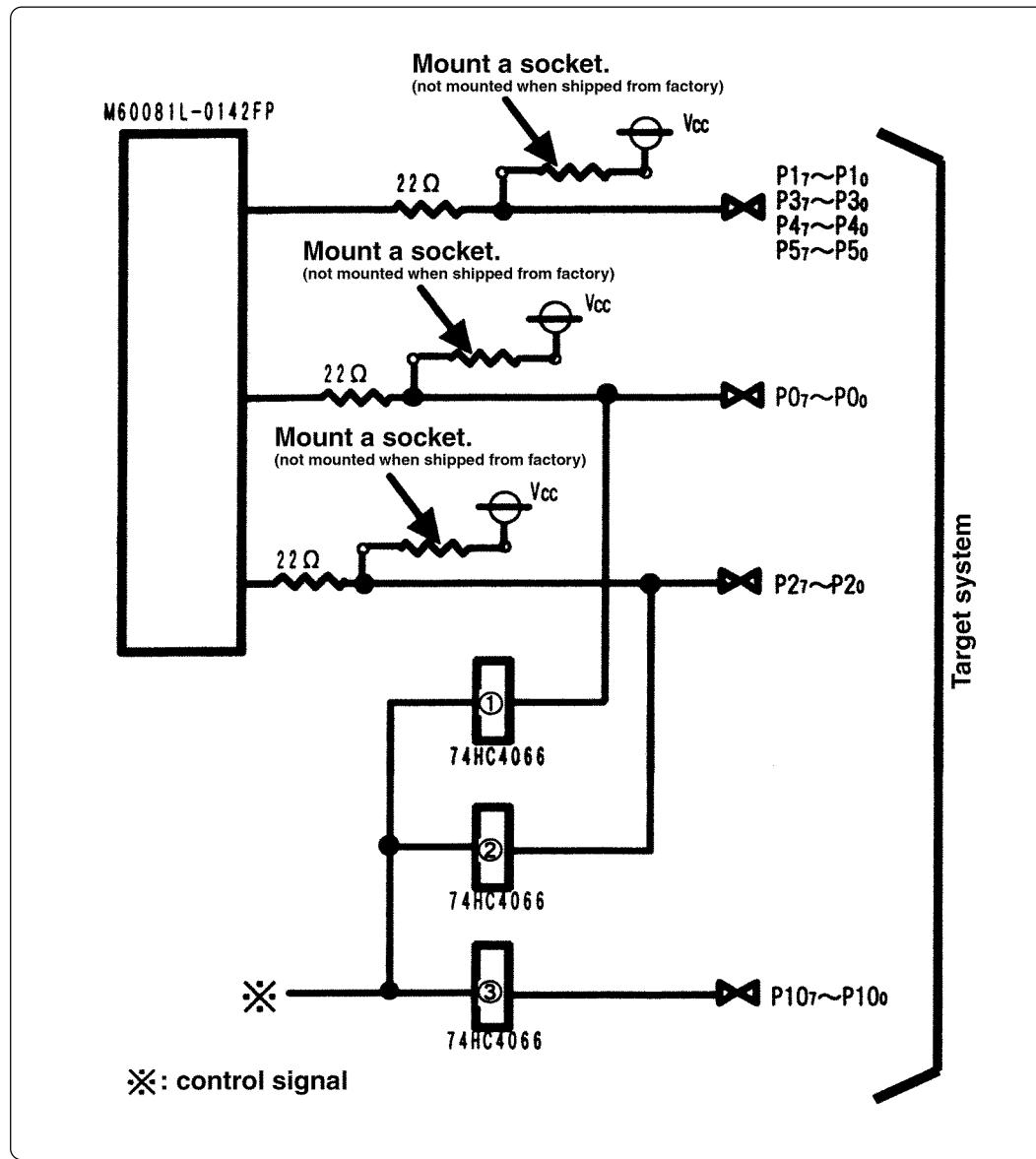

- Ports P0<sub>0</sub> to P5<sub>7</sub> are not pulled up by the pullup control resistor.

When pulling up the ports P0<sub>0</sub> to P5<sub>7</sub>, apply a resistance to the inside of the emulator. How to apply it, refer to "3.2 Setting Switches and Pullup Resistor" (page 25).

Note: Ports P6<sub>0</sub> to P10<sub>0</sub> are pulled up by the pullup control resistor.

Note: Pullup control resistor can read and write from P0<sub>0</sub> to P10<sub>0</sub> properly.

## IMPORTANT

### Note on Differences between Actual MCU and Emulator:

- Operations of the emulator differs from those of mask MCUs as listed below.

#### (1) Reset condition

Set the time for starting up (0.2 Vcc to 0.8 Vcc) 1  $\mu$ s or less.

#### (2) Data values of ROM area at power-on

(3) Internal memories (RAM and ROM) capacities etc.

#### (4) Characteristics of ports P0<sub>0</sub> to P5<sub>7</sub>

Ports P0<sub>0</sub> to P5<sub>7</sub> are connected via emulation circuits. The device used for the port emulation circuit is;

Device: M60081L-0142FP

#### (5) HOLD\* control

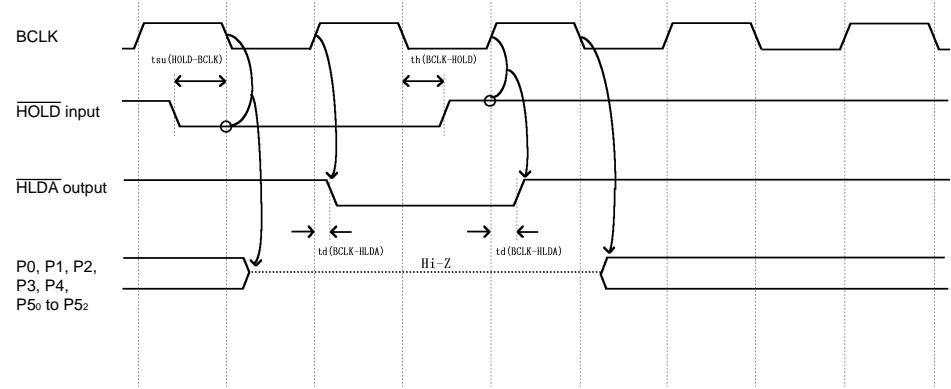

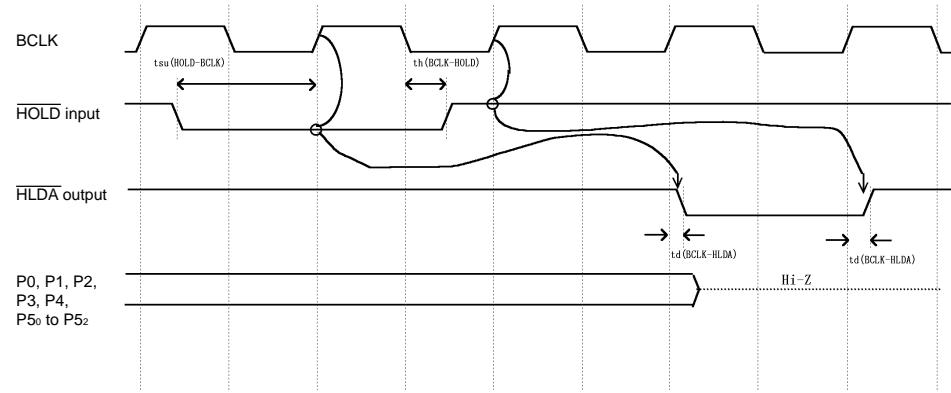

When inputting "Low" to the HOLD\* pin to run into the HOLD state, P0<sub>0</sub> to P5<sub>2</sub> will be in the HOLD state delaying by 2.5 cycles than the actual MCU (see Table 5.5, Figure 5.5, Table 5.9 and Figure 5.10).

#### (6) A-D input group selection function

To use the A-D input group selection function, following settings are required.

##### 1) To select A-D input for port P0

- Set the whole 8-bit direction registers of P10<sub>7</sub> to P10<sub>0</sub> to input.

- Set P10<sub>7</sub> to P10<sub>0</sub> to no pullup for pullup control register setting.

- P10<sub>7</sub> to P10<sub>0</sub> cannot be used for the input pins of I/O port and key input interrupt functions.

##### 2) To select A-D input for port P2

- Set the whole 8-bit direction registers of P10<sub>7</sub> to P10<sub>0</sub> to input.

- Set P10<sub>7</sub> to P10<sub>0</sub> to no pullup for pullup control register setting.

- P10<sub>7</sub> to P10<sub>0</sub> cannot be used for the input pins of I/O port and key input interrupt functions.

##### 3) To select A-D input for port P10

- There is no limitation.

As a flexible cable, a pitch converter board and other devices are used between the evaluation MCU and the target system, some characteristics are slightly different from those of the actual MCU. Therefore, be sure to evaluate your system with an evaluation MCU. Before starting mask production, evaluate your system and make final confirmation with an ES (Engineering Sample) version MCU.

# IMPORTANT

(7) Output of the actual MCU and this product

Table 1.1 Differences of outputs between actual MCU and this product (when executing program)

| Access area                  | Signal       | Actual MCU                                            | This product                                          | * for difference |

|------------------------------|--------------|-------------------------------------------------------|-------------------------------------------------------|------------------|

| SFR area<br>(MAP = EXT)      | Address BHE* | Outputs                                               | Outputs                                               |                  |

|                              | Data         | Outputs<br>(floating during read operating)           | Outputs<br>(floating during read operating)           |                  |

|                              | RD*<br>WR*   | Outputs<br>(Low at write cycle,<br>Low at read cycle) | Outputs<br>(Low at write cycle,<br>Low at read cycle) |                  |

|                              | CS*          | Does not output<br>(fixed to High output)             | Does not output<br>(fixed to High output)             |                  |

|                              | ALE          | Does not output<br>(fixed to Low output)              | Outputs                                               | *                |

| Internal RAM<br>Internal ROM | Address BHE* | Retains previous status                               | Outputs                                               | *                |

|                              | Data         | Floating                                              | Floating                                              |                  |

|                              | RD*<br>WR*   | Does not output<br>(fixed to High output)             | Does not output<br>(fixed to High output)             |                  |

|                              | CS*          | Does not output<br>(fixed to High output)             | Does not output<br>(fixed to High output)             |                  |

|                              | ALE          | Does not output<br>(fixed to Low output)              | Outputs                                               | *                |

| External area                | Address BHE* | Outputs                                               | Outputs                                               |                  |

|                              | Data         | Outputs<br>(inputs external data at read cycle)       | Outputs<br>(inputs external data at read cycle)       |                  |

|                              | RD*<br>WR*   | Outputs<br>(Low at write cycle,<br>Low at read cycle) | Outputs<br>(Low at write cycle,<br>Low at read cycle) |                  |

|                              | CS*          | Outputs                                               | Outputs                                               |                  |

|                              | ALE          | Outputs                                               | Outputs                                               |                  |

Table 1.2 Differences of outputs between actual MCU and this product (when stopping program)

| Access area | Signal       | Actual MCU | This product                                      | * for difference |

|-------------|--------------|------------|---------------------------------------------------|------------------|

|             | Address BHE* |            | Outputs                                           |                  |

|             | Data         |            | Floating                                          |                  |

|             | RD*<br>WR*   |            | Outputs RD* only<br>(WR* is fixed to High output) |                  |

|             | CS*          |            | Outputs                                           |                  |

|             | ALE          |            | Outputs                                           |                  |

# IMPORTANT

Table 1.3 Differences of outputs between actual MCU and this product (in stop mode)

| Access area | Signal       | Actual MCU                                | This product                              | * for difference |

|-------------|--------------|-------------------------------------------|-------------------------------------------|------------------|

|             | Address BHE* | Retains previous status                   | Retains previous status                   |                  |

|             | Data         | Retains previous status                   | Floating                                  | *                |

|             | RD*<br>WR*   | Does not output<br>(fixed to High output) | Does not output<br>(fixed to High output) |                  |

|             | CS*          | Retains previous status                   | Retains previous status                   |                  |

|             | ALE          | Does not output<br>(fixed to High output) | Does not output<br>(fixed to High output) |                  |

Table 1.4 Differences of outputs between actual MCU and this product (in wait mode)

| Access area | Signal       | Actual MCU                                | This product                              | * for difference |

|-------------|--------------|-------------------------------------------|-------------------------------------------|------------------|

|             | Address BHE* | Retains previous status                   | Retains previous status                   |                  |

|             | Data         | Retains previous status                   | Floating                                  | *                |

|             | RD*<br>WR*   | Does not output<br>(fixed to High output) | Does not output<br>(fixed to High output) |                  |

|             | CS*          | Retains previous status                   | Retains previous status                   |                  |

|             | ALE          | Does not output<br>(fixed to High output) | Does not output<br>(fixed to High output) |                  |

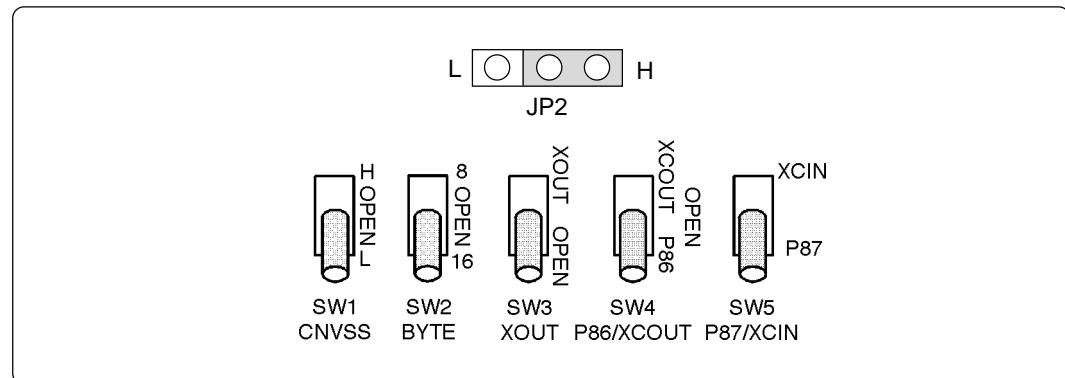

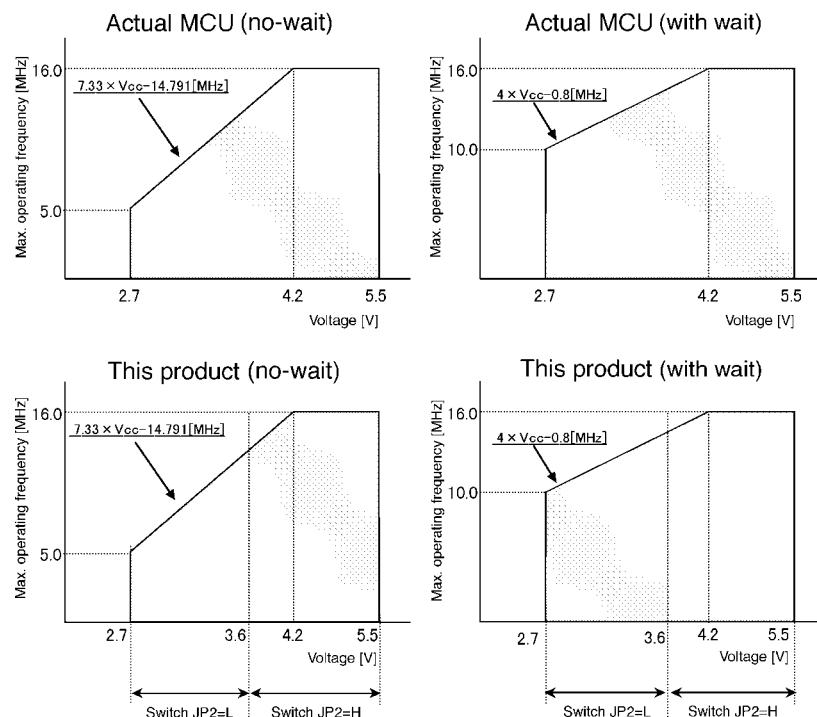

## Note on Switch Settings According to Operation Voltage:

- With this product, you need to change the switch setting according to the operation voltage. Change the setting as described below. For details, see "3.2 Setting Switches and Pullup Resistor" (page 25).

|     |                                                                                                                     |                                                                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

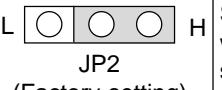

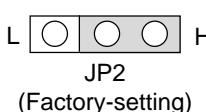

| JP2 | L  H<br>JP2<br>(Factory-setting) | Set when using at the range of the target voltage within +3.6 to +5.5 V or not connecting the target system. |

|     | L  H<br>JP2                      | Set when using at the range of the target voltage within +2.7 to +3.6 V.                                     |

# Chapter 2. Preparation

This chapter describes the package components, the system configuration and the preparation for using this product for the first time.

|                                                        |    |

|--------------------------------------------------------|----|

| 2.1 Terminology .....                                  | 18 |

| 2.2 Package Components .....                           | 19 |

| 2.3 Other Tool Products Required for Development ..... | 19 |

| 2.4 Name of Each Part .....                            | 20 |

| (1) System Configuration .....                         | 20 |

| (2) Inside of Emulation Pod .....                      | 21 |

| 2.5 When Using the Emulator for the First Time .....   | 22 |

# Chapter 2. Preparation

## 2.1 Terminology

Some specific words used in this user's manual are defined as follows:

### **Emulator system**

This means an emulator system built around the PC4701 emulator. The PC4701 emulator system is configured with an emulator main unit, emulation pod, host machine and emulator debugger.

### **Emulator main unit (Hereafter PC4701)**

This means a generic name for PC4701M, PC4701HS and PC4701L emulators for 8 and 16-bit MCUs.

### **Emulation pod**

This means M30620T2-RPD-E (this product). This emulation pod is for M16C/62 and 62A Group MCUs.

### **Host machine**

This means a personal computer used to control the emulator and emulation pod.

### **Emulator debugger**

This means a software tool M3T-PD30 to control the emulator from the host machine through an interface.

### **Firmware**

Program that analyzes contents of communication with the emulator debugger and controls the emulator hardware. This program is installed in the EEPROM. This program is downloadable from the emulator debugger to upgrade the firmware or to support other MCUs.

### **Evaluation MCU**

This means the microcomputer mounted on the emulation pod which is operated in the specific mode for tools.

### **Target MCU**

This means the microcomputer you are going to debug.

### **Target system**

This means a user's application system using the microcomputer to be debugged.

\*

In this user's manual, this symbol is used to show active LOW. (e.g. RESET\*: Reset signal)

## 2.2 Package Components

The M30620T2-RPD-E package consists of the following items. When unpacking, check to see if your M30620T2-RPD-E contains all of these items.

| Item                                                                                        | Quantity |

|---------------------------------------------------------------------------------------------|----------|

| M30620T2-RPD-E emulation pod main unit                                                      | 1        |

| FLX120-RPD flexible cable for connecting PC4701                                             | 1        |

| FLX100 flexible cable for connecting pitch converter board (pre-installed in emulation pod) | 1        |

| FLX-100LCC pitch converter board for connecting target system                               | 1        |

| OSC-3 (16 MHz) oscillator circuit board (pre-installed in emulation pod)                    | 1        |

| OSC-2 oscillator circuit board                                                              | 1        |

| Resistor arrays for pulling up ports P0 <sub>0</sub> to P5 <sub>7</sub> (51 kΩ)             | 12       |

| Hardware tool user registration FAX sheet (English)                                         | 1        |

| Hardware tool user registration FAX sheet (Japanese)                                        | 1        |

| M30620T2-RPD-E user's manual (this manual)                                                  | 1        |

| M30620T2-RPD-E user's manual (Japanese)                                                     | 1        |

Please keep the M30620T2-RPD-E's packing box and cushion material in your place for reuse at a later time when sending your product for repair or other purposes. Always use these packing box and cushion material when transporting this product.

If any of these items are missing or found faulty, please contact your local distributor. Also, if there is any question or doubt about the packaged product, contact your local distributor.

## 2.3 Other Tool Products Required for Development

To bring forward programs development on the M16C/62 and 62A Group MCUs, the products listed below are necessary in addition to those contained package above. Get them separately.

|                                               |                                                                                                                                 |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Emulator main unit                            | PC4701M, PC4701HS or PC4701L                                                                                                    |

| Emulator debugger                             | M3T-PD30                                                                                                                        |

| Converter board<br>(Required for 80-pin MCUs) | FLX-DIRECT613 + DIRECT80S<br>or<br>100LCC-80QSB<br><i>see Figure 3.11 Connecting emulation pod and target systems (page 35)</i> |

To purchase these products, contact your nearest distributor.

## 2.4 Name of Each Part

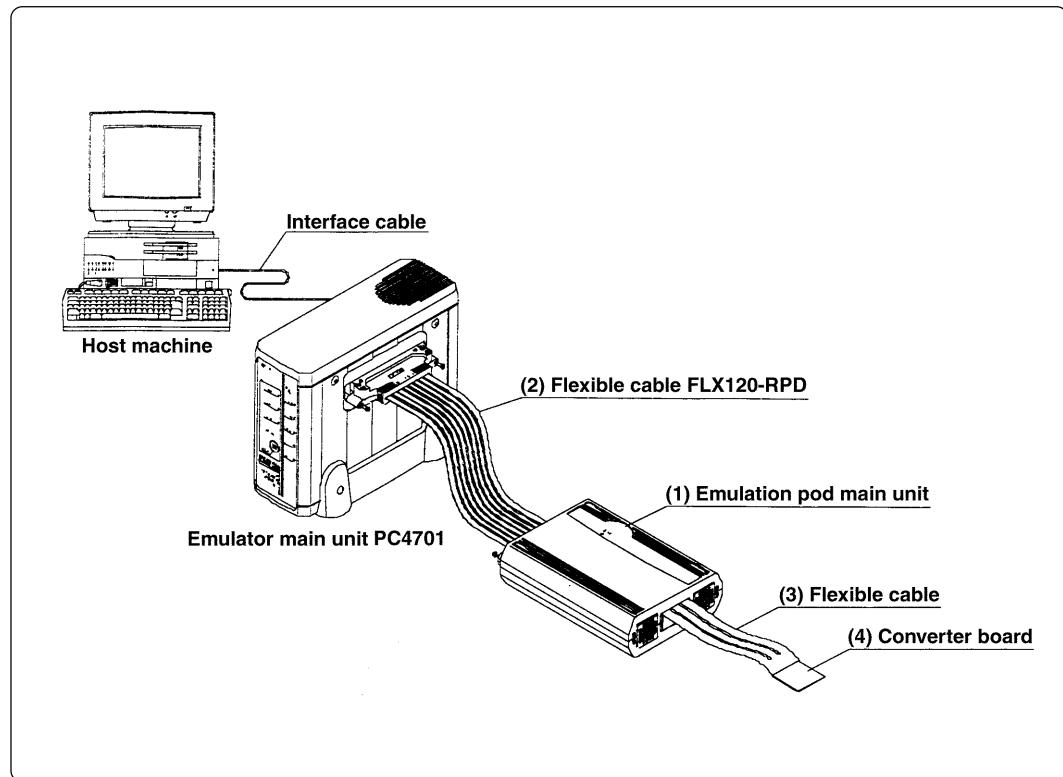

### (1) System Configuration

Figure 2.1 System configuration

(1) to (4) in Figure 2.1 are included with this product package.

#### (1) Emulation pod (M30620T2-RPD-E)

This emulation pod contains an evaluation MCU, emulation memory and circuit to feature the debugging function.

#### (2) Flexible cable (FLX120-RPD)

This is a 120-pin flexible cable for connecting the PC4701 emulator and the emulation pod.

#### (3) Flexible cable (FLX100)

This is a 100-pin flexible cable for connecting the emulation pod and the target system.

#### (4) Pitch converter board

This is a pitch converter board for connecting to the target system. For details, refer to "3.5 Connecting the Target System" (page 35).

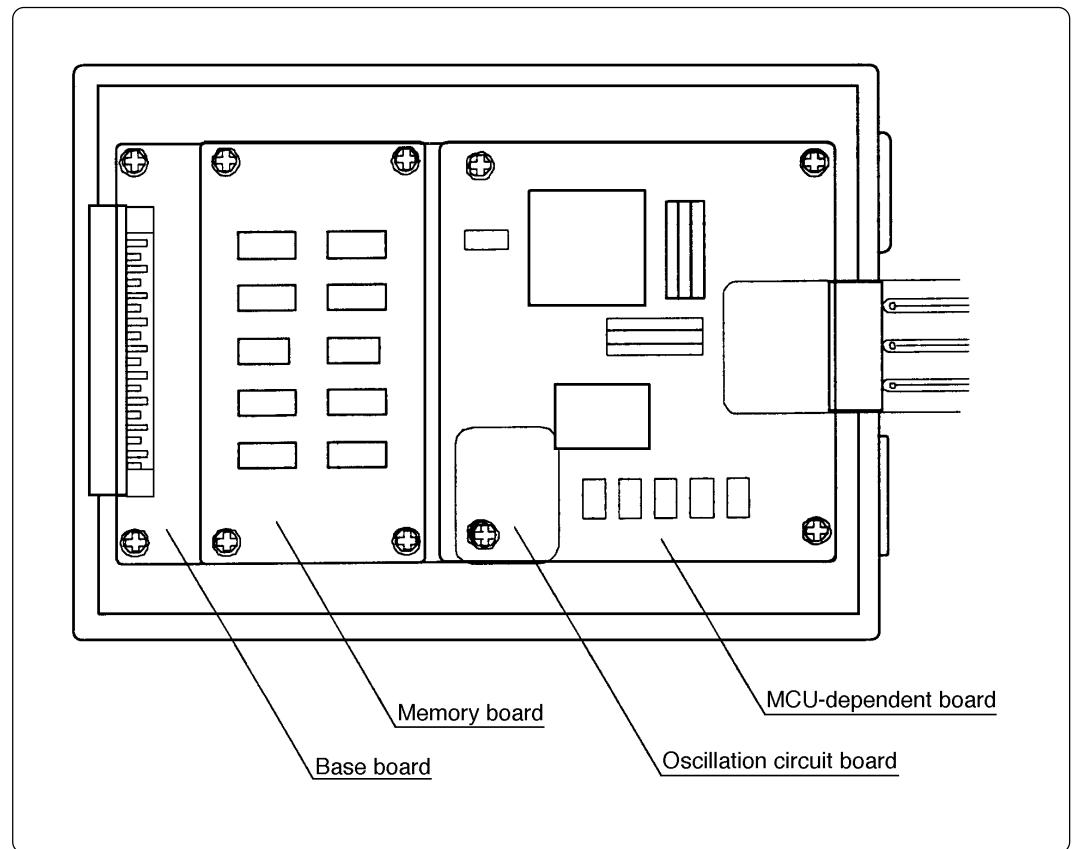

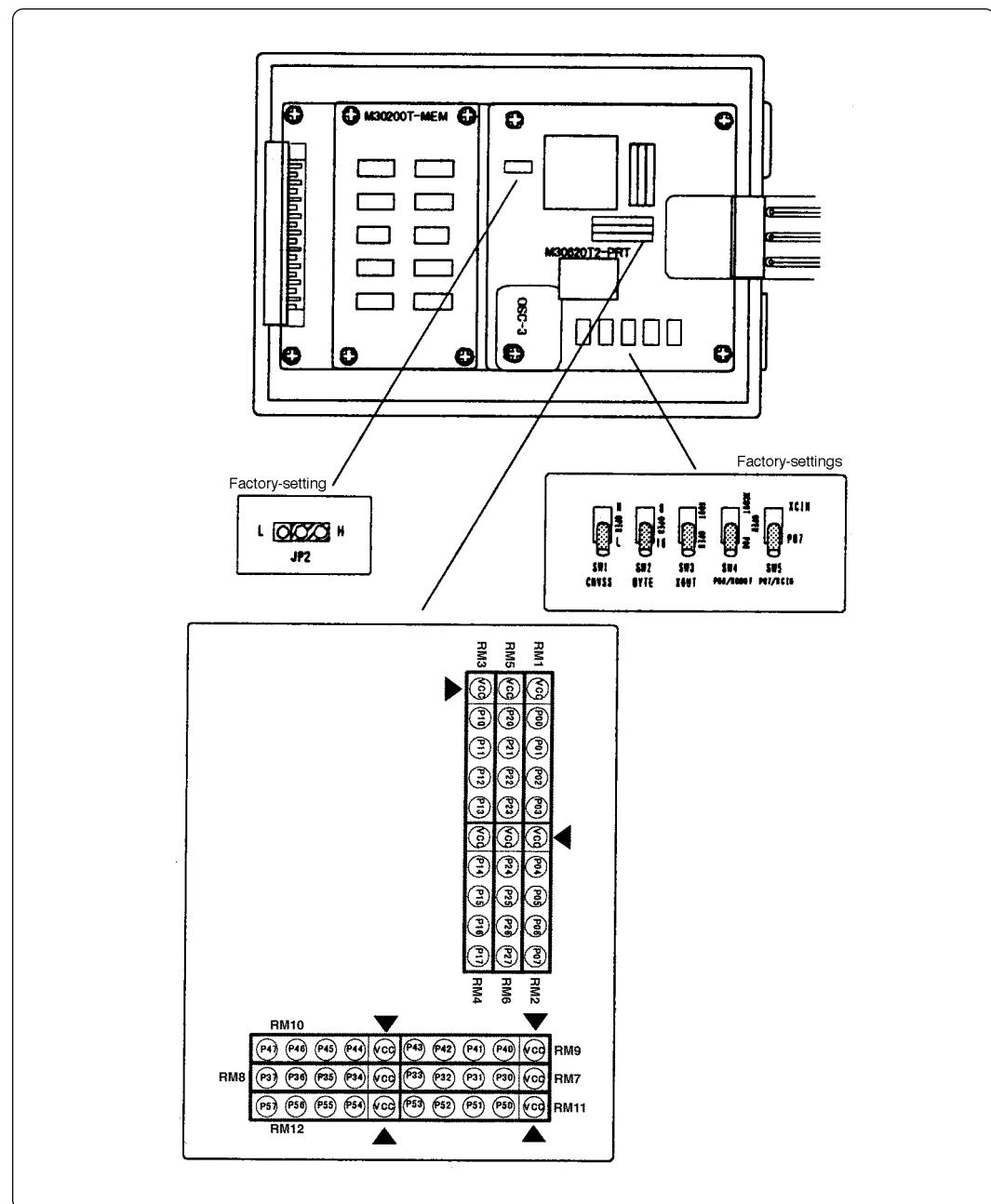

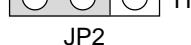

## (2) Inside of Emulation Pod

Figure 2.2 Internal view of emulation pod

### (1) MCU-dependent board

Board which groups parts (pins and added functions) which vary according to MCU model.

### (2) Base board

Board for the M16C/60 and M16C/20 Series MCUs which controls the interface with the PC4701 and the evaluation MCU.

### (3) Memory board

Board on which is mounted the emulation memory (1 MB) and the map memory (4 bit  $\times$  1 M) for the M16C/60 and M16C/20 Series MCUs.

### (4) Oscillation circuit board

Oscillator circuit board on which the oscillation module device is mounted (16.000 MHz).

It is planned to enable customers to use future M16C/62 and 62A Group models by changing the MCU-dependent board and MCU board.

## 2.5 When Using the Emulator for the First Time

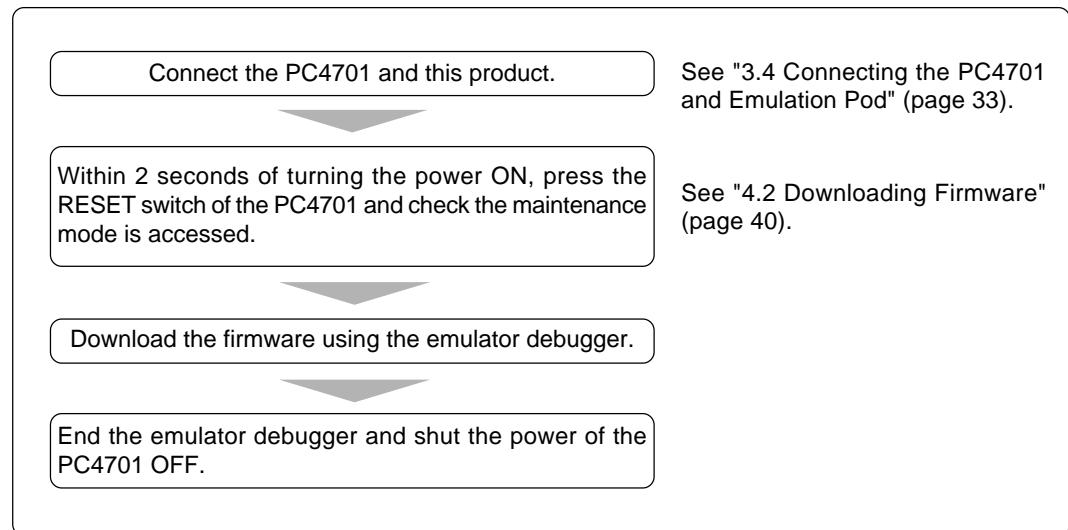

If you have purchased this emulation pod newly, it is necessary to download the firmware. The download procedure is given in Figure 2.3.

Before attempting to download the firmware, check the emulator debugger is installed and the emulator is connected to the host machine. For more information, see each user's manual of the emulator debugger and the PC4701.

*Figure 2.3 Firmware download procedure when emulator is used for the first time*

To make sure the emulation pod works properly, run the self-check. For self-check procedures, see "4.3 Self-check" (page 41).

# Chapter 3. Setting Up

This chapter describes switch settings required for using this product and how to connect this product to the PC4701 and the target system.

|     |                                                                     |    |

|-----|---------------------------------------------------------------------|----|

| 3.1 | Removing the Upper Cover .....                                      | 24 |

| 3.2 | Setting Switches and Pullup Resistor .....                          | 25 |

| 3.3 | Selecting Clock Supply .....                                        | 29 |

|     | (1) Using the Oscillator Circuit on Target System .....             | 30 |

|     | (2) Changing the Internal Oscillator Circuit of Emulation Pod ..... | 31 |

|     | (3) Replacing the Oscillator Circuit Boards .....                   | 32 |

| 3.4 | Connecting the PC4701 and Emulation Pod .....                       | 33 |

|     | (1) Connecting the Cable to the PC4701 .....                        | 33 |

|     | (2) Connecting the Cable to the Emulation Pod .....                 | 34 |

| 3.5 | Connecting the Target System .....                                  | 35 |

# Chapter 3. Setting Up

To use this emulation pod with your target system, it is necessary to set as follows. Set the following after removing the upper cover.

- Change the oscillation frequency.

- Set the X<sub>IN</sub>, X<sub>OUT</sub>, X<sub>CIN</sub> and X<sub>COUT</sub> pins for the target system.

- Set the switches for the operating voltage of the target system.

- Install a pullup resistor to ports P0<sub>0</sub> to P5<sub>7</sub>.

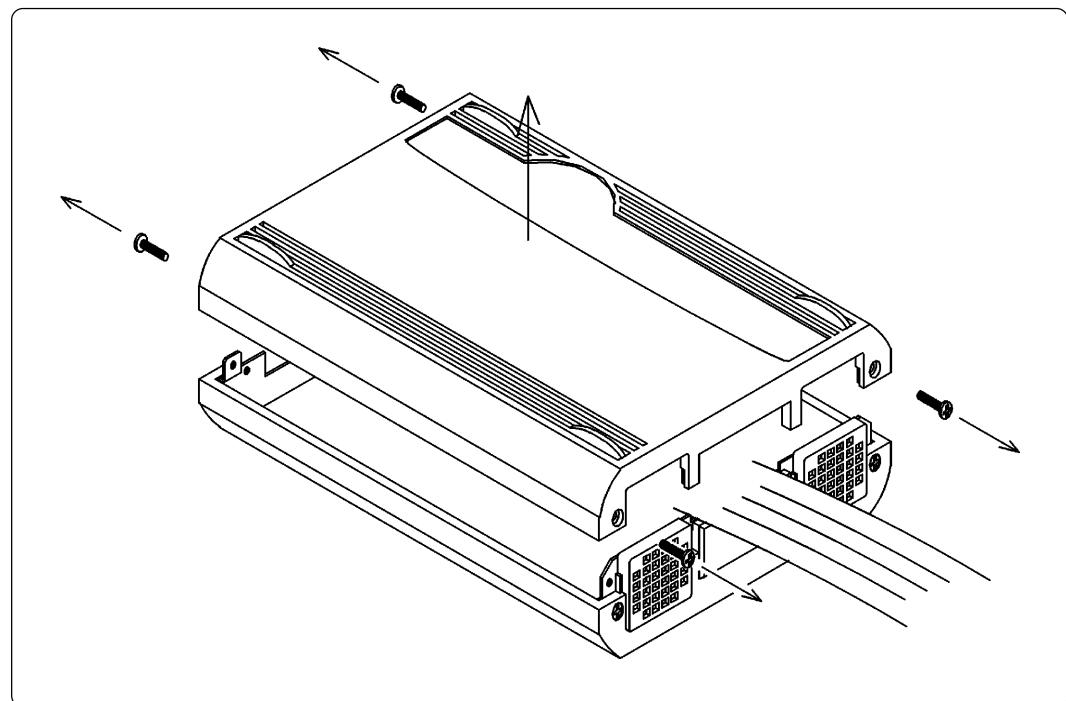

## 3.1 Removing the Upper Cover

The procedure of removing the upper cover is shown below.

- (1) Remove the four screws of both sides of this product and lift off the upper cover. (see Figure 3.1)

- (2) Set the jumper switches.

- (3) Replace the upper cover and secure the four screws.

Figure 3.1 Removing the upper cover

### ⚠ CAUTION

#### When Removing the Upper Cover:

- Always shut OFF power when removing the upper cover or setting the switches.

### 3.2 Setting Switches and Pullup Resistor

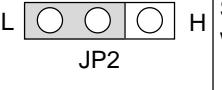

Figure 3.2 shows the positions of switches and a position for installing a pullup resistor. Tables 3.1, 3.2 list how to set each switch and Figure 3.3 shows how to install a pullup resistor.

Figure 3.2 Positions of switches and their factory-settings

Table 3.1 Switch settings of M30620T2-RPD-E (part 1)

| Signal            | Switch | Setting                                           | Description                                                             |

|-------------------|--------|---------------------------------------------------|-------------------------------------------------------------------------|

| CNV <sub>ss</sub> | SW1    | <br>SW1<br>CNV <sub>ss</sub><br>(Factory-setting) | Pulls down the CNV <sub>ss</sub> pin of MCU with a resistance at 33 kΩ. |

|                   |        | <br>SW1<br>CNV <sub>ss</sub>                      | Does not pull down/up the CNV <sub>ss</sub> pin of MCU.                 |

|                   |        | <br>SW1<br>CNV <sub>ss</sub>                      | Pulls up the CNV <sub>ss</sub> pin of MCU with a resistance at 33 kΩ.   |

| BYTE              | SW2    | <br>SW2<br>BYTE<br>(Factory-setting)              | Pulls down the BYTE pin of MCU with a resistance at 33 kΩ.              |

|                   |        | <br>SW2<br>BYTE                                   | Does not pull down/up the BYTE pin of MCU.                              |

|                   |        | <br>SW2<br>BYTE                                   | Pulls up the BYTE pin of MCU with a resistance at 33 kΩ.                |

| X <sub>OUT</sub>  | SW3    | <br>SW3<br>XOUT<br>(Factory-setting)              | Does not connect the X <sub>OUT</sub> pin of MCU to the target system.  |

|                   |        | <br>SW3<br>XOUT                                   | Connects the X <sub>OUT</sub> pin of MCU to the target system.          |

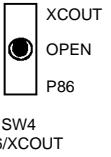

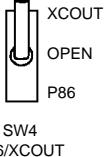

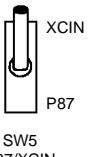

Table 3.2 Switch settings of M30620T2-RPD-E (part 2)

| Signal                 | Switch | Setting                                                                                                                                                                                                    | Description                                                                                                                                             |

|------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| P8 <sub>6</sub> /XCOUT | SW4    | <br>XCOUT<br>OPEN<br>P86<br>SW4<br>P86/XCOUT<br>(Factory-setting)                                                         | Connects the P8 <sub>6</sub> /XCOUT pin of MCU to the target system. (Uses P8 <sub>6</sub> /XCOUT pin as port P8 <sub>6</sub> )                         |

|                        |        | <br>XCOUT<br>OPEN<br>P86<br>SW4<br>P86/XCOUT                                                                              | Does not connect the P8 <sub>6</sub> /XCOUT pin of MCU. (Uses P8 <sub>6</sub> /XCOUT pin as XCOUT and opens XCOUT.)                                     |

|                        |        | <br>XCOUT<br>OPEN<br>P86<br>SW4<br>P86/XCOUT                                                                              | Connects the P8 <sub>6</sub> /XCOUT pin of MCU to the target system. (Uses P8 <sub>6</sub> /XCOUT pin as XCOUT and connect XCOUT to the target system.) |

| P8 <sub>7</sub> /XCIN  | SW5    | <br>XCIN<br>OPEN<br>P87<br>SW5<br>P87/XCIN<br>(Factory-setting)                                                           | Connects the P8 <sub>7</sub> /XCIN pin of MCU to the target system. (Uses P8 <sub>7</sub> /XCIN pin as port P8 <sub>7</sub> )                           |

|                        |        | <br>XCIN<br>OPEN<br>P87<br>SW5<br>P87/XCIN                                                                              | Uses P8 <sub>7</sub> /XCIN pin as XCIN.                                                                                                                 |

|                        | JP2    | <br>L  H<br>JP2<br>(Factory-setting) | Set when using at the range of the target voltage within +3.6 to +5.5 V or not connecting the target system.                                            |

|                        |        | <br>L  H<br>JP2                      | Set when using at the range of the target voltage within +2.7 to +3.6 V.                                                                                |

It is not possible to control the pullup by the pullup control resistor of ports P0<sub>0</sub> to P5<sub>7</sub> (possible to read and write by the pullup control resistor).

However, as this product has a socket for installing the pullup resistor, it is possible to pull up by mounting the resistor array included with this product. Figure 3.3 shows the positions for installing the pullup resistor.

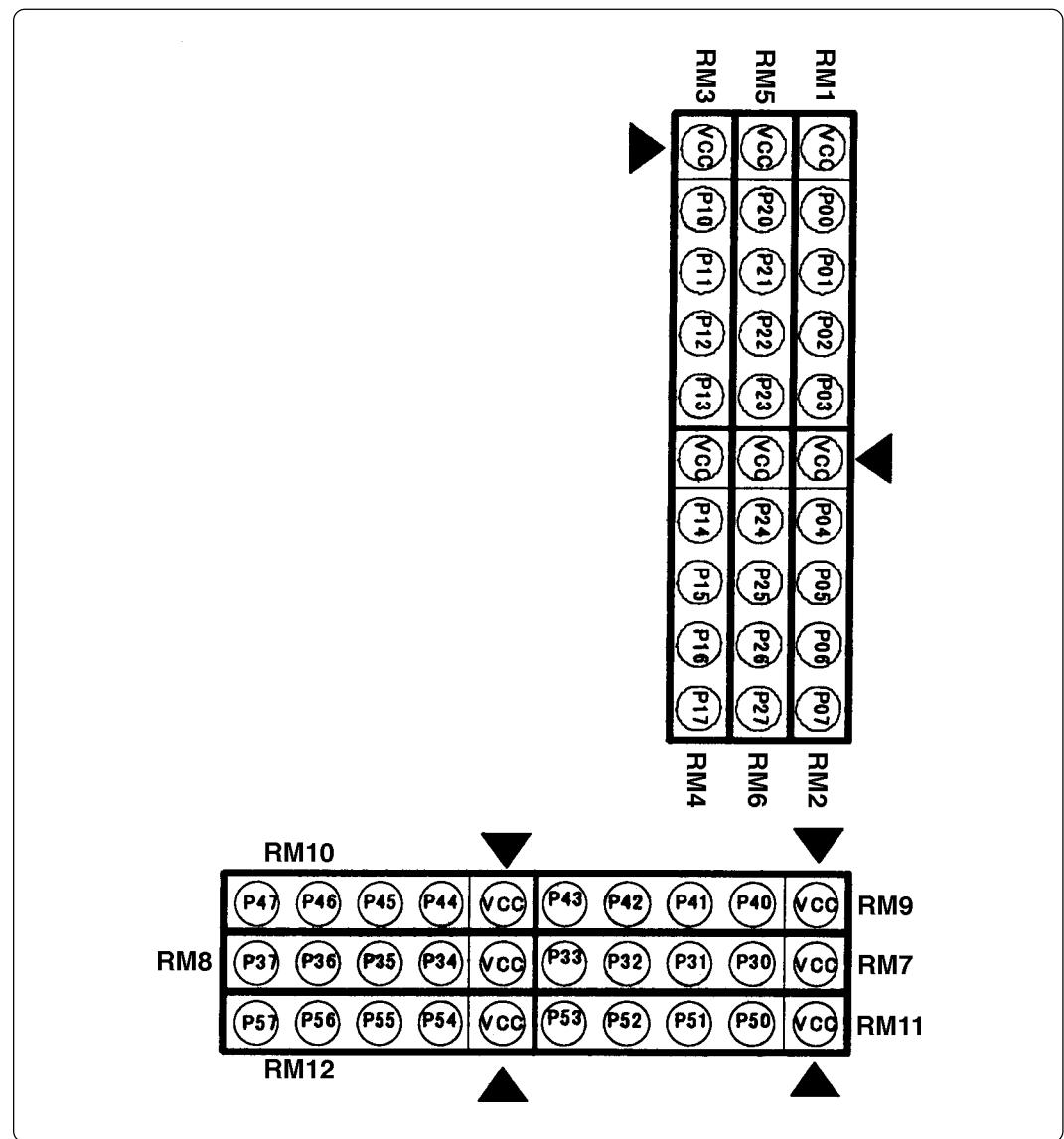

Figure 3.3 Positions for installing the pullup resistor

### 3.3 Selecting Clock Supply

There are two ways to supply a clock to the MCU, using the oscillator circuit of the emulation pod or using the oscillator circuit on the target system. Table 3.3 lists the factory-settings of each clock supply.

*Table 3.3 Clock supply to the MCU*

| Clock                               | Description                                                  | Display of emulator debugger | Default setting |

|-------------------------------------|--------------------------------------------------------------|------------------------------|-----------------|

| X <sub>IN</sub> -X <sub>OUT</sub>   | Internal oscillator circuit of emulation pod (OSC-3: 16 MHz) | Internal                     | ○               |

|                                     | Target System                                                | External                     | -               |

| X <sub>CIN</sub> -X <sub>COUT</sub> | Internal oscillator circuit of emulation pod (32.768 kHz)    | Internal                     | ○               |

|                                     | Target System                                                | External                     | -               |

## IMPORTANT

### Notes on Changing the Clock Supply:

- The clock supply can be set by the Init dialog when starting up the emulator debugger or inputting CLK command on the script window.

- For X<sub>CIN</sub>-X<sub>COUT</sub> pins, it is necessary to set switches in the emulation pod. For details, refer to "3.2 Setting Switches and Pullup Resistor" (page 25).

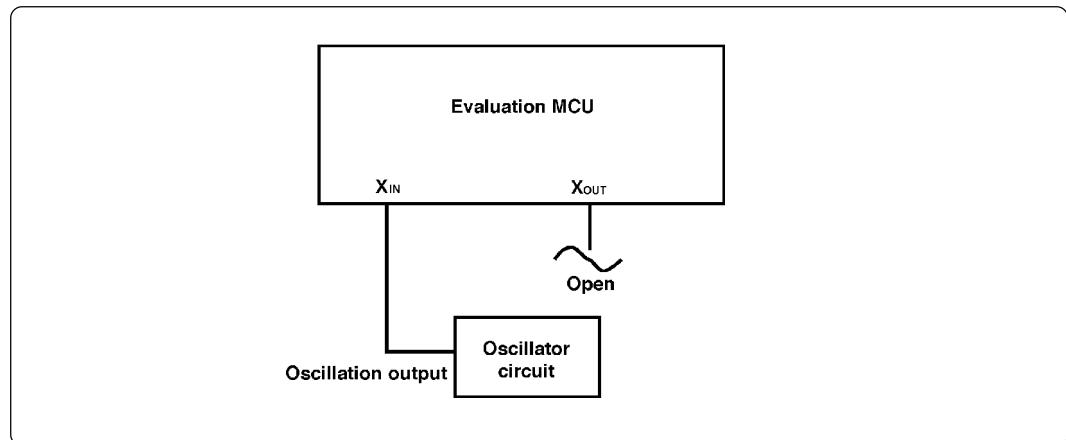

## (1) Using the Oscillator Circuit on Target System

When turning on the power supply, the internal clock of emulation pod is selected to supply the clock to the MCU. To use the external clock on the target system, change the clock by the Init dialog when starting up the emulator debugger or the CLK command on the script window. (For details, refer to the user's manual of the emulator debugger)

Figure 3.4 External oscillator circuit

Figure 3.5 Circuit in which oscillation does not occur (same for  $X_{CIN}$ - $X_{COUT}$ )

## IMPORTANT

### Notes on External Clock:

- To operate the emulation pod with an external clock, construct the oscillator circuit as shown in Figure 3.4 in the target system and input the oscillator output at 50% duty (within the operating range of the evaluation MCU) into the  $X_{IN}$  pin. And the  $X_{OUT}$  pin should be open.

- Make note of the fact that in the oscillator circuit shown in Figure 3.5 where a resonator is connected between the  $X_{IN}$  and  $X_{OUT}$  pins, oscillation does not occur because a flexible cable, buffer IC and other devices are used between the evaluation MCU and the target system. It is same for sub-clock oscillator circuits ( $X_{CIN}$  and  $X_{COUT}$ ).

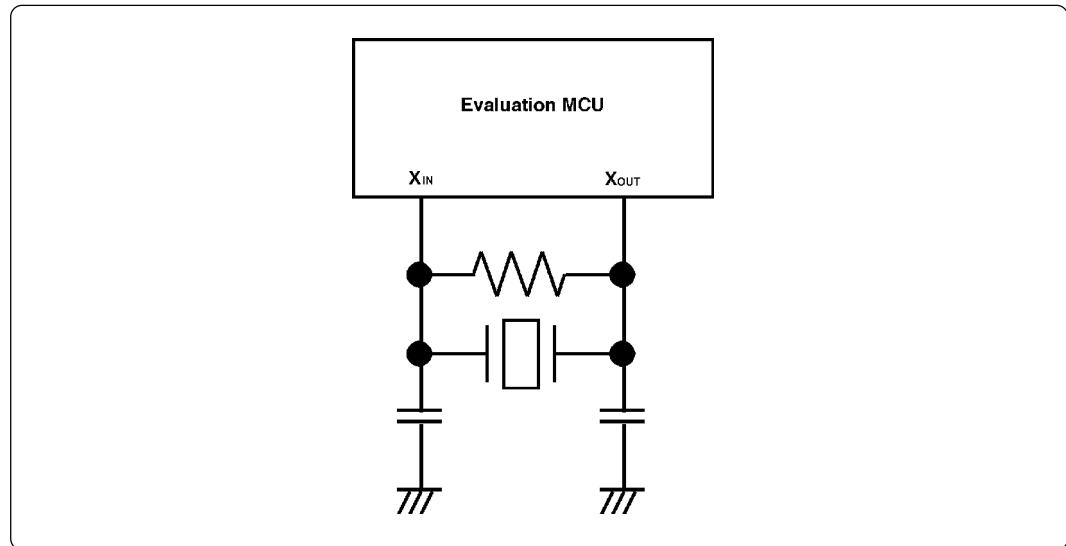

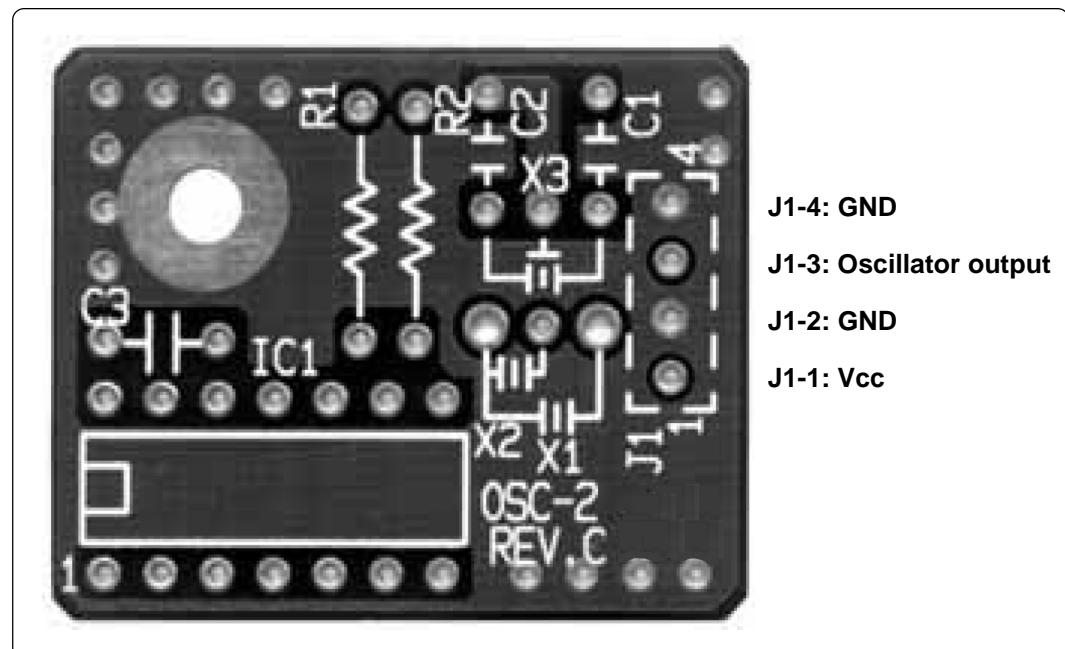

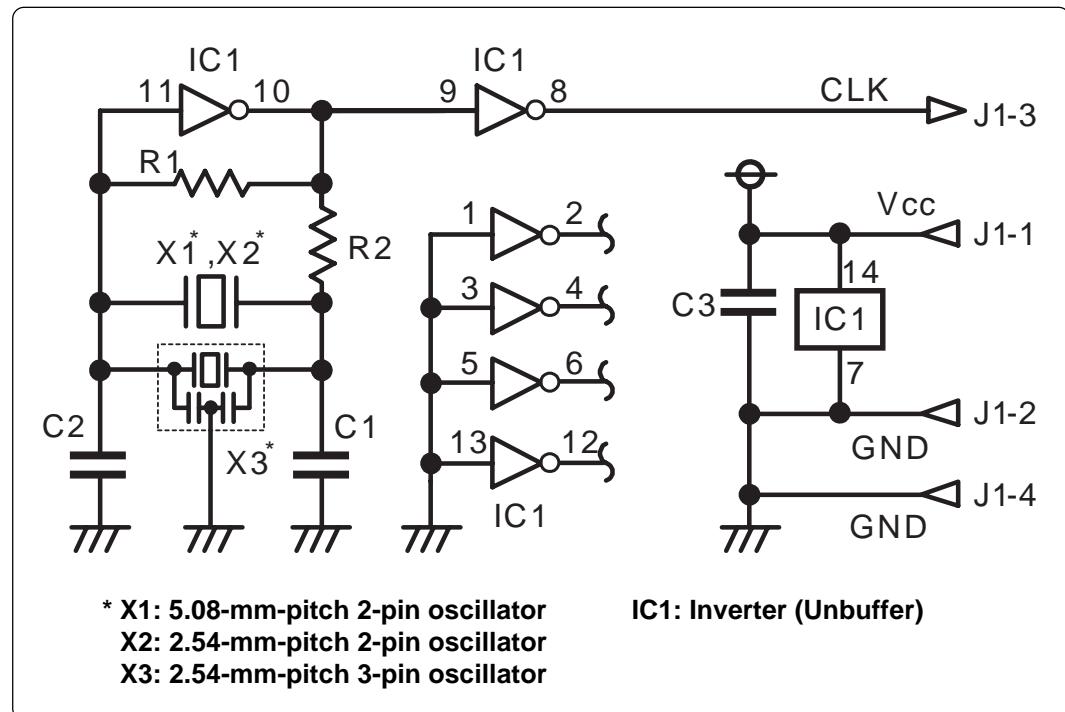

## **(2) Changing the Internal Oscillator Circuit of Emulation Pod**

An oscillator circuit board for 16 MHz is mounted on this product. To use the emulation pod at a frequency other than 16 MHz, build the desired oscillator circuit on the included OSC-2 oscillator circuit board (bare board) and replace the board installed in the emulation pod when shipped from the factory.

Figure 3.6 shows a view of the OSC-2 oscillator circuit board (bare board) and where connector pins are located. Figure 3.7 shows the circuitry of the OSC-2 oscillator circuit board (bare board). Use the number of oscillator circuits recommended by the oscillator manufacturer.

Figure 3.6 External view of oscillator board (OSC-2) and connector pin assignment

Figure 3.7 Circuit of oscillator board (OSC-2)

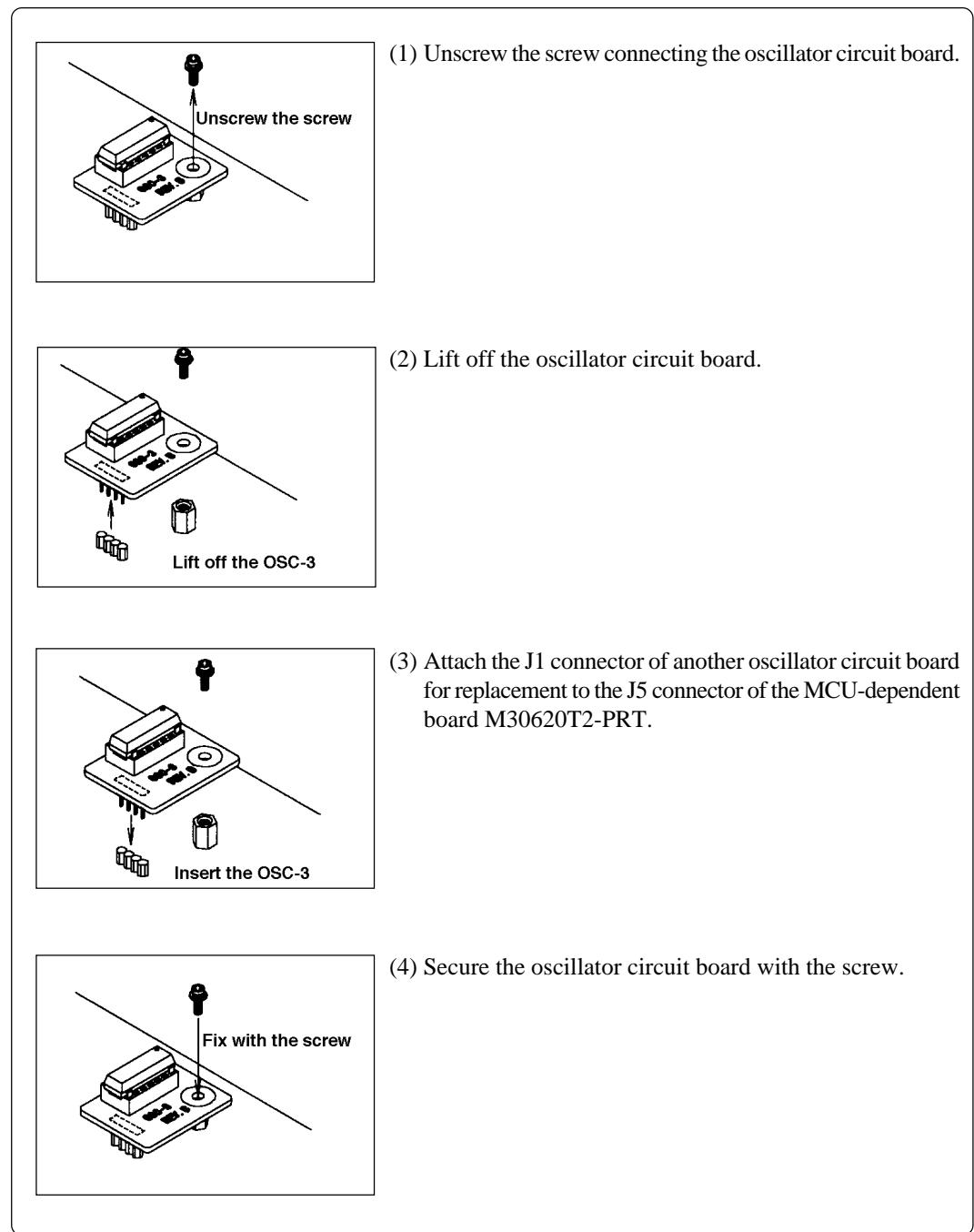

### (3) Replacing the Oscillator Circuit Boards

Figure 3.8 shows how to replace the oscillator circuit boards. For the position of the oscillator circuit board, see Figure 2.2.

Figure 3.8 Replacing the oscillator circuit boards

### 3.4 Connecting the PC4701 and Emulation Pod

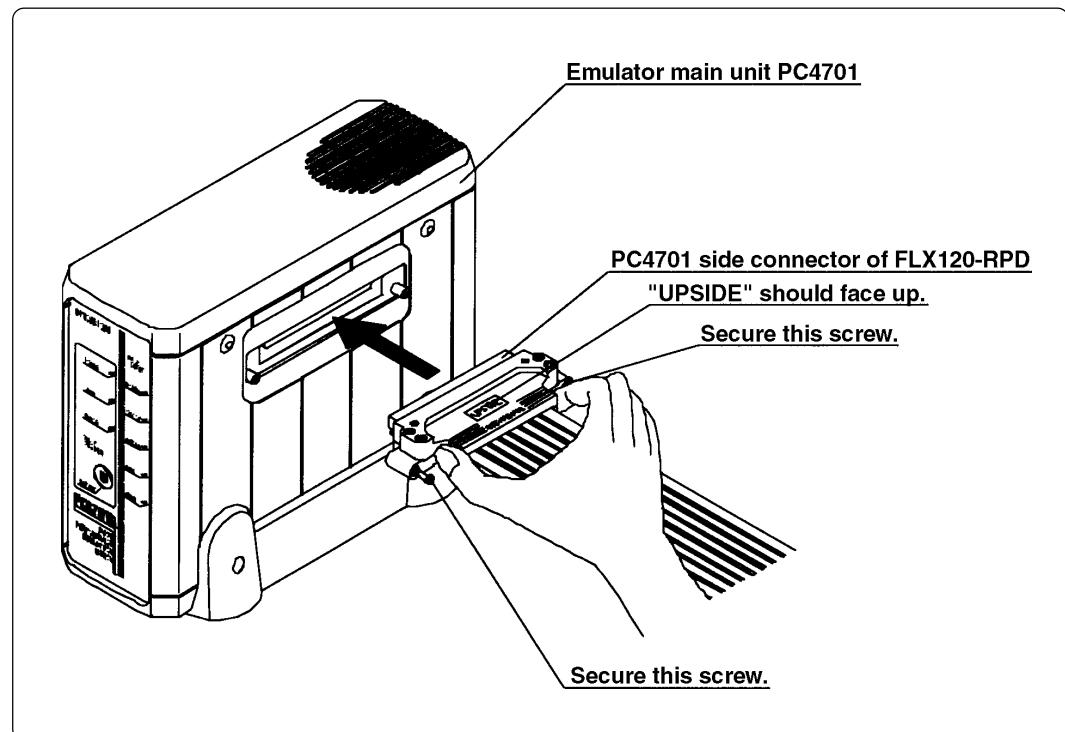

To connect the emulation pod to the PC4701, use the FLX120-RPD 120-pin flexible cable included with this product package. Connect the PC4701 side connector of FLX120-RPD to the cable connector of the PC4701, then secure with screws the FLX120-RPD.

#### (1) Connecting the Cable to the PC4701

Figure 3.9 shows how to connect the PC4701 and FLX120-RPD

Figure 3.9 Connecting PC4701 and FLX120-RPD

#### ⚠ CAUTION

##### Note on Connecting the Cable:

- To connect the FLX120-RPD, be sure to hold the both sides of the PC4701 side connector horizontally with the "UPSIDE" facing up.

- Always shut OFF power before connecting the cable. The power ON state could destroy internal circuits.

##### Note on Securing the Screws:

- After connecting the cable to the emulator main unit PC4701, be sure to secure the screws mounted in both sides of the connector.

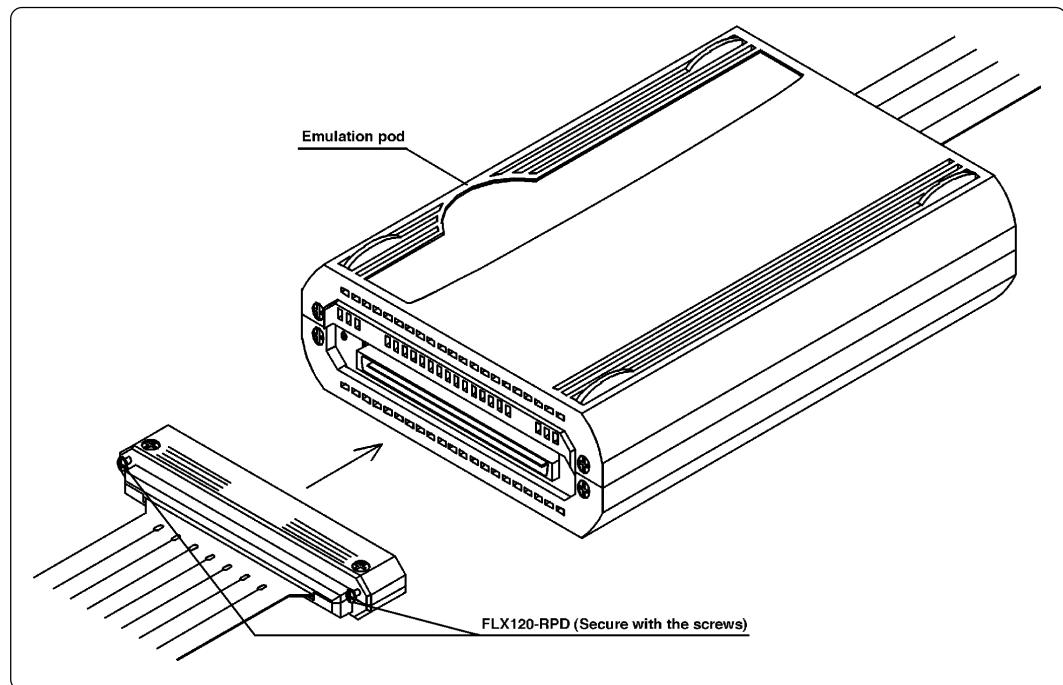

## (2) Connecting the Cable to the Emulation Pod

Figure 3.10 shows how to connect the FLX120-RPD and the emulation pod.

Figure 3.10 Connecting FLX120-RPD and emulation pod

### ! CAUTION

#### Note on Connecting the Cable:

- Always shut OFF power before connecting the cable. The power ON state could destroy internal circuits.

#### Note on Securing the Screws:

- After connecting the cable to the emulation pod, be sure to secure the screws.

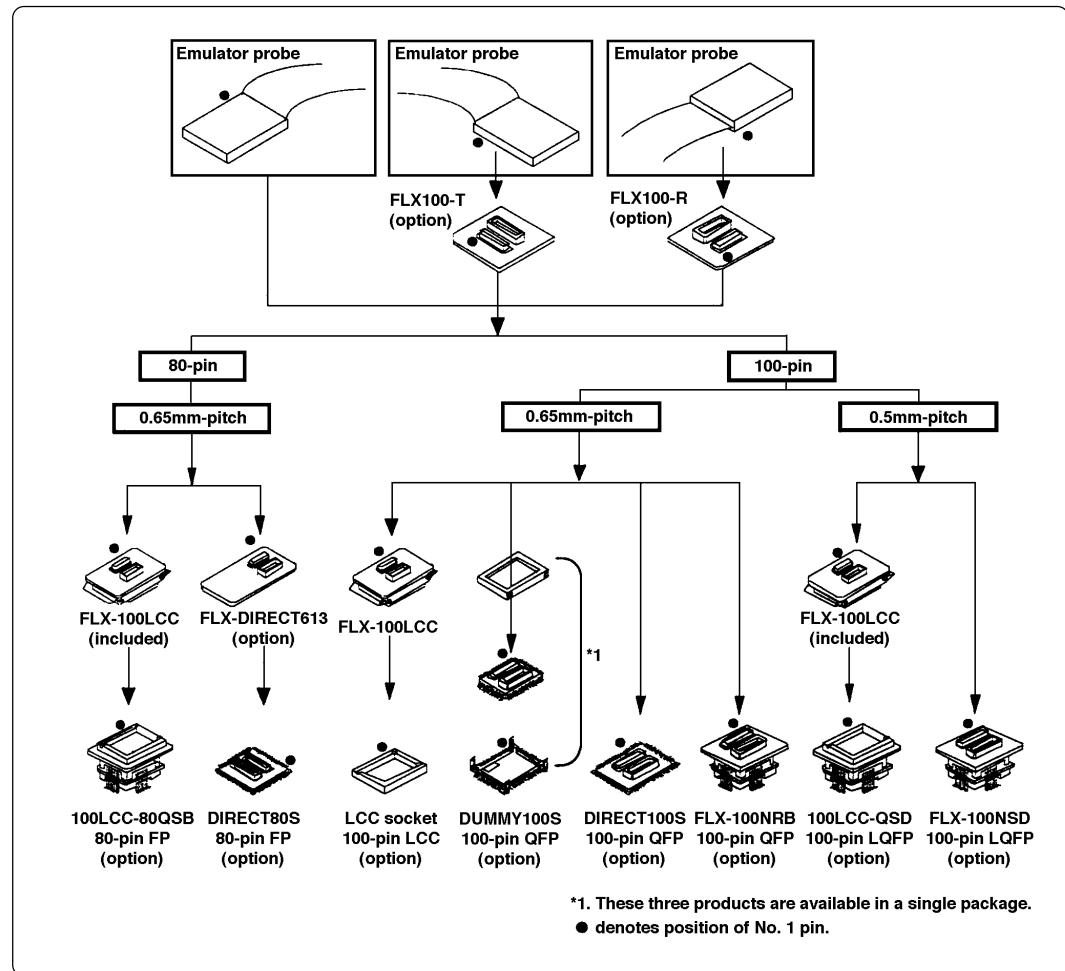

### 3.5 Connecting the Target System

There are eight ways available to connect the emulation pod to target systems as shown in Figure 3.11.

Figure 3.11 Connecting emulation pod and target systems

## ⚠ CAUTION

### Notes on Connecting Target Systems:

- Take care not to attach the converter board in a wrong direction. It may cause a fatal damage to the emulation pod.

- The small connectors of FLX100 and FLX-100LCC are guaranteed for only 20 insertion/removal iterations.

# MEMO

# Chapter 4. Usage

This chapter describes from turning on the power of this product to starting up the emulator debugger.

|     |                                                      |    |

|-----|------------------------------------------------------|----|

| 4.1 | Turning On the Power .....                           | 38 |

| (1) | Checking the Connection of the Emulator System ..... | 38 |

| (2) | Turning On the Power.....                            | 38 |

| (3) | LED Display When PC4701 Starts Up Normally .....     | 39 |

| 4.2 | Downloading Firmware .....                           | 40 |

| (1) | When It is Necessary to Download Firmware .....      | 40 |

| (2) | Downloading Firmware in Maintenance Mode .....       | 40 |

| 4.3 | Self-check .....                                     | 41 |

| (1) | Self-check Procedure .....                           | 41 |

| (2) | If an Error is Detected in the Self-check.....       | 41 |

# Chapter 4. Usage

## 4.1 Turning On the Power

### (1) Checking the Connection of the Emulator System

Before turning the power ON, check the connection of the PC4701, emulation pod, converter board and target system.

### (2) Turning On the Power

Power ON/OFF the target system and the PC4701 as simultaneously as possible.

### CAUTION

#### Notes on Power Supply:

- The emulator's Vcc pin is connected to the target system in order to monitor target system voltage. For this reason, the emulator cannot supply power to the target system. Therefore, provide the target system with a separate power supply from that of the emulator.

- Keep target system power supply voltage within the MCU's specified range.

- Do not change target system power supply voltage after power has been activated.

### (3) LED Display When PC4701 Starts Up Normally

After the emulator starts up, check the status of the LEDs on the front panel to see whether emulation pod operation is enabled or not. Figure 4.1 shows front panel LED lighting status when the emulator is turned ON.

Figure 4.1 LED display when the power turned on

## 4.2 Downloading Firmware

### (1) When It is Necessary to Download Firmware

It is necessary to download firmware when;

- (1) When you use this product for the first time

- (2) When the firmware has been upgraded

- (3) When the emulator debugger has been upgraded

- (4) When you use this product with a PC4701 which was used with other emulation pod before

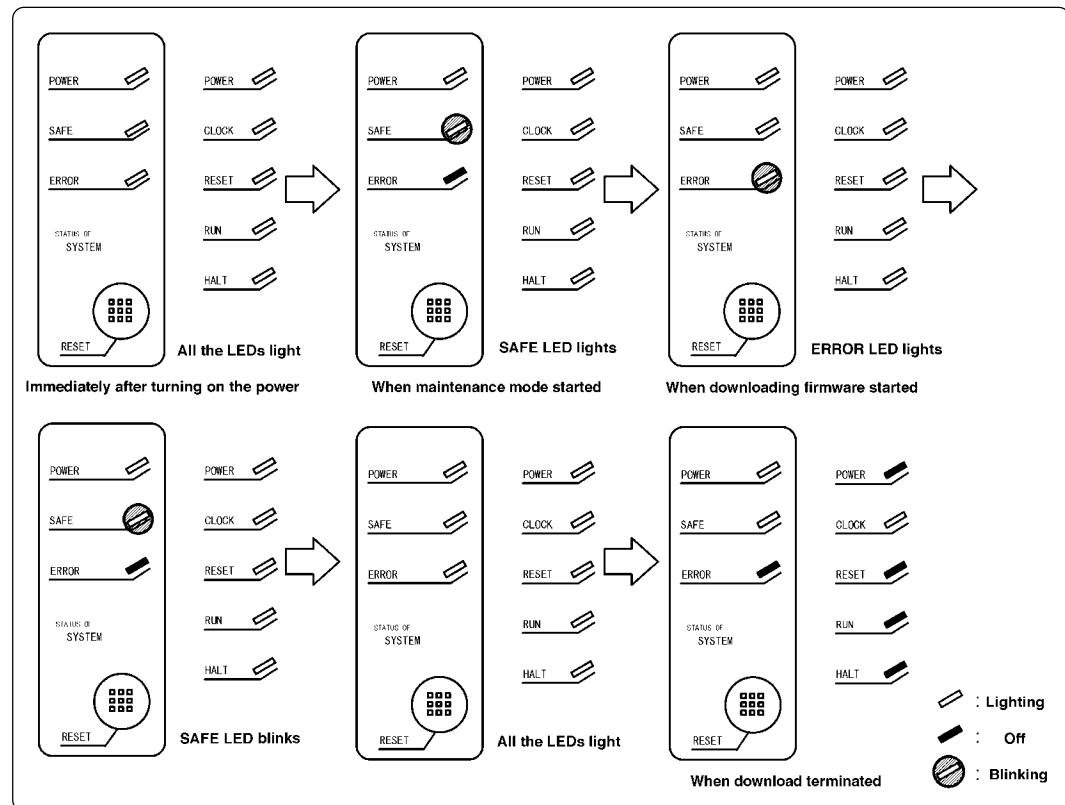

### (2) Downloading Firmware in Maintenance Mode

Download the firmware in the maintenance mode as explained here following. The target system must not be connected when downloading the firmware.

- (1) Within 2 seconds of activating power to the emulator, press the RESET switch on the emulator front panel. This will switch the emulator to the maintenance mode.

- (2) Start up the emulator debugger. When the Init dialog box setup is complete, the dialog which urges to download the firmware will appear. Download the firmware following messages. Required time for downloading the firmware depends on the connection of the interface.

- For the serial interface ..... About 7 minutes

- For the parallel interface ..... About 30 seconds

Figure 4.2 Downloading firmware in the maintenance mode

### CAUTION

#### Note on Downloading Firmware:

- Do not shut OFF power while the firmware is being downloaded. Doing so, the emulator will not start up properly. If power is shut OFF by mistake, redownload the firmware in the maintenance mode.

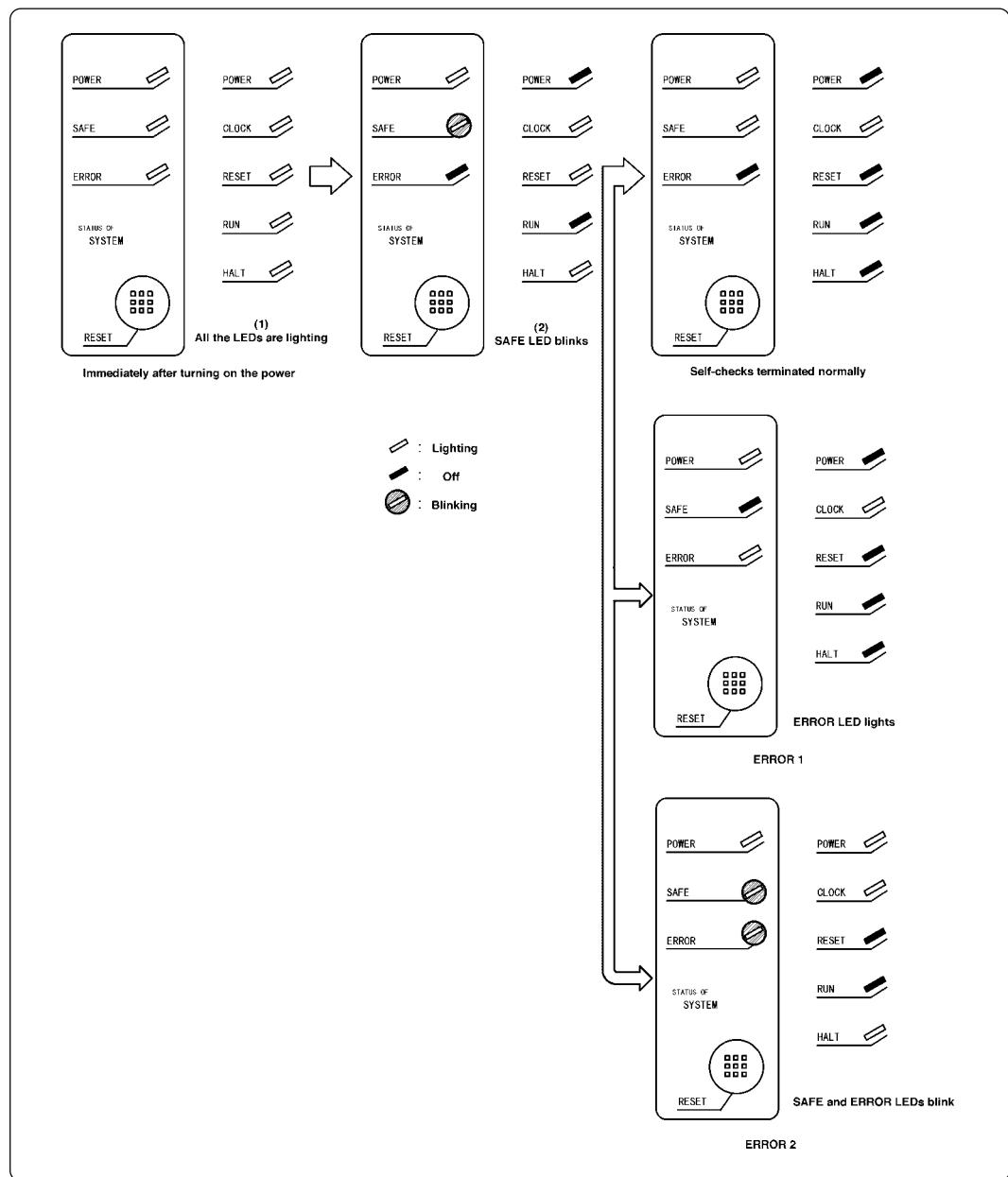

## 4.3 Self-check

### (1) Self-check Procedure

To run the emulator self-check, do so as explained here below. While the self-check is in progress, LEDs will change as shown in Figure 4.4.

- (1) Set the switches in the emulation pod same as the factory setting (see Figure 4.3).

- (2) When the target system is connected, disconnect the target system.

- (3) Within 2 seconds of activating power to the emulator, press the RESET switch on the emulator front panel to switch the emulator to the maintenance mode.

- (4) Check the "SAFE" LED starts blinking and then press the RESET switch again.

- (5) The self-check will start. If the normal result is displayed in about 2 minutes, the self-check has terminated normally.

Figure 4.3 Switch settings when running the self-check (factory-settings)

### (2) If an Error is Detected in the Self-check

If the self-check does not result normally (ERROR 1 and ERROR 2 in Figure 4.4), check the following.

- Check the connection of the emulation pod and the PC4701.

- Download the proper firmware.

- Check if the switches in this product are set same as the factory-settings (Figure 4.3).

### ⚠ CAUTION

#### Note on Self-check:

- If the self-check does not result normally (excluding target system errors), the emulation pod may be damaged. Then contact your local distributor.

Figure 4.4 Self-check procedure

# Chapter 5. Specifications

This chapter describes specifications of this product.

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| 5.1 Specifications .....                                                      | 44 |

| 5.2 Operation Timing in Memory Expansion and Microprocessor Modes (5 V) ..... | 45 |

| (1) Separate Bus, No-wait .....                                               | 45 |

| (2) Separate Bus, With Wait, Accessing External Memory Area .....             | 47 |

| (3) Multiplex Bus, With Wait, Accessing External Memory Area .....            | 49 |

| (4) Timing Requirements .....                                                 | 51 |

| 5.3 Operation Timing in Memory Expansion and Microprocessor Modes (3 V) ..... | 53 |

| (1) Separate Bus, No-wait .....                                               | 53 |

| (2) Separate Bus, With Wait, Accessing External Memory Area .....             | 55 |

| (3) Multiplex Bus, With Wait, Accessing External Memory Area .....            | 57 |

| (4) Timing Requirements .....                                                 | 59 |

| 5.4 Electrical Characteristics .....                                          | 61 |

| 5.5 Connection Diagram .....                                                  | 62 |

| 5.6 External Dimensions .....                                                 | 64 |

| (1) External Dimensions of Emulation Pod .....                                | 64 |

| (2) External Dimensions of Pitch Converter Board (FLX-100LCC) .....           | 65 |

# Chapter 5. Specifications

## 5.1 Specifications

Table 5.1 lists the specifications of M30620T2-RPD-E.

Table 5.1 Specifications of M30620T2-RPD-E

|                               |                                                                                                                                     |                                                                                       |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Emulators                     | PC4701M, PC4701HS or PC4701L                                                                                                        |                                                                                       |

| Applicable MCUs               | M16C/62 and M16C/62A Group MCUs (5 V)                                                                                               |                                                                                       |

| Evaluation MCU                | M30622SAFP                                                                                                                          |                                                                                       |

| Usable modes                  | Single-chip mode<br>Memory expansion mode<br>Microprocessor mode                                                                    |                                                                                       |

| Emulation memory              | 1 MB                                                                                                                                |                                                                                       |

| Maximum operating frequency   | JP2 = L                                                                                                                             | See the charts under this table (2.7 to 3.6 V).                                       |

|                               | JP2 = H                                                                                                                             | See the charts under this table (3.6 to 5.5 V).                                       |

| Clock supply                  | $X_{IN}$ - $X_{OUT}$                                                                                                                | Internal oscillator circuit board (OSC-3)<br>Switchable to external oscillator input. |

|                               | $X_{CIN}$ - $X_{COUT}$                                                                                                              | Internal oscillator circuit board<br>Switchable to external oscillator input.         |

| Operating voltage             | JP2 = L                                                                                                                             | 2.7 to 3.6 V                                                                          |

|                               | JP2 = H                                                                                                                             | 3.6 to 5.5 V                                                                          |

| Operating temperature         | 5 to 35°C (no dew)                                                                                                                  |                                                                                       |

| Storage temperature           | -10 to 60°C (no dew)                                                                                                                |                                                                                       |

| Power supply to emulation pod | Supplied from PC4701                                                                                                                |                                                                                       |

| Connection to target system   | Refer to "3.5 Connecting the Target System" (page 35).                                                                              |                                                                                       |

| Overseas standards            | <ul style="list-style-type: none"> <li>U.S. EMI standards (FCC part 15 Class A)</li> <li>CE marking (EN55022, EN50082-1)</li> </ul> |                                                                                       |

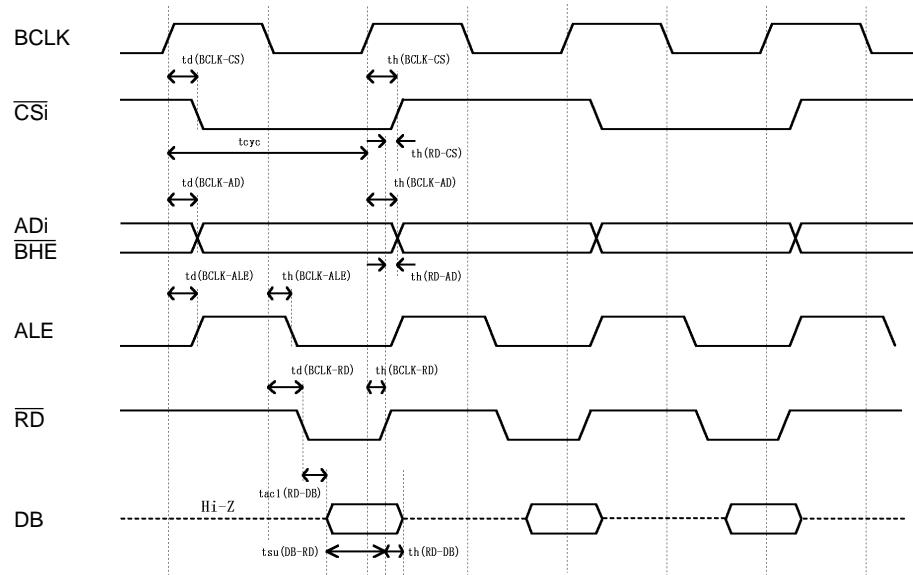

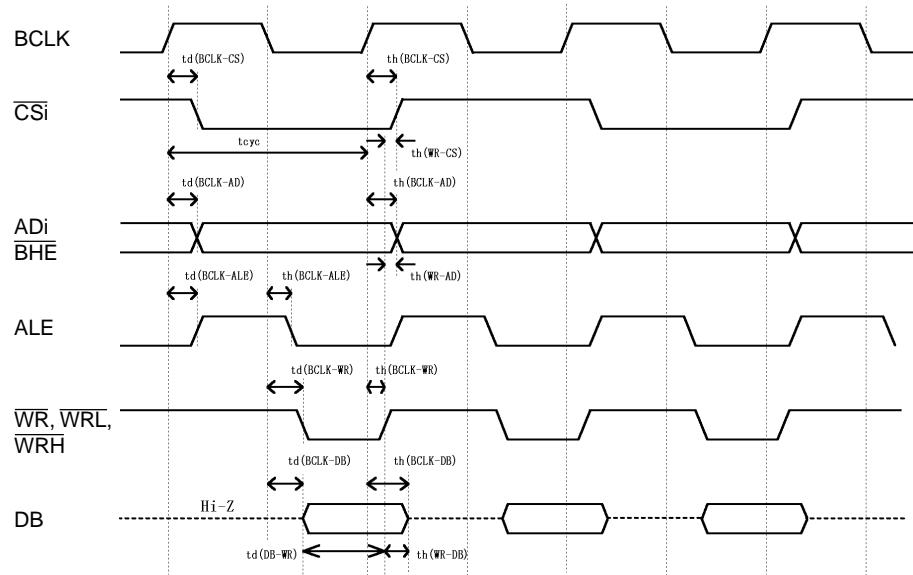

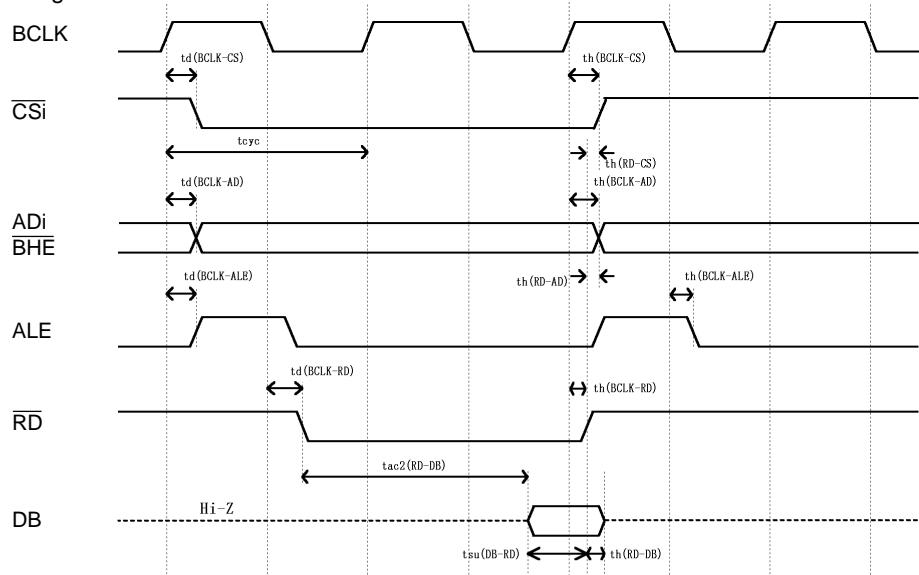

## 5.2 Operation Timing in Memory Expansion and Microprocessor Modes (5 V)

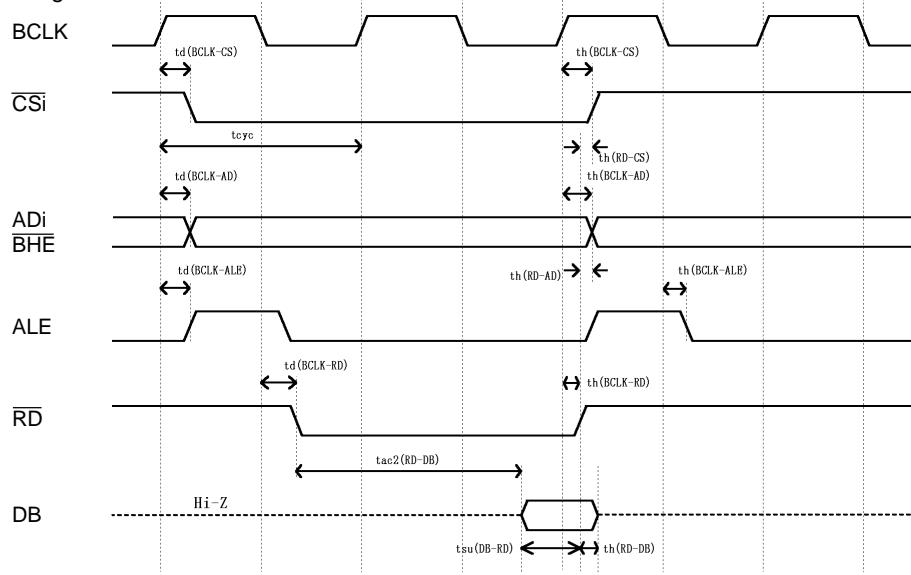

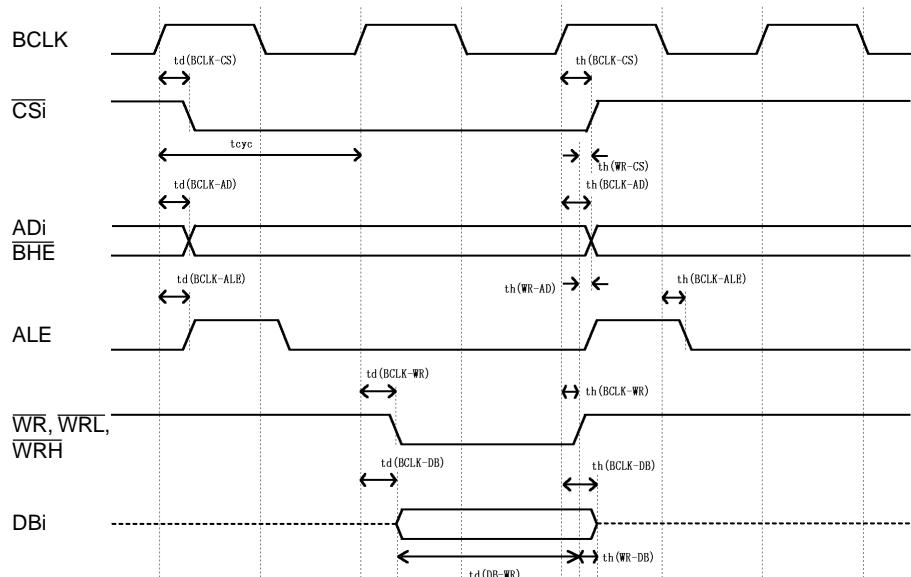

### (1) Separate Bus, No-Wait

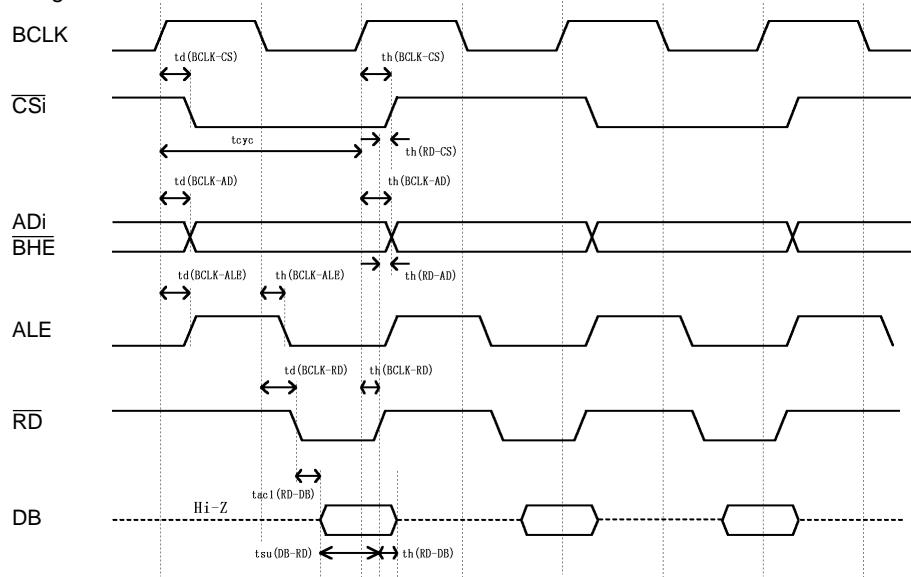

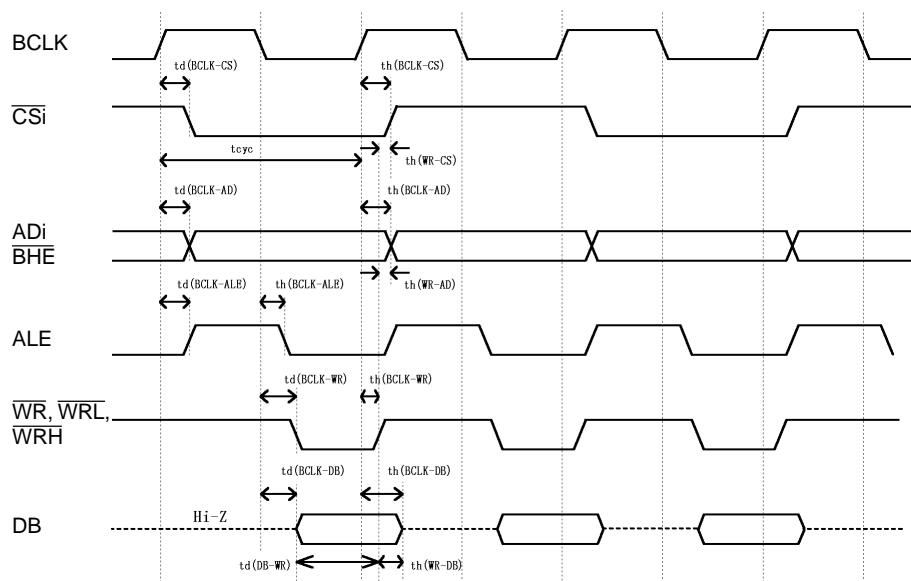

Table 5.2 and Figure 5.1 show the bus timing in the memory expansion mode and the microprocessor mode (separate bus, no-wait).

Table 5.2 Memory expansion mode and microprocessor mode (separate bus, no-wait)

| Symbol        | Item                                         | Actual MCU [ns] |      | This product [ns] |          |

|---------------|----------------------------------------------|-----------------|------|-------------------|----------|

|               |                                              | Min.            | Max. | Min.              | Max.     |

| Td (BCLK-AD)  | Address output delay time                    |                 | 25   |                   | See left |

| Th (BCLK-AD)  | Address output hold time (BCLK standard)     | 4               |      | See left          |          |

| Th (RD-AD)    | Address output hold time (RD standard)       | 0               |      | See left          |          |

| Th (WR-AD)    | Address output hold time (WR standard)       | 0               |      | See left          |          |

| Td (BCLK-CS)  | Chip-select output delay time                |                 | 25   |                   | See left |

| Th (BCLK-CS)  | Chip-select output hold time (BCLK standard) | 4               |      | See left          |          |

| Td (BCLK-ALE) | ALE signal output delay time                 |                 | 25   |                   | See left |

| Th (BCLK-ALE) | ALE signal output hold time                  | -4              |      | See left          |          |

| Td (BCLK-RD)  | RD signal output delay time                  |                 | 25   |                   | See left |

| Th (BCLK-RD)  | RD signal output hold time                   | 0               |      | See left          |          |

| Td (BCLK-WR)  | WR signal output delay time                  |                 | 25   |                   | See left |

| Th (BCLK-WR)  | WR signal output hold time                   | 0               |      | See left          |          |

| Td (BCLK-DB)  | Data output delay time (BCLK standard)       |                 | 40   |                   | See left |

| Th (BCLK-DB)  | Data output hold time (BCLK standard)        | 4               |      | See left          |          |

| Td (DB-WR)    | Data output delay time (WR standard)         | (*1)            |      | See left          |          |

| Th (WR-DB)    | Data output hold time (WR standard)          | 0               |      | See left          |          |

\*1 Calculated by the following formula according to the frequency of BCLK.

$$Td (DB-WR) = \frac{10^9}{f(BCLK) \times 2} - 40 \text{ [ns]}$$

$V_{CC} = 5 \text{ V}$

Memory expansion mode and microprocessor mode (no-wait)

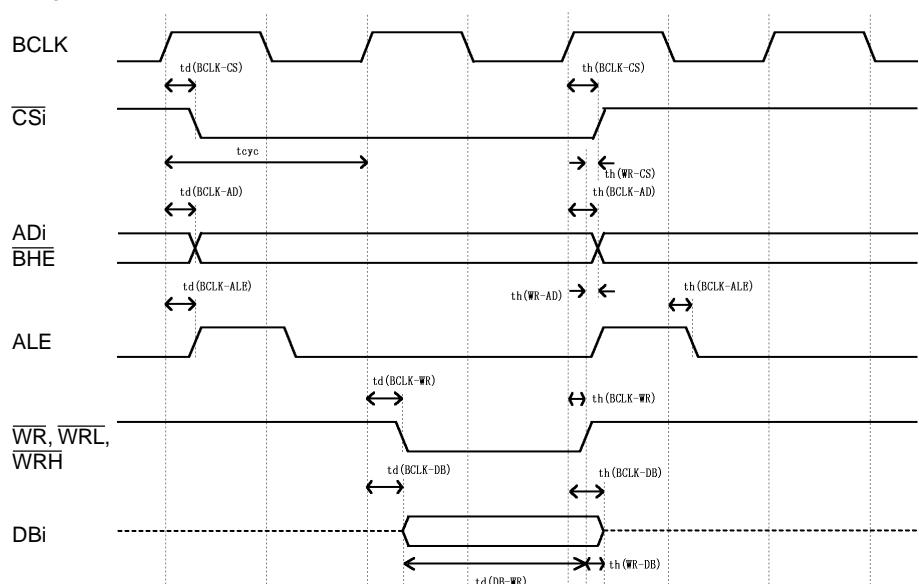

Read timing

Write timing

Conditions:

- $V_{CC} = 5 \text{ V}$

- Input timing voltage:  $V_{IL} = 0.8 \text{ V}$ ,  $V_{IH} = 2.5 \text{ V}$

- Output timing voltage:  $V_{OL} = 0.8 \text{ V}$ ,  $V_{OH} = 2.0 \text{ V}$

Figure 5.1 Memory expansion mode and microprocessor mode (no-wait)

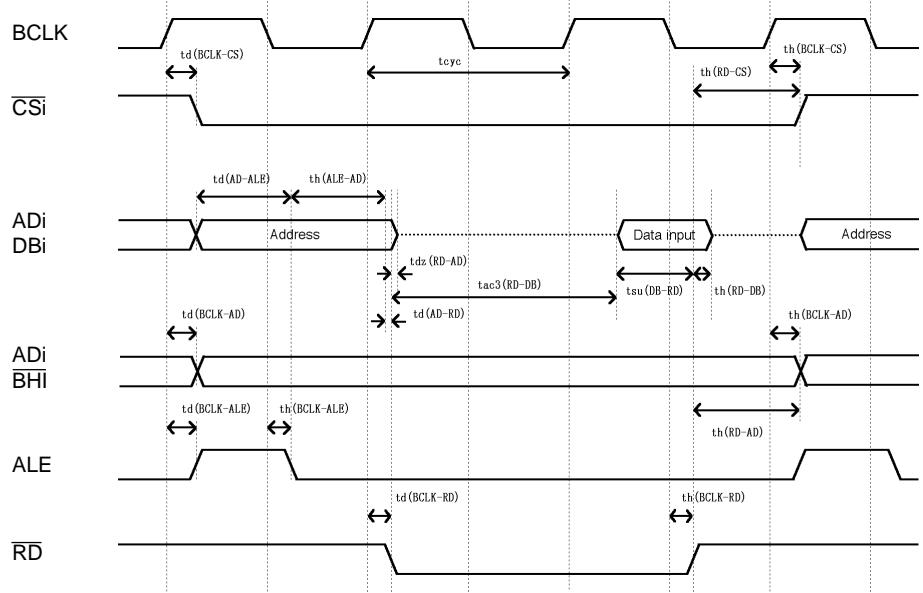

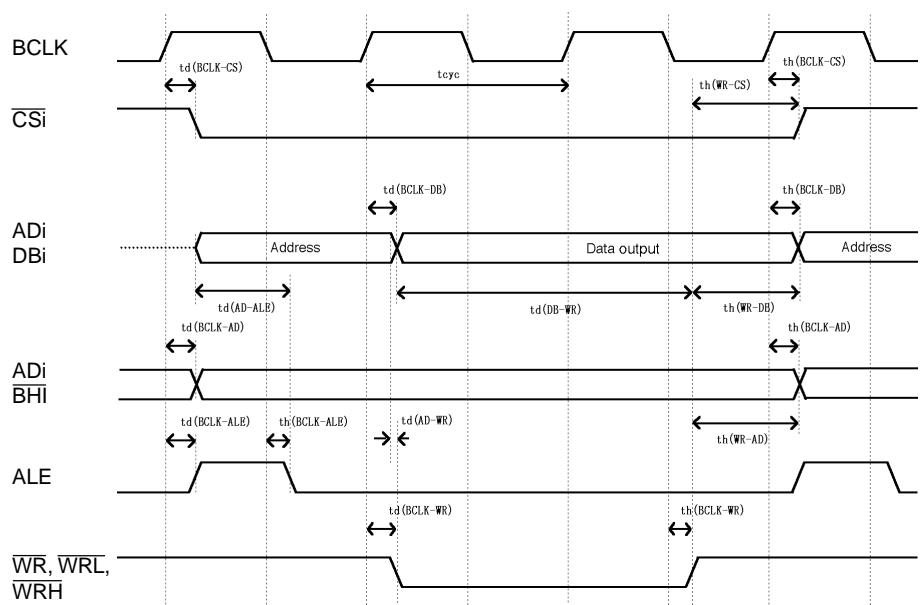

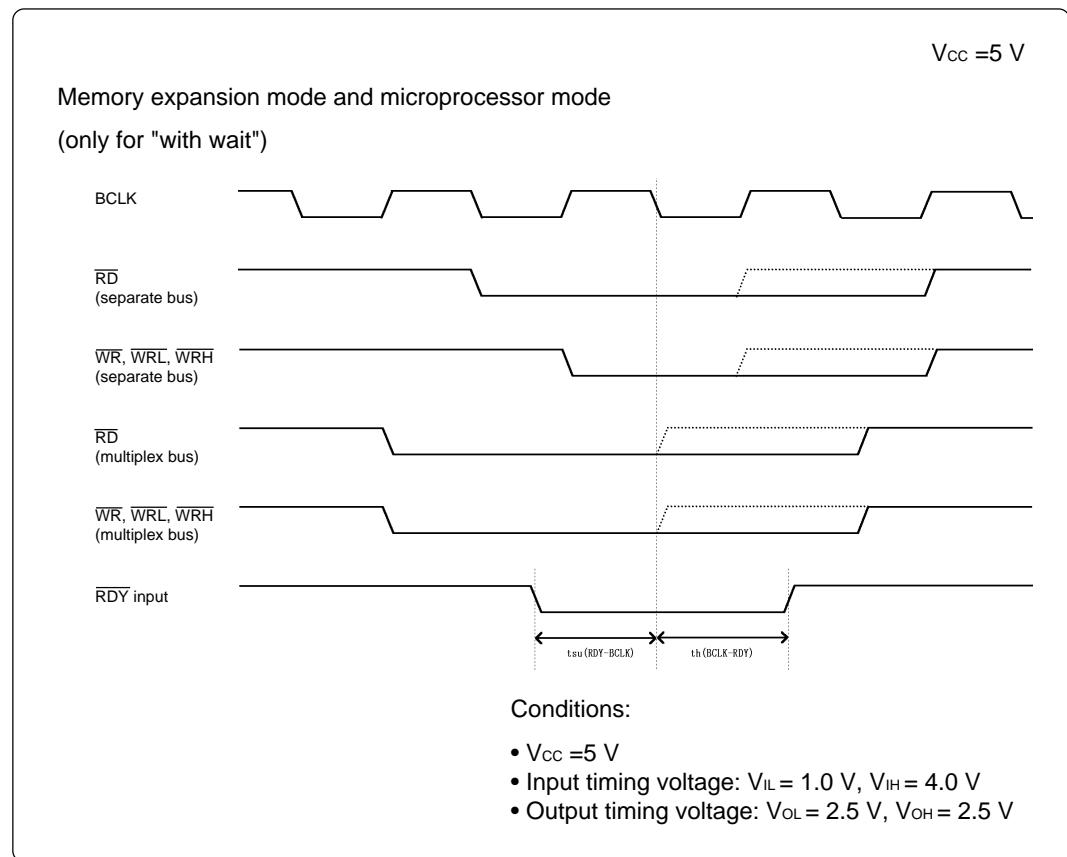

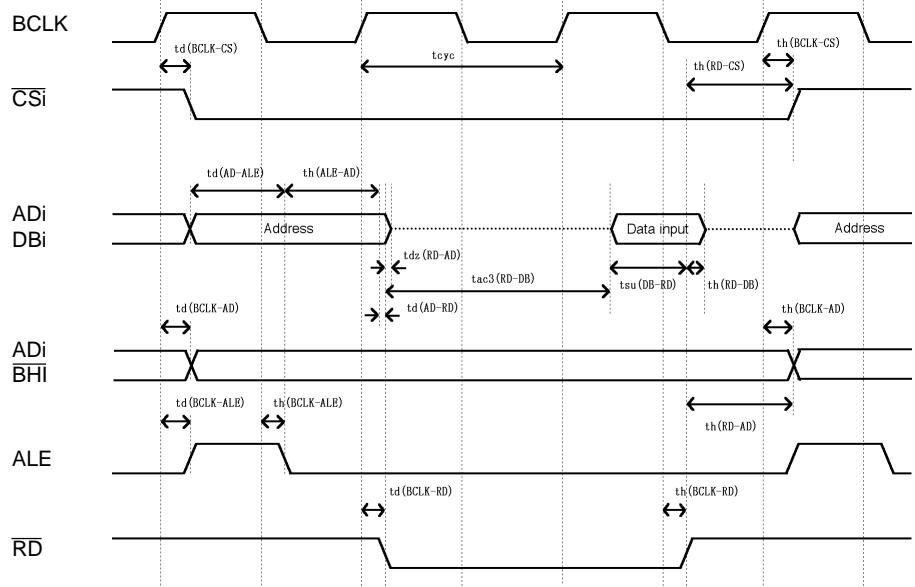

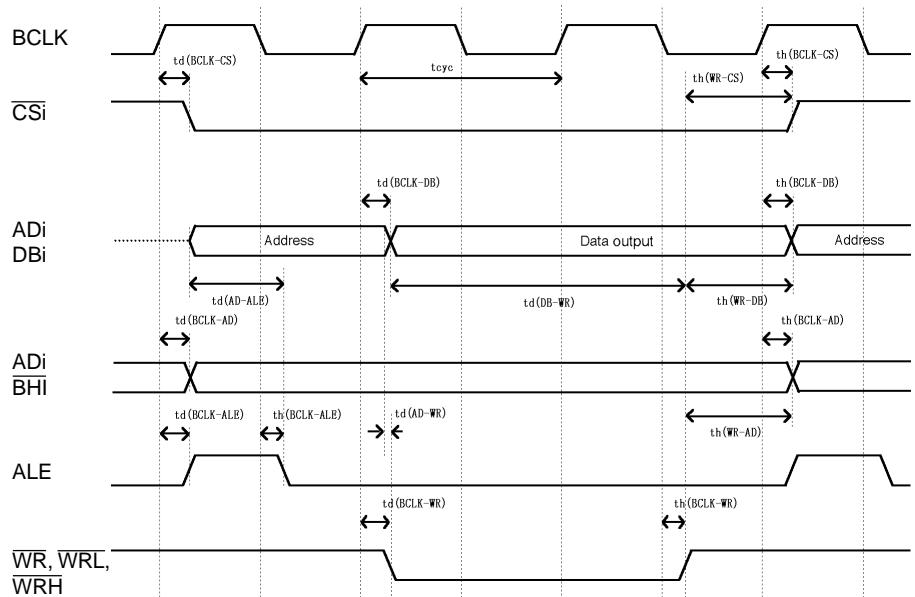

## (2) Separate Bus, With Wait, Accessing External Memory Area