MX9830 Bluetooth Serial Port Module

# LMX9830 Bluetooth<sup>®</sup> Serial Port Module

## **1.0 General Description**

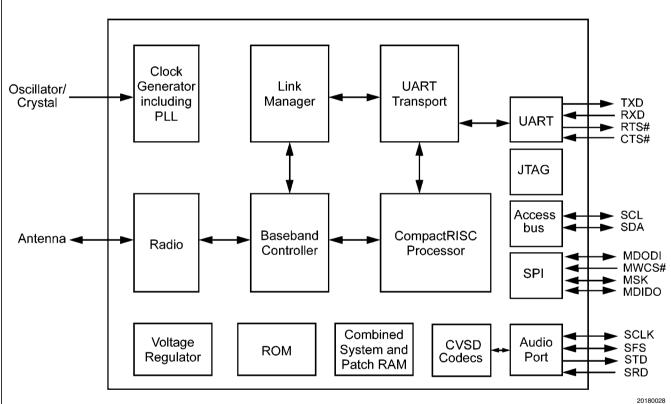

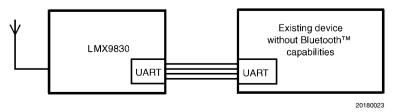

The National Semiconductor LMX9830 Bluetooth Serial Port module is a highly integrated Bluetooth 2.0 baseband controller and 2.4 GHz radio, combined to form a complete small form factor (6.1 mm x 9.1 mm x 1.2 mm) Bluetooth node.

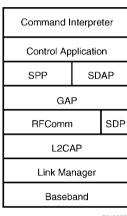

All hardware and firmware is included to provide a complete solution from antenna through the complete lower and upper layers of the Bluetooth stack, up to the application including the Generic Access Profile (GAP), the Service Discovery Application Profile (SDAP), and the Serial Port Profile (SPP). The module includes a configurable service database to fulfil service requests for additional profiles on the host. Moreover, the LMX9830 is pre-qualified as a Bluetooth Integrated Component. Conformance testing through the Bluetooth qualification program enables a short time to market after system integration by insuring a high probability of compliance and interoperability.

Based on National's CompactRISC<sup>®</sup> 16-bit processor architecture and Digital Smart Radio technology, the LMX9830 is optimized to handle the data and link management processing requirements of a Bluetooth node.

The firmware supplied in the on-chip ROM memory offers a complete Bluetooth (v2.0) stack including profiles and command interface. This firmware features point-to-point and point-to-multipoint link management supporting data rates up to the theoretical maximum over RFComm of 704 kbps (**Best in Class** in the industry). The internal memory supports up to 7 active Bluetooth data links and one active SCO link.

The on-chip Patch RAM provided for lowest cost and risk, allows the flexibility of firmware upgrade.

The LMX9830 module is lead free and RoHS (Restriction of Hazardous Substances) compliant. For more information on those quality standards, please visit our green compliance website at http://www.national.com/quality/green/

## 2.0 Features

- Compliant with the Bluetooth 2.0 Core Specification

Qualified Design ID (PRD 2.0): B012364

- Better than -80 dBm input sensitivity

- Class 2 operation

- Low power consumption

- High integration:

- Implemented in 0.18 µm CMOS technology

- RF includes antenna filter and switch on-chip

## 3.0 Other Features

#### **3.1 DIGITAL HARDWARE**

- Baseband and Link Management processors

- CompactRISC Core

- Embedded ROM and Patch RAM memory

- UART Command/Data Port:

- Support for up to 921.6k baud rate

- Auxiliary Host Interface Ports:

- Link Status

- Transceiver Status (Tx or Rx)

- Three General Purpose I/Os, available through the API

- Alternative IO functions:

- Link Status

- Transport layer activity

- Advanced Power Management (APM) features:

- Advanced power management functions

- Advanced Audio Interface for external PCM codec

- ACCESS.bus and SPI/Microwire for interfacing with external non-volatile memory

#### 3.2 FIRMWARE

- Complete Bluetooth Stack including:

- Baseband and Link Manager

- L2CAP, RFCOMM, SDP

- Profiles:

- GAP

- SDAP

- SPP

- Additional Profile support on Host, e.g.:

- Dial Up Networking (DUN)

- Facsimile Profile (FAX)

- File Transfer Protocol (FTP)

- Object Push Profile (OPP)

- Synchronization Profile (SYNC)

- Headset (HSP)

- Handsfree Profile (HFP)

- Basic Imaging Profile (BIP)

- Basic Printing Profile (BPP)

- On-chip application including:

- Default connections

- Command Interface:

- Link setup and configuration (also Multipoint)

- Configuration of the module

- Service database modifications

- UART Transparent mode

- Optimized cable replacement :

- Automatic transparent mode

Bluetooth® is a registered trademark of Bluetooth SIG, Inc. and is used under license by National Semiconductor Corporation. CompactRISC® is a registered trademark of National Semiconductor Corporation.

- LMX9830

- Event filter

#### **3.3 DIGITAL SMART RADIO**

- Accepts external clock or crystal input:

- 13 MHz Typical

- Supports 10 20 MHz

- Secondary 32.768 kHz oscillator for low-power modes

- 20 ppm cumulative clock error required for Bluetooth

- Synthesizer:

- Integrated VCO

- Provides all clocking for radio and baseband functions

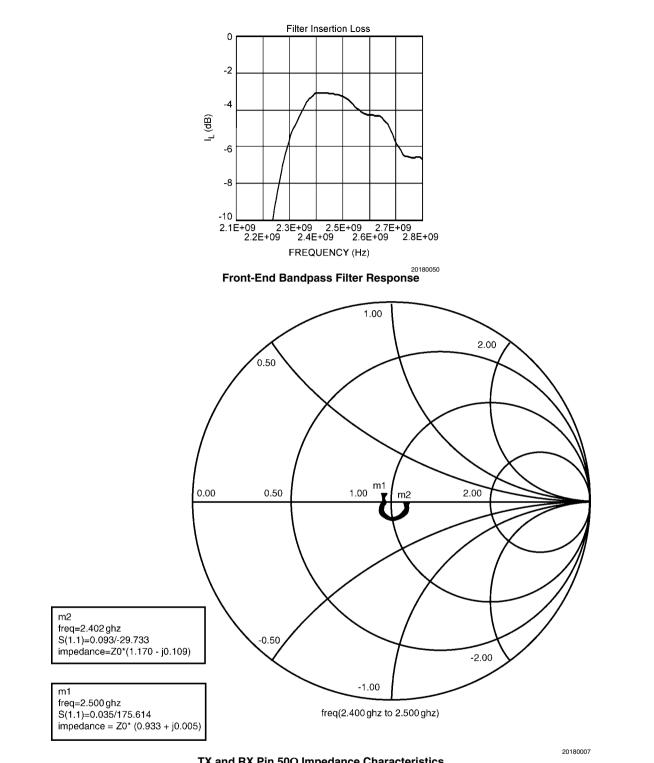

Antenna Port (50 Ω nominal impedance):

- Embedded front-end filter for enhanced out of band performance

- Integrated transmit/receive switch (full duplex operation via antenna port)

- Better than -80 dBm input sensitivity

- 0 dBm typical output power

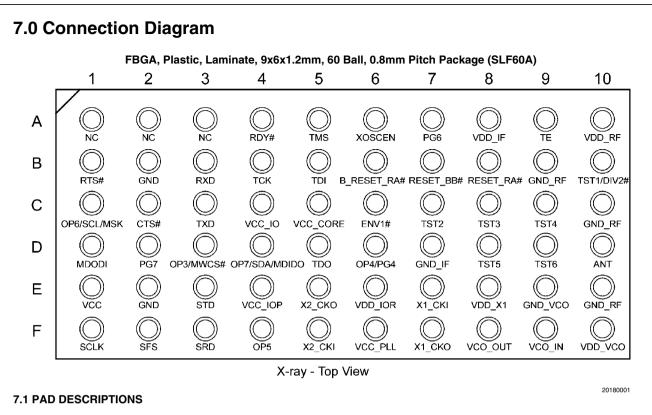

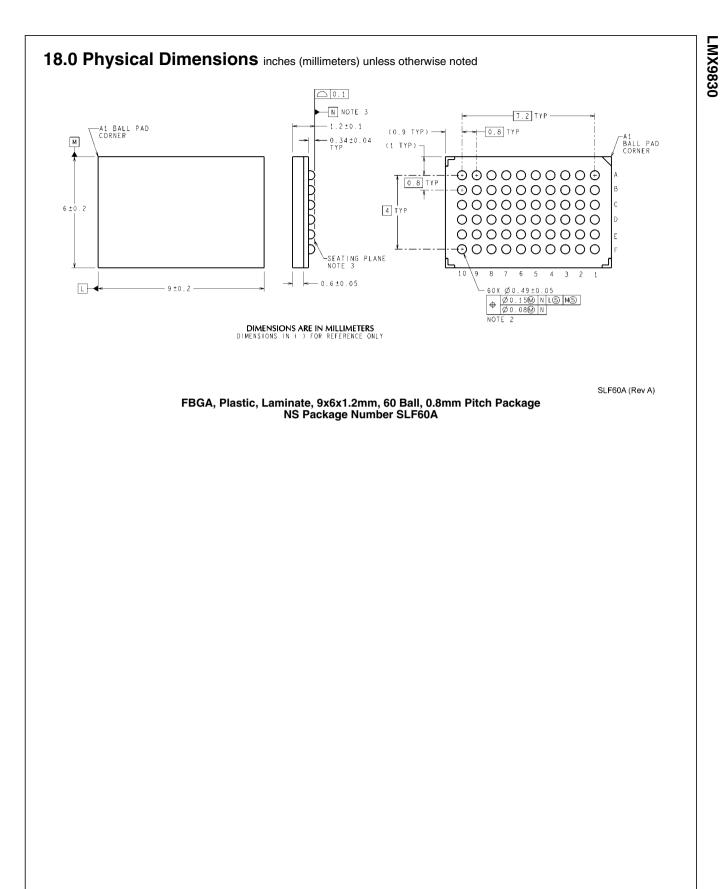

#### 3.4 PHYSICAL

- Compact size 6.1 mm x 9.1 mm x 1.2 mm

- Complete system interface provided in Ball Grid Array on underside for surface mount assembly

## 4.0 Applications

- Personal Digital Assistants

- POS Terminals

- Data Logging Systems

- Audio Gateway application

- Telemedicine/Medical, Industrial and Scientific

6.0 Ordering Information

| Order Number | Spec.         | Shipment Method      |

|--------------|---------------|----------------------|

| LMX9830SM    | NOPB (Note 1) | 388 pcs Tray         |

| LMX9830SMX   | NOPB (Note 1) | 2500 pcs Tape & Reel |

Note 1: NOPB = No Pb (No Lead)

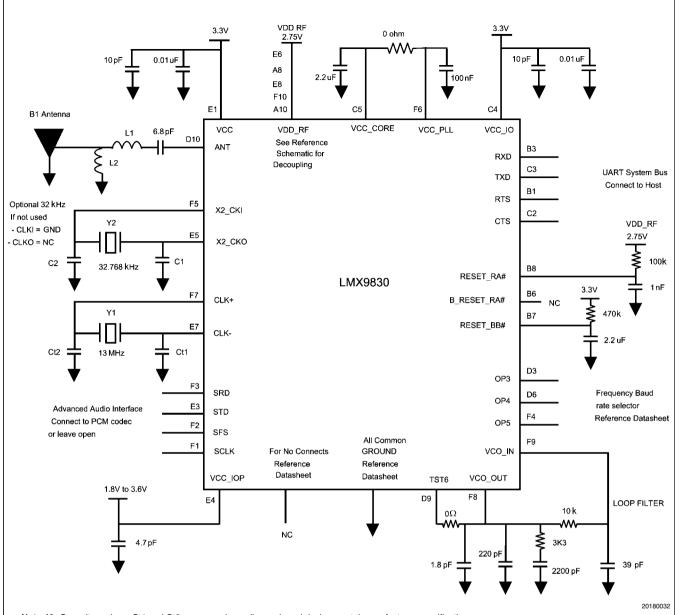

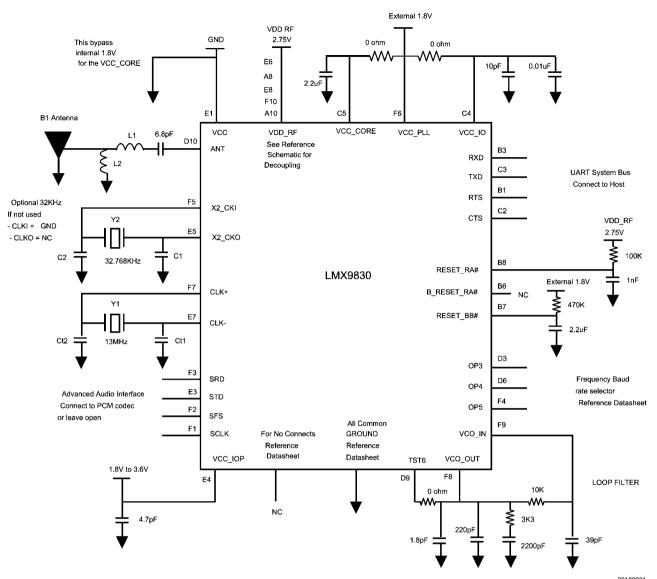

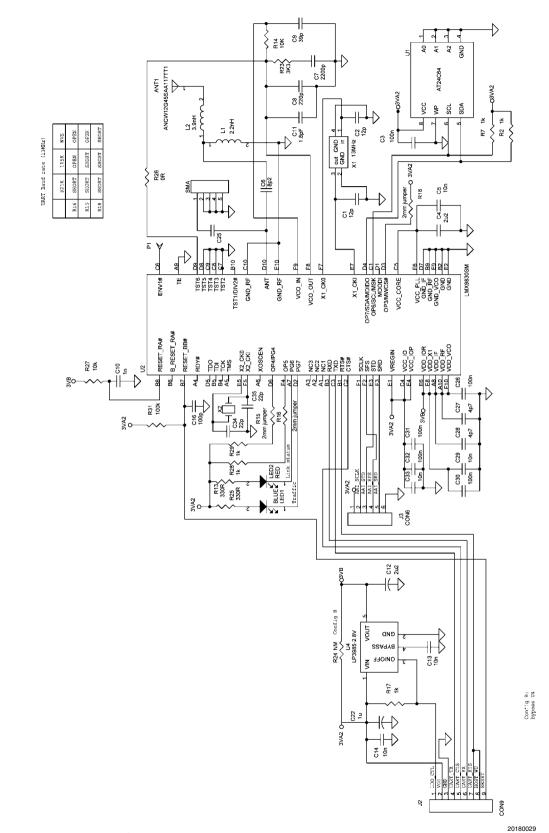

## 5.0 Functional Block Diagram

#### TABLE 1. Pin Descriptions

| Pad Name       | Pad Location | Туре                   | Default Layout | Description                                                                                                                               |

|----------------|--------------|------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| X1_CKO         | F7           | 0                      |                | Crystal 10-20 MHz                                                                                                                         |

| X1_CKI         | E7           | I                      |                | Crystal or External Clock 10-20 MHz                                                                                                       |

| X2_CKI         | F5           | I                      | GND            | 32.768 kHz Crystal Oscillator                                                                                                             |

|                |              |                        | (if not used)  |                                                                                                                                           |

| X2_CKO         | E5           | 0                      | NC             | 32.768 kHz Crystal Oscillator                                                                                                             |

|                |              |                        | (if not used)  |                                                                                                                                           |

| RESET_RA#      | B8           | I                      |                | Radio Reset (active low)                                                                                                                  |

| B_RESET_RA#    | B6           | 0                      | NC             | Buffered Reset Radio Output (active low)                                                                                                  |

| RESET_BB#      | B7           | I                      |                | Baseband Reset (active low)                                                                                                               |

| ENV1#          | C6           | I                      | NC             | ENV1: Environment Select (active low) used for<br>manufacturing test only                                                                 |

| TE             | A9           | I                      | GND            | Test Enable - Used for manufacturing test only                                                                                            |

| TST1/DIV2#     | B10          | I                      | NC             | <b>TST1</b> : Test Mode. Leave not connected to permit use<br>with VTune automatic tuning algorithm<br><b>DIV2#</b> : No longer supported |

| TST2           | C7           | I                      | GND            | Test Mode, Connect to GND                                                                                                                 |

| TST3           | C8           | I                      | GND            | Test Mode, Connect to GND                                                                                                                 |

| TST4           | C9           | I                      | GND            | Test Mode, Connect to GND                                                                                                                 |

| TST5           | D8           | I                      | GND            | Test Mode, Connect to GND                                                                                                                 |

| TST6           | D9           | I                      | VCO_OUT        | Test Input,                                                                                                                               |

|                |              |                        |                | Connect to VCO_OUT via 0 $\Omega$ resistor to permit use with VTune automatic tuning algorithm                                            |

| MDODI (Note 2) | D1           | I/O                    |                | SPI Master Out Slave In                                                                                                                   |

| OP6/SCL/MSK    | C1           | OP6:  <br>SCL/MSK: I/O | See Table 16   | OP6: Pin checked during Startup Sequence for<br>configuration option<br>SCL: ACCESS.Bus Clock<br>MSK: SPI Shift                           |

| Pad Name            | Pad Location | Туре                     | Default Layout                             | Description                                                                                                                           |

|---------------------|--------------|--------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| OP7/SDA/<br>MDIDO   | D4           | OP7: I<br>SDA/MDIDO: I/O | See Table 16                               | OP7: Pin checked during Startup Sequence for<br>configuration option<br>SDA: ACCESS.Bus Serial Data<br>MDIDO: SPI Master In Slave Out |

| OP3/MWCS#           | D3           | I                        | See <i>Table 16</i> and<br><i>Table 17</i> | OP3: Pin checked during Startup Sequence for configuration option MWCS#: SPI Slave Select Input (active low)                          |

| OP4/PG4             | D6           | OP4:  <br>PG4:  /O       | See <i>Table 16</i> and<br><i>Table 17</i> | OP4: Pin checked during Startup Sequence for configuration option PG4: GPIO                                                           |

| OP5                 | F4           | I/O                      | See <i>Table 16</i> and<br><i>Table 17</i> | <b>OP5:</b> Pin checked during Startup Sequence for configuration option                                                              |

| SCLK                | F1           | I/O                      |                                            | Audio PCM Interface Clock                                                                                                             |

| SFS                 | F2           | I/O                      |                                            | Audio PCM Interface Frame Synchronization                                                                                             |

| SRD                 | F3           | I                        |                                            | Audio PCM Interface Receive Data Input                                                                                                |

| STD                 | E3           | 0                        |                                            | Audio PCM Interface Transmit Data Output                                                                                              |

| XOSCEN              | A6           | 0                        |                                            | Clock Request. Toggles with X2 (LP0) crystal enable/<br>disable                                                                       |

| PG6                 | A7           | I/O                      |                                            | GPIO                                                                                                                                  |

| PG7                 | D2           | I/O                      |                                            | GPIO - Default setup RF traffic LED indication                                                                                        |

| CTS#(Note 3)        | C2           | 1                        | GND (if not used)                          | Host Serial Port Clear To Send (active low)                                                                                           |

| RXD                 | B3           | 1                        |                                            | Host Serial Port Receive Data                                                                                                         |

| RTS#(Note 4)        | B1           | 0                        | NC (if not used)                           | Host Serial Port Request To Send (active low)                                                                                         |

| TXD                 | C3           | 0                        | , ,                                        | Host Serial Port Transmit Data                                                                                                        |

| RDY#                | A4           | 0                        | NC                                         | JTAG Ready Output (active low)                                                                                                        |

| тск                 | B4           | 1                        | NC                                         | JTAG Test Clock Input                                                                                                                 |

| TDI                 | B5           |                          | NC                                         | JTAG Test Data Input                                                                                                                  |

| TDO                 | D5           | 0                        | NC                                         | JTAG Test Data Output                                                                                                                 |

| TMS                 | A5           | -                        | NC                                         | JTAG Test Mode Select Input                                                                                                           |

| VCO_OUT             | F8           | 0                        |                                            | Charge Pump Output, connect to Loop filter                                                                                            |

| VCO_IN              | F9           | 1                        |                                            | VCO Tuning Input, feedback from Loop filter                                                                                           |

| ANT                 | D10          | I/O                      |                                            | RF Antenna 50 $\Omega$ Nominal Impedance                                                                                              |

| VCC_PLL             | F6           | 0                        |                                            | 1.8V Core Logic Power Supply Output                                                                                                   |

| VCC_PLL<br>VCC_CORE | C5           | 0                        |                                            | 1.8V Voltage Regulator Output                                                                                                         |

|                     | E8           | 0                        |                                            | Power Supply Crystal Oscillator                                                                                                       |

| VDD_X1<br>VDD_VCO   | F10          |                          |                                            | Power Supply VCO                                                                                                                      |

|                     |              |                          |                                            |                                                                                                                                       |

| VDD_RF<br>VDD_IOR   | A10<br>E6    |                          |                                            | Power Supply RF<br>Power Supply I/O Radio/BB                                                                                          |

|                     |              | -                        |                                            |                                                                                                                                       |

| VDD_IF              | A8           |                          |                                            | Power Supply IF                                                                                                                       |

|                     | E4           |                          |                                            | Power Supply Audio Interface                                                                                                          |

|                     | C4           |                          |                                            | Power Supply I/O                                                                                                                      |

| VCC                 | E1           | I                        |                                            | Voltage Regulator Input                                                                                                               |

| GND_VCO             | E9           |                          |                                            | Ground                                                                                                                                |

| GND_RF              | B9, C10, E10 |                          |                                            | Ground                                                                                                                                |

| GND_IF              | D7           |                          |                                            | Ground                                                                                                                                |

| GND                 | B2,E2        |                          |                                            | Ground                                                                                                                                |

| NC                  | A1,A2,A3     |                          | NC                                         | Treat as no connect. Place pad for mechanical stability                                                                               |

Note 2: Must use 1k  $\Omega$  pull up.

Note 3: Connect to GND if CTS is not use.

Note 4: Treat as No Connect if RTS is not used. Pad required for mechanical stability.

## 8.0 General Specifications

Absolute Maximum Ratings (see *Table 2*) indicate limits beyond which damage to the device may occur. Operating Ratings (see *Table 3*) indicate conditions for which the device is intended to be functional.

This device is a high performance RF integrated circuit and is ESD sensitive. Handling and assembly of this device should be performed at ESD free workstations.

The following conditions are true unless otherwise stated in the tables below:

•  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$

```

V_{CC} = 3.3V

```

RF system performance specifications are guaranteed on National Semiconductor Mesa board rev 1.1 reference design platform.

| Symbol             | Parameter                                 | Min  | Max                   | Unit |

|--------------------|-------------------------------------------|------|-----------------------|------|

| V <sub>cc</sub>    | Digital Voltage Regulator input           | -0.2 | 4                     | V    |

| V <sub>I</sub>     | Voltage on any pad with GND = 0V          | -0.2 | V <sub>CC</sub> + 0.2 | V    |

| /DD_RF             | Supply Voltage Radio                      | 0.2  | 3.3                   | V    |

| /DD_IF             |                                           |      |                       |      |

| /DD_X1             |                                           |      |                       |      |

| /DD_VCO            |                                           |      |                       |      |

| P <sub>IN</sub> RF | RF Input Power                            |      | 0                     | dBm  |

| / <sub>ANT</sub>   | Applied Voltage to ANT pad                |      | 1.95                  | V    |

| -<br>S             | Storage Temperature Range                 | -65  | +150                  | °C   |

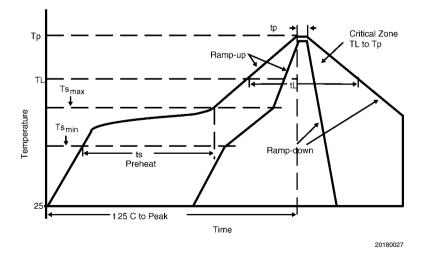

| ſ <sub>L</sub>     | Lead Temperature (Note 5) (solder 4 sec.) |      | 225                   | °C   |

| Г <sub>LNOPB</sub> | Lead Temperature NOPB (Note 5), (Note 6)  |      |                       |      |

|                    | (solder 40 sec.)                          |      | 260                   | °C   |

| ESD <sub>HBM</sub> | ESD - Human Body Model                    |      | 2000                  | V    |

| ESD <sub>MM</sub>  | ESD - Machine Model                       |      | 200 (Note 7)          | V    |

#### **TABLE 2. Absolute Maximum Ratings**

Note 5: Reference IPC/JDEC J-STD-20C spec.

Note 6: NOPB = No Pb (No Lead).

Note 7: A 200V ESD rating applies to all pins except OP3, OP6, OP7, MDODI, SCLK, SFS, STD, TDO, and ANT pins = 150V.

#### **TABLE 3. Recommended Operating Conditions**

| Symbol                    | Parameter                                                              | Min | Тур  | Max    | Unit |

|---------------------------|------------------------------------------------------------------------|-----|------|--------|------|

| V <sub>cc</sub>           | Digital Voltage Regulator input                                        | 2.5 | 2.75 | 3.6    | V    |

| T <sub>R</sub>            | Digital Voltage Regulator Rise Time                                    |     |      | 10     | μs   |

| T <sub>A</sub>            | Ambient Operating Temperature Range<br>Fully Functional Bluetooth Node | -40 | +25  | +125   | °C   |

| VCC_IO                    | Supply Voltage Digital I/O                                             | 1.6 | 3.3  | 3.6    | V    |

| VCC_PLL                   | Internally connected to VCC_Core                                       |     |      |        |      |

| VDD_RF                    | Supply Voltage Radio                                                   | 2.5 | 2.75 | 3      | V    |

| VDD_IF                    |                                                                        |     |      |        |      |

| VDD_X1                    |                                                                        |     |      |        |      |

| VDD_VCO                   |                                                                        |     |      |        |      |

| VDD_IOR                   | Supply Voltage Radio I/O                                               | 1.6 | 2.75 | VDD_RF | V    |

| VCC_IOP                   | Supply Voltage PCM Interface                                           | 1.6 | 3.3  | 3.6    | V    |

| VCC_CORE                  | Supply Voltage Output                                                  |     | 1.8  |        | ۷    |

| VCC_CORE <sub>MAX</sub>   | Supply Voltage Output Max Load                                         |     | 5    |        | mA   |

| VCC_CORE <sub>SHORT</sub> | When used as Supply Input (V <sub>CC</sub> grounded)                   | 1.6 | 1.8  | 2      | V    |

#### **TABLE 4. Power Supply Requirements** (Notes 8, 9)

| Symbol                | Parameter                                       | Min | Typ<br>(Note 10) | Мах | Unit |

|-----------------------|-------------------------------------------------|-----|------------------|-----|------|

| I <sub>CC-TX</sub>    | Power supply current for continuous transmit    |     |                  | 65  | mA   |

| I <sub>CC-RX</sub>    | Power supply current for continuous receive     |     |                  | 65  | mA   |

| I <sub>RXSL</sub>     | Receive Data in SPP Link, Slave (Note 11)       |     | 26               |     | mA   |

| I <sub>RXM</sub>      | Receive Data in SPP Link, Master (Note 11)      |     | 23               |     | mA   |

| I <sub>SnM</sub>      | Sniff Mode, Sniff interval 1 second (Note 11)   |     | 5.6              |     | mA   |

| I <sub>SC-TLDIS</sub> | Scanning, No Active Link, TL Disabled (Note 11) |     | 0.43             |     | mA   |

| I <sub>ldle</sub>     | Idle, Scanning Disabled, TL Disabled (Note 11)  |     | 100              |     | μA   |

Note 8: Power supply requirements based on Class II output power.

Note 9: Based on UART Baudrate 921.6 kbit/s.

Note 10:  $V_{CC}$  = 3.3V, VCC\_IO = 3.3V, Ambient Temperature = +25°C.

Note 11: Average values excluding IO.

#### **8.1 DC CHARACTERISTICS**

#### TABLE 5. Digital DC Characteristics

| Symbol           | Parameter                       | Condition                    | Min          | Max           | Units |

|------------------|---------------------------------|------------------------------|--------------|---------------|-------|

| V <sub>IH</sub>  | Logical 1 Input Voltage high    | 1.6V ≤ VCC_IO ≤ 3.0V         | 0.7 x VCC_IO | VCC_IO + 0.2  | V     |

|                  | (except oscillator I/O)         | $3.0V \le VCC_{IO} \le 3.6V$ | 2            | VCC_IO + 0.2  |       |

| V <sub>IL</sub>  | Logical 0 Input Voltage low     | 1.6V ≤ VCC_IO ≤ 3.0V         | -0.2         | 0.25 x VCC_IO | V     |

|                  | (except oscillator I/O)         | 3.0V ≤ VCC_IO ≤ 3.6V         | -0.2         | 0.8           |       |

| V <sub>HYS</sub> | Hysteresis Loop Width (Note 12) |                              | 0.1 x VCC_IO |               | V     |

| I <sub>он</sub>  | Logical 1 Output Current        | V <sub>OH</sub> = 2.4V,      | -10          |               | mA    |

|                  |                                 | $VCC_{IO} = 3.0V$            |              |               |       |

| I <sub>OL</sub>  | Logical 0 Output Current        | V <sub>OH</sub> = 0.4V,      | 10           |               | mA    |

|                  |                                 | VCC_IO = 3.0V                |              |               |       |

Note 12: Guaranteed by design.

#### 8.2 RF PERFORMANCE CHARACTERISTICS

In the performance characteristics tables the following applies:

- All tests performed are based on Bluetooth Test Specification revision 2.0.

- All tests are measured at antenna port unless otherwise specified

- $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$

- VDD\_RF = 2.8V unless otherwise specified.

RF system performance specifications are guaranteed on National Semiconductor Mesa Board rev 1.1 reference design platform.

#### **TABLE 6. Receiver Performance Characteristics**

| Symbol               | Parameter                   | c                            | Condition | Min | Typ<br>(Note 13) | Max | Unit |

|----------------------|-----------------------------|------------------------------|-----------|-----|------------------|-----|------|

| RX <sub>sense</sub>  | Receive Sensitivity         | BER < 0.001                  | 2.402 GHz |     | -80              | -76 | dBm  |

|                      |                             |                              | 2.441 GHz |     | -80              | -76 | dBm  |

|                      |                             | Γ                            | 2.480 GHz |     | -80              | -76 | dBm  |

| P <sub>in</sub> RF   | Maximum Input Level         |                              |           | -10 | 0                |     | dBm  |

| IMP                  | Intermodulation Performance | F1= + 3 MHz,                 |           | -38 | -36              |     | dBm  |

| (Note 14), (Note 15) |                             | F2= + 6 MHz,                 |           |     |                  |     |      |

|                      |                             | P <sub>in</sub> RF = -64 dBn | n         |     |                  |     |      |

| RSSI                 | RSSI Dynamic Range at LNA   |                              |           | -72 |                  | -52 | dBm  |

|                      | Input                       |                              |           |     |                  |     |      |

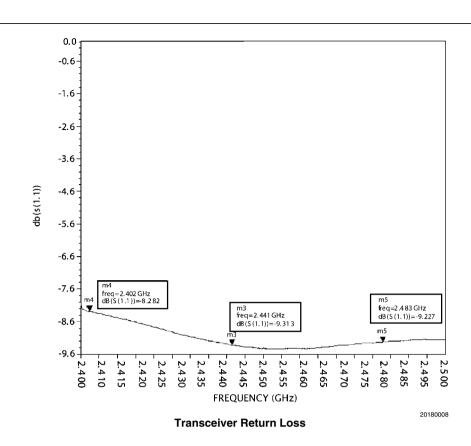

| Symbol                      | Parameter                                | Condition                                                                                | Min | Typ<br>(Note 13) | Мах | Unit |

|-----------------------------|------------------------------------------|------------------------------------------------------------------------------------------|-----|------------------|-----|------|

| Z <sub>RFIN</sub> (Note 15) | Input Impedance of RF Port<br>(RF_inout) | Single input impedance<br>F <sub>in</sub> = 2.5 GHz                                      |     | 32               |     | Ω    |

| Return Loss<br>(Note 15)    | Return Loss                              |                                                                                          |     |                  | -8  | dB   |

| OOB (Note 14),<br>(Note 15) | Out Of Band Blocking<br>Performance      | P <sub>in</sub> RF = -10 dBm,<br>30 MHz < F <sub>CWI</sub> < 2 GHz,<br>BER < 0.001       | -10 |                  |     | dBm  |

|                             |                                          | P <sub>in</sub> RF = -27 dBm,<br>2000 MHz < F <sub>CWI</sub> < 2399 MHz,<br>BER < 0.001  | -27 |                  |     | dBm  |

|                             |                                          | P <sub>in</sub> RF = -27 dBm,<br>2498 MHz < F <sub>CWI</sub> < 3000 MHz,<br>BER < 0.001  | -27 |                  |     | dBm  |

|                             |                                          | P <sub>in</sub> RF = -10 dBm,<br>3000 MHz < F <sub>CWI</sub> < 12.75 GHz,<br>BER < 0.001 | -10 |                  |     | dBm  |

Note 13: Typical operating conditions are at 2.75V operating voltage and 25°C ambient temperature.

Note 14: The  $f_0 = -64$  dBm Bluetooth modulated signal,  $f_1 = -39$  dbm sine wave,  $f_2 = -39$  dBm Bluetooth modulated signal,  $f_0 = 2f_1 - f_2$ , and  $|f_2 - f_1| = n + 1$  MHz, where n is 3, 4, or 5. For the typical case, n = 3.

Note 15: Not tested in production.

#### **TABLE 7. Transmitter Performance Characteristics**

| Symbol                                           | Parameter                                                    | Condition                                                                                                                          | Min | Typ<br>(Note 13) | Max  | Unit |

|--------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|------|------|

| P <sub>OUT</sub> RF                              | Transmit Output Power                                        | 2.402 GHz                                                                                                                          | -4  | 0                | +3   | dBm  |

|                                                  |                                                              | 2.441 GHz                                                                                                                          | -4  | 0                | +3   | dBm  |

|                                                  |                                                              | 2.480 GHz                                                                                                                          | -4  | 0                | +3   | dBm  |

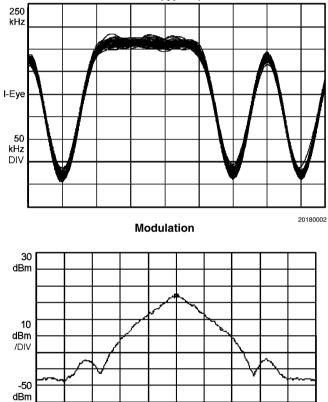

| MOD ΔF1 <sub>AVG</sub>                           | Modulation Characteristics                                   | Data = 00001111                                                                                                                    | 140 | 165              | 175  | kHz  |

| MOD ΔF2 <sub>MAX</sub> (Note 17)                 | Modulation Characteristics                                   | Data = 10101010                                                                                                                    | 115 | 125              |      | kHz  |

| ΔF2 <sub>AVG</sub> /DF1 <sub>AVG</sub> (Note 18) | Modulation Characteristics                                   |                                                                                                                                    | 0.8 |                  |      |      |

| 20 dB Bandwidth                                  |                                                              |                                                                                                                                    |     |                  | 1000 | kHz  |

| P <sub>OUT</sub> 2*f <sub>o</sub> (Note 19)      | PA 2 <sup>nd</sup> Harmonic Suppression                      | $\begin{array}{l} \mbox{Maximum gain setting:} \\ \mbox{f}_0 = 2402 \mbox{ MHz}, \\ \mbox{P}_{out} = 4804 \mbox{ MHz} \end{array}$ |     |                  | -30  | dBm  |

| Z <sub>RFOUT</sub> (Note 20)                     | RF Output Impedance/Input<br>Impedance of RF Port (RF_inout) | P <sub>out</sub> @ 2.5 GHz                                                                                                         |     | 47               |      | Ω    |

Note 16: Typical operating conditions are at 2.75V operating voltage and 25°C ambient temperature.

**Note 17:**  $\Delta$ F2max  $\geq$  115 kHz for at least 99.9% of all  $\Delta$ f2max.

Note 18: Modulation index set between 0.28 and 0.35.

Note 19: Out-of-Band spurs only exist at 2nd and 3rd harmonics of the CW frequency for each channel.

Note 20: Not tested in production.

LMX9830

#### **TABLE 8. Synthesizer Performance Characteristics**

| Symbol                           | Parameter                           | Condition               | Min  | Тур | Max  | Unit     |

|----------------------------------|-------------------------------------|-------------------------|------|-----|------|----------|

| f <sub>VCO</sub>                 | VCO Frequency Range                 |                         | 2402 |     | 2480 | MHz      |

| t <sub>LOCK</sub>                | Lock Time                           | f <sub>0</sub> ± 20 kHz |      | 120 |      | μs       |

| Δf <sub>0</sub> offset (Note 21) | Initial Carrier Frequency Tolerance | During preamble         | -75  | 0   | 75   | kHz      |

| Δf <sub>o</sub> drift (Note 21)  | Initial Carrier Frequency Drift     | DH1 data packet         | -25  | 0   | 25   | kHz      |

| -                                |                                     | DH3 data packet         | -40  | 0   | 40   | kHz      |

|                                  |                                     | DH5 data packet         | -40  | 0   | 40   | kHz      |

|                                  |                                     | Drift Rate              | -20  | 0   | 20   | kHz/50µs |

| t <sub>D</sub> - Tx              | Transmitter Delay Time              | From Tx data to antenna |      | 4   |      | μs       |

Note 21: Frequency accuracy is dependent on crystal oscillator chosen. The crystal must have a cumulative accuracy of < +/-20ppm to meet Bluetooth specifications.

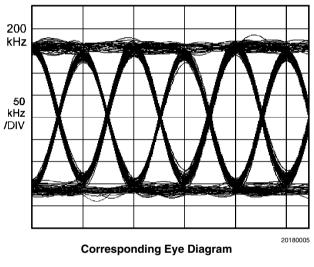

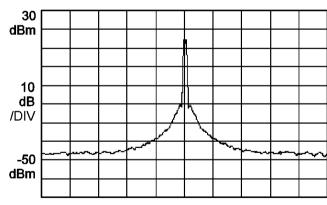

8.3 PERFORMANCE DATA (typical)

Synthesizer Phase Noise

20180006

20180004

## 9.0 Functional Description

#### 9.1 BASEBAND AND LINK MANAGEMENT PROCESSORS

Baseband and Lower Link control functions are implemented using a combination of National's CompactRISC 16-bit processor and the Bluetooth Lower Link Controller. These processors operate from integrated ROM memory and RAM and execute on-board firmware implementing all Bluetooth functions.

#### 9.1.1 Bluetooth Lower Link Controller

The integrated Bluetooth Lower Link Controller (LLC) complies with the Bluetooth Specification version 2.0 and implements the following functions:

- Adaptive Frequency Hopping

- Interlaced Scanning

- Fast Connect

- Support for 1, 3, and 5 slot packet types

- 79 Channel hop frequency generation circuitry

- Fast frequency hopping at 1600 hops per second

- Power management control

- Access code correlation and slot timing recovery

#### 9.1.2 Bluetooth Upper Layer Stack

The integrated upper layer stack is prequalified and includes the following protocol layers:

- L2CAP

- RFComm

- SDP

#### 9.1.3 Profile support

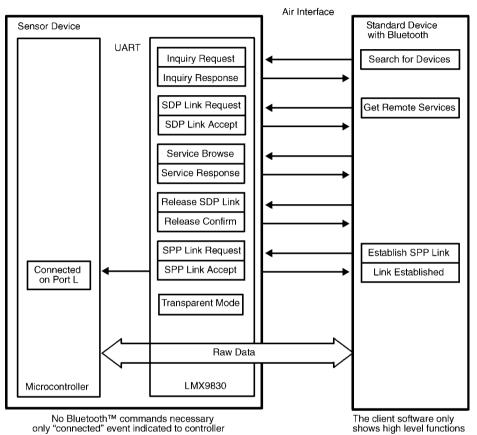

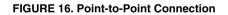

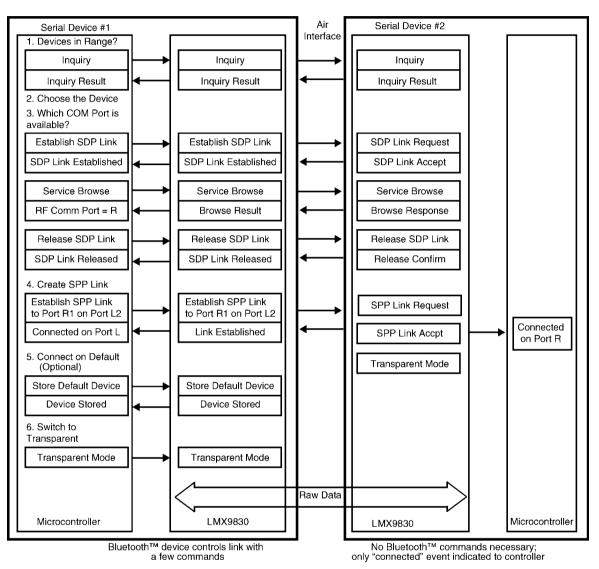

The on-chip application of the LMX9830 allows full standalone operation, without any Bluetooth protocol layer necessary outside the module. It supports the Generic Access Profile (GAP), the Service Discovery Application Profile (SDAP), and the Serial Port Profile (SPP).

The on-chip profiles can be used as interfaces to additional profiles executed on the host. The LMX9830 includes a configurable service database to answer requests with the profiles supported.

#### 9.1.4 Application with command interface

The module supports automatic slave operation eliminating the need for an external control unit. The implemented transparent option enables the chip to handle incoming data raw, without the need for packaging in a special format. The device uses a pin to block unallowed connections. This pincode can be fixed or dynamically set.

Acting as master, the application offers a simple but versatile command interface for standard Bluetooth operation like inquiry, service discovery, or serial port connection. The firmware supports up to seven slaves. Default Link Policy settings and a specific master mode allow optimized configuration for the application specific requirements. See also *Section 11.0 Integrated Firmware.*

#### 9.1.5 Memory

The LMX9830 introduces 16 kB of combined system and Patch RAM memory that can be used for data and/or code upgrades of the ROM based firmware. Due to the flexible startup used for the LMX9830 operating parameters like the Bluetooth Device Address (BD\_ADDR) are defined during boot time. This allows reading out the parameters of an external EEPROM or programming them directly over UART.

#### 9.1.6 External memory interfaces

As the LMX9830 is a ROM based device with no on-chip non volatile storage, the operation parameters will be lost after a power cycle or hardware reset. In order to prevent re initializing such parameters, patches or even user data, the LMX9830 offers two interfaces to connect an external EEP-ROM to the device:

- µ-wire/SPI

- Access.bus (I<sup>2</sup>C compatible)

The selection of the interface is done during start up based on the option pins. See *Table 16* for the option pin descriptions.

#### 9.1.7 µ-wire/SPI interface

In case the firmware is configured by the option pins to use a  $\mu$ -wire/SPI EEPROM, the LMX9830 will activate that interface and try to read out data from the EEPROM. The external memory needs to be compatible to the reference listed in *Table 10.* The largest size EEPROM supported is limited by the addressing format of the selected NVM.

The device must have a page size equal to N x 32 bytes. The firmware requires that the EEPROM supports Page write. Clock must be HIGH when idle.

#### TABLE 9. M95640-S EEPROM 8k x 8

| Parameter                | Value                                     |  |  |

|--------------------------|-------------------------------------------|--|--|

| Supplier                 | ST Microelectronics                       |  |  |

| Supply Voltage (Note 22) | 1.8 - 3.6V                                |  |  |

| Interface                | SPI compatible (positive clock SPI Modes) |  |  |

| Memory Size              | 8k x 8, 64 kbit                           |  |  |

| Clock Rate (Note 22)     | 2 MHz                                     |  |  |

| Access                   | Byte and Page Write (up to 32 bytes)      |  |  |

Note 22: Parameter range reduced to requirements of National reference design.

#### 9.1.8 Access.bus Interface

In case the firmware is configured by the option pins to use an access.bus or I<sup>2</sup>C compatible EEPROM, the LMX9830 will activate that interface and try to read out data from the EEP-ROM. The external memory needs to be compatible to the reference listed in *Table 10*. The largest size EEPROM supported is limited by the addressing format of the selected NVM. The device must have a page size equal to N x 32 bytes.

The device uses a 16 bit address format. The device address must be "000".

#### TABLE 10. 24C64 EEPROM 8kx8

| Parameter               | Value                   |

|-------------------------|-------------------------|

| Supplier                | Atmel                   |

| Supply Voltage(Note 23) | 2.7 - 5.5 V             |

| Interface               | 2 wire serial interface |

| Memory Size             | 8K x 8, 64 kbit         |

| Clock Rate (Note 23)    | 100 kHz                 |

| Access                  | 32 Byte Page Write Mode |

Note 23: Parameter range reduced to requirements of National reference design.

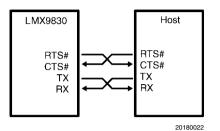

#### 9.2 TRANSPORT PORT - UART

The LMX9830 provides one Universal Asynchronous Receiver Transmitter (UART). The UART interface consists out of Receive (RX), Transmit (TX), Ready-to-Send (RTS) and Clear-to-Send signals. RTS and CTS are used for hardware handshaking between the host and the LMX9830. Since the LMX9830 acts as gateway between the bluetooth and the UART interface, National recommends to use the handshaking signals especially for transparent operation. In case two signals are used CTS needs to be pulled to GND. Please refer also to "LMX9830 Software User's Guide" for detailed information on 2-wire operation.

The UART interface supports formats of 8-bit data with or without parity, with one or two stop bits. It can operate at standard baud rates from 2400bits/s up to a maximum baud

rate of 921.6 kbits/s. DMA transfers are supported to allow for fast processor independent receive and transmit operation.

The UART baudrate is configured during startup by checking option pins OP3, OP4 and OP5 for reference clock and baudrate. In case Auto baud rate detect is chosen, the firmware check the NVS area if a valid UART baudrate has been stored in a previous session. In case, no useful value can be found the device will switch to auto baud rate detection and wait for an incoming reference signal.

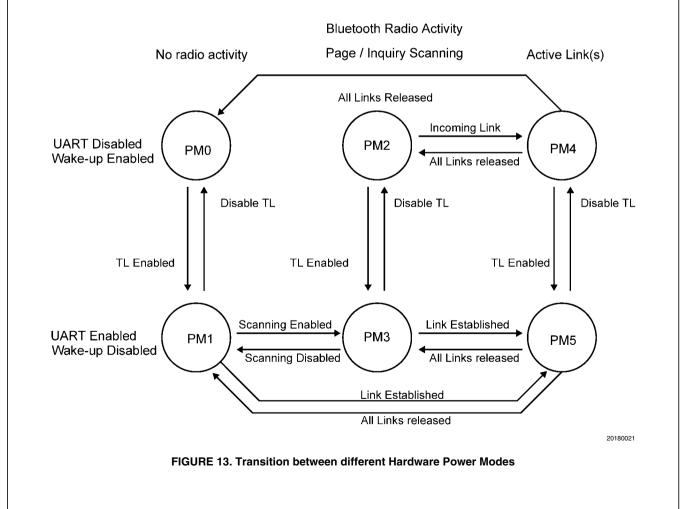

The UART offers wakeup from the power save modes via the multi-input wakeup module. When the LMX9830 is in low power mode, RTS# and CTS# can function as Host\_WakeUp and Bluetooth\_WakeUp respectively. *Table 11* represents the operational modes supported by the firmware for implementing the transport via the UART.

#### **TABLE 11. UART Operation Modes**

|              | _                    |                                                                             |                      |

|--------------|----------------------|-----------------------------------------------------------------------------|----------------------|

| Item         | Range                | Default at Power-Up                                                         | With Auto-Detect     |

| Baud Rate    | 2.4 to 921.6 kbits/s | Either configured by option pins, NVS parameter or auto baud rate detection | 2.4 to 921.6 kbits/s |

| Flow Control | RTS#/CTS# or None    | RTS#/CTS#                                                                   | RTS#/CTS#            |

| Parity       | Odd, Even, None      | None                                                                        | None                 |

| Stop Bits    | 1,2                  | 1                                                                           | 1                    |

| Data Bits    | 8                    | 8                                                                           | 8                    |

#### 9.3 AUDIO PORT

#### 9.3.1 Advanced Audio Interface

The Advanced Audio Interface (AAI) is an advanced version of the Synchronous Serial Interface (SSI) that provides a fullduplex communications port to a variety of industry-standard 13/14/15/16-bit linear or 8-bit log PCM codecs, DSPs, and other serial audio devices.

The interface allows the support one codec or interface. The firmware selects the desired audio path and interface configuration by a parameter that is located in RAM (imported from

non-volatile storage or programmed during boot-up). The audio path options include the Motorola MC145483 codec, the OKI MSM7717 codec, the Winbond W681360/W681310 codecs and the PCM slave through the AAI.

In case an external codec or DSP is used the LMX9830 audio interface generates the necessary bit and frame clock driving the interface.

*Table 12* summarizes the audio path selection and the configuration of the audio interface at the specific modes. The LMX9830 supports one SCO link.

| Audio setting                  | Interface                   | Freq             | Format                           | AAI Bit Clock  | AAI Frame Clock | AAI Frame Sync<br>Pulse Length |

|--------------------------------|-----------------------------|------------------|----------------------------------|----------------|-----------------|--------------------------------|

| OKI<br>MSM7717                 | Advanced audio<br>interface | ANY<br>(Note 24) | 8-bit log PCM<br>(a-law only)    | 480 kHz        | 8 kHz           | 14 Bits                        |

| Motorola MC145483<br>(Note 25) | Advanced audio<br>interface |                  | 13-bit linear                    | 480 kHz        | 8 kHz           | 13 Bits                        |

| OKI<br>MSM7717                 | Advanced audio<br>interface | 13 MHz           | 8-bit log PCM<br>(a-law only)    | 520 kHz        | 8 kHz           | 14 Bits                        |

| Motorola MC145483<br>(Note 26) | Advanced audio<br>interface |                  | 13-bit linear                    | 520 kHz        | 8 kHz           | 13 Bits                        |

| Winbond W681310                | Advanced audio<br>interface | 13 MHz           | 8 bit log PCM<br>A-law and μ-law | 520 kHz        | 8 kHz           | 14 Bits                        |

| Winbond W681360                | Advanced audio<br>interface | 13 MHz           | 13-bit linear                    | 520 kHz        | 8 kHz           | 13 Bits                        |

| PCM slave (Note 27)            | Advanced audio<br>interface | ANY<br>(Note 24) | 8/16 bits                        | 128 - 1024 kHz | 8 kHz           | 8/16 Bits                      |

#### **TABLE 12. Audio Path Configuration**

Note 24: For supported frequencies see Table 20.

Note 25: Due to internal clock divider limitations the optimum of 512 kHz, 8 kHz can not be reached. The values are set to the best possible values. The clock mismatch does not result in any discernible loss in audio quality.

Note 26: Due to internal clock divider limitations the optimum of 512 kHz, 8 kHz can not be reached. The values are set to the best possible values. The clock mismatch does not result in any discernible loss in audio quality.

Note 27: In PCM slave mode, parameters are stored in NVS. Bit clock and frame clock must be generated by the host interface.

**PCM slave configuration example:** PCM slave uses the slot 0, 1 slot per frame, 16 bit linear mode, long frame sync, normal frame sync. In this case, 0x03E0 should be stored in NVS. See "LMX9830 Software Users Guide" for more details.

#### 9.4 AUXILIARY PORTS

#### 9.4.1 RESET#

There are two reset inputs: RESET\_RA# for the radio and RESET\_BB# for the baseband. Both are active low.

There is also a reset output, B\_RESET\_RA# (Buffered Radio Reset) active low. This output follows input RESET\_RA#.

When RESET\_RA# is released, going high, B\_RESET\_RA# stays low until the clock has started.

Please see Section 9.5 SYSTEM POWER UP for details.

#### 9.4.2 General Purpose I/Os

The LMX9830 offers 3 pins which either can be used as indication and configuration pins or can be used for General Purpose functionality. The selection is made out of settings derived out of the power up sequence.

In General Purpose configuration the pins are controlled hardware specific commands giving the ability to set the direction, set them to high or low or enable a weak pull-up. In alternate function the pins have pre-defined indication functionality. Please see *Table 13* for a description on the alternate indication functionality.

#### TABLE 13. Alternate GPIO Pin Configuration

|                                                                                                                                                                                                                                  | TABLE 13. Alternate GP                                                  | 10 Pin Configuration                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                                                                                                                                                                                                                              |                                                                         | Description                                                                                                                                                                                                                                                               |

| OP4/PG4                                                                                                                                                                                                                          | Operation Mode pin to config                                            | ure Transport Layer settings during boot-up                                                                                                                                                                                                                               |

| PG6                                                                                                                                                                                                                              | GPIO                                                                    |                                                                                                                                                                                                                                                                           |

| PG7                                                                                                                                                                                                                              | RF Traffic indication                                                   |                                                                                                                                                                                                                                                                           |

| <b>9.5 SYSTEM POWER UP</b><br>In order to correctly power-up the L<br>quence is recommended to be per<br>Apply VCC_IO and V <sub>CC</sub> to the LMX<br>The RESET_RA# should be driver<br>should be driven high at a recommended | formed:<br>(9830.<br>n high. Then RESET_BB#<br>nended time of 1ms after | the LMX9830 voltage rails are high. The LMX9830 is properly reset.<br>Please see timing diagram, <i>Figure 1</i> .<br>ESR of the crystal also has impact on the startup time of the crystal oscillator circuit of the LMX9830 (See <i>Table 14</i> and <i>Table 15</i> ). |

| All VCC and VDD Lines                                                                                                                                                                                                            |                                                                         |                                                                                                                                                                                                                                                                           |

| RESET_RA#<br>↓ t <sub>P</sub> -<br>↓ ↓ ◀                                                                                                                                                                                         |                                                                         | <br> <br> <br>                                                                                                                                                                                                                                                            |

| RESET_BB#                                                                                                                                                                                                                        |                                                                         |                                                                                                                                                                                                                                                                           |

| х1_СКО                                                                                                                                                                                                                           |                                                                         |                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                  | I I LMX9830<br>Initialization<br>LMX9830<br>Oscillator<br>Start-Up      |                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                  | LMX9830 in<br>Power-Up Mode                                             | LMX9830 in Normal Mode                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                  | FIGURE 1. LMX9830 Po                                                    | wer on Reset Timing                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                  | TABLE 14. LMX9830 Po                                                    | ower to Reset timing                                                                                                                                                                                                                                                      |

| Symbol              | Parameter              | Condition                                       | Min       | Тур | Max | Unit |

|---------------------|------------------------|-------------------------------------------------|-----------|-----|-----|------|

| t <sub>PTORRA</sub> | Power to Reset _RA#    | V <sub>CC</sub> and VCC_IO at operating voltage | <500      |     |     |      |

|                     |                        | level to valid reset                            | (Note 28) |     |     | μs   |

| t <sub>PTORBB</sub> | Reset_RA# to Reset_BB# | V <sub>CC</sub> and VCC_IO at operating voltage | 1         |     |     |      |

|                     |                        | level to valid reset                            | (Note 29) |     |     | ms   |

Note 28: Rise time on power must switch on fast, rise time <500us. Note 29: Recommended value.

-MX9830

#### TABLE 15. ESR vs. Startup Time

| ESR (Ω) | Typical (Note 30), (Note 31) | Unit |

|---------|------------------------------|------|

| 10      | 12                           | ms   |

| 25      | 13                           | ms   |

| 40      | 16                           | ms   |

| 50      | 24                           | ms   |

| 80      | 30                           | ms   |

Note 30: Frequency, loading caps and ESR all must be considered for determining startup time.

Note 31: For reference only, must be tested on each system to accurately design POR and correctly startup system.

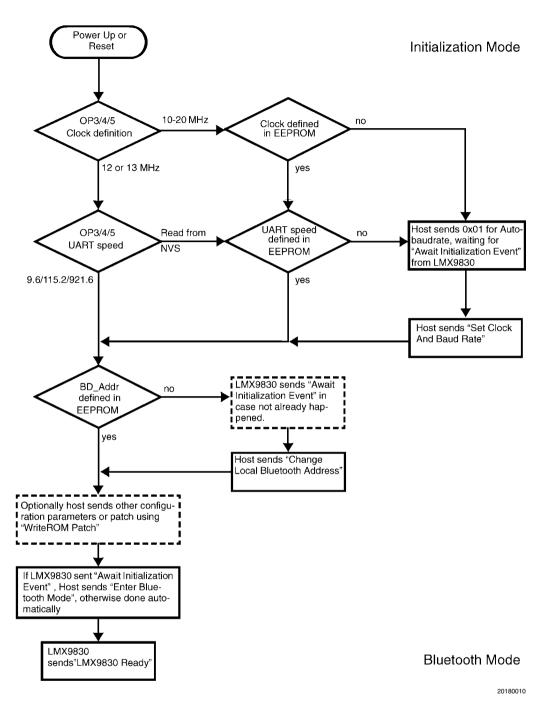

#### 9.6 STARTUP SEQUENCE

During startup the LMX9830 checks the options register pins OP3 to OP7 for configuration on operation mode, external clock source, transport layer and available non volatile storage PROM.

The different options for startup are described in Table 16.

#### 9.6.1 Options Register

External pads in Table 16 are latched in this register at the end of Reset. The Options register can be read by firmware at any time.

All pads are inputs with weak on-chip pull-up/down resistors during Reset. Resistors are disconnected at the end of RESET BB#.

1 = Pull-up resistor connected in application

- 0 = Pull-down resistor connected in application

- x = Don't care

#### 9.6.2 Startup With External PROM Available

To be able to read out information from an external PROM the option pins have to be set according to Table 16. Startup sequence activities:

- 1. From the Options registers OP6 and OP7, the LMX9830 checks if a serial PROM is available to use (ACCESS.bus or Microwire).

- 2. If serial PROM is available, the permanent parameter block, patch block, and non-volatile storage (NVS) are read from it. If the BD Address is not present, enter the BD address to be saved in the NVS. For more information

see Section 9.6.4 Configuring the LMX9830 Through Transport Layer.

- 3. From the Options register OP3, OP4 and OP5, the LMX9830 checks for clocking information and transport layer settings. If the NVS information are not sufficient, the LMX9830 will send the "Await Initialization" event on the TL (Transport Layer) and wait for additional information (see Section 9.6.3 Startup Without External PROM Available.)

- 4. The LMX9830 compensates the UART for new BBCLK information from the NVS.

- 5 The LMX9830 starts up the Bluetooth core.

#### 9.6.3 Startup Without External PROM Available

The following sequence will take place if OP6 and OP7 have been set to "No external memory" as described in Table 16. Startup sequence activities:

- 1. From the Options registers OP6 and OP7, the LMX9830 checks if a serial PROM is available to use.

- From the Options register OP3, OP4 and OP5, the 2. LMX9830 checks for clocking mode and transport layer.

- The LMX9830 sends the "Await Initialization" Event on the TL (Transport Layer) and waits for NVS configuration commands. The configuration is finalized by sending the "Enter Bluetooth Mode" command.

- The LMX9830 compensates the UART for new BBCLK information from the NVS.

- The LMX9830 starts up the Bluetooth core. 5.

|        |     |     |                      | Comment              |                   |                                                                            |

|--------|-----|-----|----------------------|----------------------|-------------------|----------------------------------------------------------------------------|

| OP3    | OP4 | OP5 | <b>OP6</b> (Note 33) | <b>OP7</b> (Note 34) | ENV1#             |                                                                            |

| PD     | PD  | PD  | PD                   | PD                   | PU                | PD = Internal Pull-down during Reset<br>PU = Internal Pull-up during Reset |

| x      | x   | x   | Open (0)             | Open (0)             | Open (1)<br>BBCLK | No serial memory                                                           |

| х      | x   | x   | 1                    | Open (0)             | Open (1)<br>BBCLK | Reserved                                                                   |

| х      | x   | x   | Open (0)             | 1                    | Open (1)<br>BBCLK | Microwire serial memory                                                    |

| х      | x   | x   | 1                    | 1                    | Open (1)<br>BBCLK | ACCESS.bus serial memory                                                   |

| T_SCLK | х   | х   | T_RFDATA             | T_RFCE               | 0 BBCLK           | Test mode                                                                  |

TABLE 16. Startup Sequence Options (Note 32)

Note 32: 1/0 pull-up/down resistor connected in application.

Note 33: If OP6 is 1, must use 1k  $\Omega$  pull up, If OP6 is 0, must use 10k  $\Omega$  pull down.

Note 34: If OP7 is 1, must use  $1 k \Omega$  pull up.

FIGURE 2. Flow Diagram for the Start-up Sequence

#### **TABLE 17. Fixed Frequencies**

| Osc Freq. (MHz) | BBCLK (MHz)     | PLL (48 MHz) | OP3 (Note 35) | <b>OP4</b> (Note 36) | <b>OP5</b> (Note 37) | Function                 |

|-----------------|-----------------|--------------|---------------|----------------------|----------------------|--------------------------|

| 12              | 12              | OFF          | 0             | 0                    | 0                    | UART speed read from NVS |

| 10-20 (Note 38) | 10-20 (Note 35) | ON           | 0             | 1                    | 0                    | Clock and UART baudrate  |

|                 |                 |              |               |                      |                      | detection                |

| 13              | 13              | OFF          | 1             | 0                    | 0                    | UART speed read from NVS |

| 13              | 13              | OFF          | 1             | 0                    | 1                    | UART speed 9.6 kbps      |

| 13              | 13              | OFF          | 1             | 1                    | 0                    | UART speed 115.2 kbps    |

| 13              | 13              | OFF          | 1             | 1                    | 1                    | UART speed 921.6 kbps    |

Note 35: If OP3 is 1, must use 1k  $\Omega$  pull up.

Note 36: If OP4 is 1, must use 1k  $\Omega$  pull up.

Note 37: If OP5 is 1, must use 1k  $\Omega$  pull up.

Note 38: Supported frequencies see Table 21.

#### 9.6.4 Configuring the LMX9830 Through Transport Layer

As described in *Section 9.5 SYSTEM POWER UP*, the LMX9830 will check during startup the Options Registers if an external PROM is available. If the information on the PROM are incomplete or no PROM is installed the LMX9830 will boot into the "initialization Mode".

The mode is confirmed by the "Await Initialization" Event.

The following information are needed to enter Bluetooth Mode:

- Bluetooth Device Address (BD\_Addr)

- External clock source (only if 10 20 MHz has been selected)

- UART Baudrate (only if Auto baudrate detection has been selected)

In general the following procedure will initialize the LMX9830:

- 1. Wait for "Await initialization" Event

- Event will only appear if transport layer speed is set or after successful baudrate detection.

- Send "Set Clock and Baudrate" Command only if the clock speed is not known through hardware configuration (i.e only if OP3, OP4, OP5 = 0 1 0).

- 3. Send "Write BD\_Addr" to Configure Local Bluetooth Device Address.

- 4. Send "Enter Bluetooth Mode"

- LMX9830 will use configured clock and UART speed and start the command interface.

- Note: In case no EEPROM is used, BDAddr, clock source and Baudrate are only valid until the next power-cycle or hardware reset.

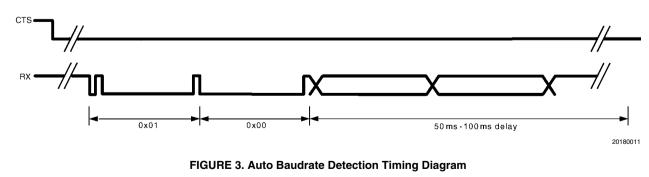

#### 9.6.5 Auto Baud Rate Detection

The LMX9830 supports an Automatic Baudrate Detection in case the external clock is different to 12, 13MHz or the range 10-20 MHz or the baudrate is different to 9.6 kbps, 115.2 or 921.6 kbit/s.

The baudrate detection is based on the measurement of a single character. The following issues need to be considered:

- The flow control pin CTS must be low or else the host is in flow stop.

- The Auto Baudrate Detector measures the length of the 0x01 character from the positive edge of bit 0 to the positive edge of stop bit.

- Therefore the very first received character must always be a 0x01.

- The host can restrict itself to send only a 0x01 character or also can send a command.

- The host must flush the TX buffer within 50-100 milliseconds depend on clock frequency on the host controller.

- After 50-100 milliseconds the UART is about to be initialized and short after the host should receive a "Await Initialization" Event or an "Command Status" Event.

# 9.7 USING AN EXTERNAL EEPROM FOR NON-VOLATILE DATA

The LMX9830 offers two interfaces to connect to external memory. Depending on the EEPROM used, the interface is activated by setting the correct option pins during start up. See *Table 16* for the option pin settings.

The external memory is used to store mandatory parameters like the BD\_Address as well as many optional parameters like Link Keys or even User data.

The NVM is organized with fixed addresses for the parameters. Because of that the EEPROM can be preprogrammed with default parameters in manufacturing. Refer to "Operation Parameters Stored in LMX9830" for the organization of the NVS map.

In case the external memory is empty on first startup the LMX9830 will behave as like no memory is connected. (See *Section 9.6.3 Startup Without External PROM Available*). During the startup process parameters can be written directly to the EEPROM to be available after next bootup. On first bootup, the EEPROM will be automatically programmed to default values, including the UART speed of 9600 BPS. Patches supplied over the TL will be stored automatically into the EEPROM.

## 10.0 Digital Smart Radio

#### **10.1 FUNCTIONAL DESCRIPTION**

The integrated Digital Smart Radio utilizes a heterodyne receiver architecture with a low intermediate frequency (2 MHz) such that the intermediate frequency filters can be integrated on chip. The receiver consists of a low-noise amplifier (LNA) followed by two mixers. The intermediate frequency signal processing blocks consist of a poly-phase bandpass filter (BPF), two hard-limiters (LIM), a frequency discriminator (DET), and a post-detection filter (PDF). The received signal level is detected by a received signal strength indicator (RSSI).

The received frequency equals the local oscillator frequency (fLO) plus the intermediate frequency (fIF):

#### fRF = fLO + fIF (supradyne).

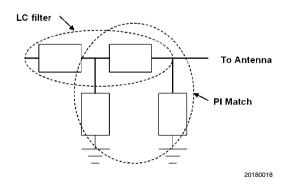

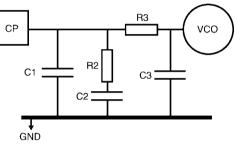

The radio includes a synthesizer consisting of a phase detector, a charge pump, an (off-chip) loop-filter, an RF-frequency divider, and a voltage controlled oscillator (VCO).

The transmitter utilizes IQ-modulation with bit-stream data that is gaussian filtered. Other blocks included in the transmitter are a VCO buffer and a power amplifier (PA).

#### **10.2 RECEIVER FRONT-END**

The receiver front-end consists of a low-noise amplifier (LNA) followed by two mixers and two low-pass filters for the I- and Q-channels.

The intermediate frequency (IF) part of the receiver front-end consists of two IF amplifiers that receive input signals from the mixers, delivering balanced I- and Q-signals to the polyphase bandpass filter. The poly-phase bandpass filter is directly followed by two hard-limiters that together generate an AD-converted RSSI signal.

#### 10.2.1 Poly-Phase Bandpass Filter

The purpose of the IF bandpass filter is to reject noise and spurious (mainly adjacent channel) interference that would otherwise enter the hard limiting stage. In addition, it takes care of the image rejection.

The bandpass filter uses both the I- and Q-signals from the mixers. The out-of-band suppression should be higher than 40 dB (f<1 MHz, f>3 MHz). The bandpass filter is tuned over process spread and temperature variations by the autotuner circuitry. A 5th order Butterworth filter is used.

#### 10.2.2 Hard-Limiter and RSSI

The I- and Q-outputs of the bandpass filter are each followed by a hard-limiter. The hard-limiter has its own reference current. The RSSI (Received Signal Strength Indicator) measures the level of the RF input signal.

The RSSI is generated by piece-wise linear approximation of the level of the RF signal. The RSSI has a mV/dB scale, and an analog-to-digital converter for processing by the baseband circuit. The input RF power is converted to a 5-bit value. The RSSI value is then proportional to the input power (in dBm). The digital output from the ADC is sampled on the BPKTCTL signal low-to-high transition.

#### **10.3 RECEIVER BACK-END**

The hard-limiters are followed by a two frequency discriminators. The I-frequency discriminator uses the  $90\times$  phase-shifted signal from the Q-path, while the Q-discriminator uses the  $90\times$  phase-shifted signal from the I-path. A poly-phase bandpass filter performs the required phase shifting. The output signals of the I- and Q-discriminator are substracted and filtered by a low-pass filter. An equalizer is added to improve the eye-pattern for 101010 patterns.

After equalization, a dynamic AFC (automatic frequency offset compensation) circuit and slicer extract the RX\_DATA from the analog data pattern. It is expected that the Eb/No of the demodulator is approximately 17 dB.

#### 10.3.1 Frequency Discriminator

The frequency discriminator gets its input signals from the limiter. A defined signal level (independent of the power supply voltage) is needed to obtain the input signal. Both inputs of the frequency discriminator have limiting circuits to optimize performance. The bandpass filter in the frequency discriminator is tuned by the autotuning circuitry.

#### 10.3.2 Post-Detection Filter and Equalizer

The output signals of the FM discriminator first go through a post-detection filter and then through an equalizer. Both the post-detection filter and equalizer are tuned to the proper frequency by the autotuning circuitry. The post-detection filter is a low-pass filter intended to suppress all remaining spurious signals, such as the second harmonic (4 MHz) from the FM detector and noise generated after the limiter.

The post-detection filter also helps for attenuating the first adjacent channel signal. The equalizer improves the eyeopening for 101010 patterns. The post-detection filter is a third order Butterworth filter.

#### **10.4 AUTOTUNING CIRCUITRY**

The autotuning circuitry is used for tuning the bandpass filter, the detector, the post-detection filter, the equalizer, and the transmit filters for process and temperature variations. The circuit also includes an offset compensation for the FM detector.

#### **10.5 SYNTHESIZER**

The synthesizer consists of a phase-frequency detector, a charge pump, a low-pass loop filter, a programmable frequency divider, a voltage-controlled oscillator (VCO), a deltasigma modulator, and a lookup table.

The frequency divider consists of a divide-by-2 circuit (divides the 5 GHz signal from the VCO down to 2.5 GHz), a divideby-8-or-9 divider, and a digital modulus control. The deltasigma modulator controls the division ratio and also generates an input channel value to the lookup table.

#### 10.5.1 Phase-Frequency Detector

The phase-frequency detector is a 5-state phase-detector. It responds only to transitions, hence phase-error is independent of input waveform duty cycle or amplitude variations. Loop lockup occurs when all the negative transitions on the inputs, F\_REF and F\_MOD, coincide. Both outputs (i.e., Up and Down) then remain high. This is equal to the zero error mode. The phase-frequency detector input frequency range operates at 12MHz.

#### **10.6 TRANSMITTER CIRCUITRY**

The transmitter consists of ROM tables, two Digital to Analog (DA) converters, two low-pass filters, IQ mixers, and a power amplifier (PA).

The ROM tables generate a digital IQ signal based on the transmit data. The output of the ROM tables is inserted into IQ-DA converters and filtered through two low-pass filters. The two signal components are mixed up to 2.5 GHz by the TX mixers and added together before being inserted into the transmit PA.

#### 10.6.1 IQ-DA Converters and TX Mixers

The ROM output signals drive an I- and a Q-DA converter. Two Butterworth low-pass filters filter the DA output signals. The 6 MHz clock for the DA converters and the logic circuitry around the ROM tables are derived from the autotuner.

The TX mixers mix the balanced I- and Q-signals up to 2.4-2.5 GHz. The output signals of the I- and Q-mixers are summed.

#### **10.7 CRYSTAL REQUIREMENTS**

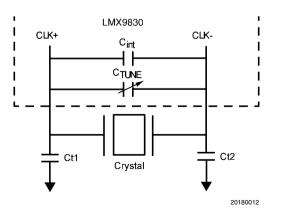

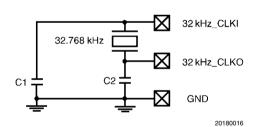

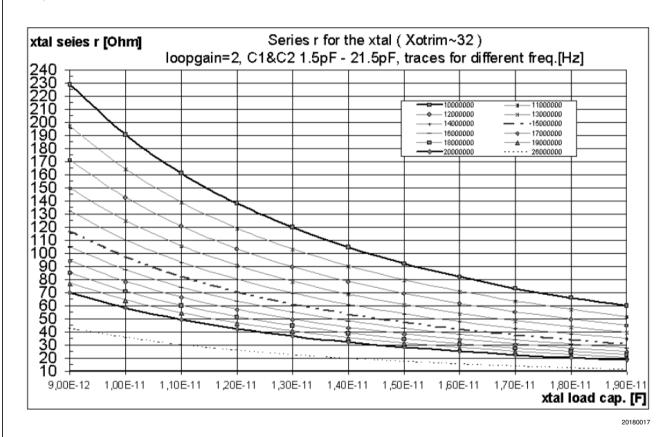

The LMX9830 contains a crystal driver circuit. This circuit operates with an external crystal and capacitors to form an oscillator. shows the recommended crystal circuit. *Table 21* specifies system clock requirements.

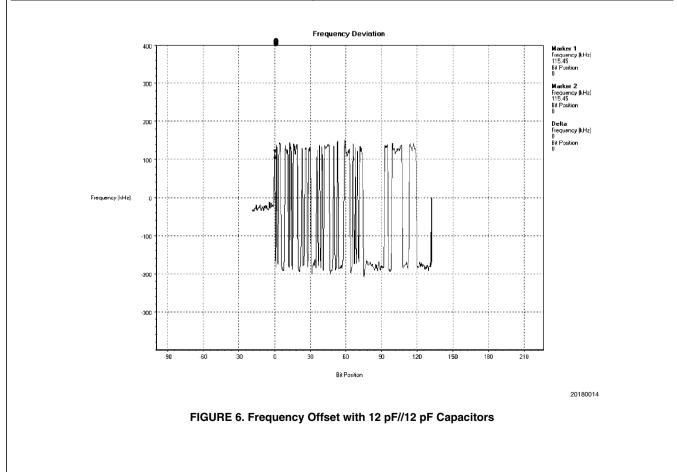

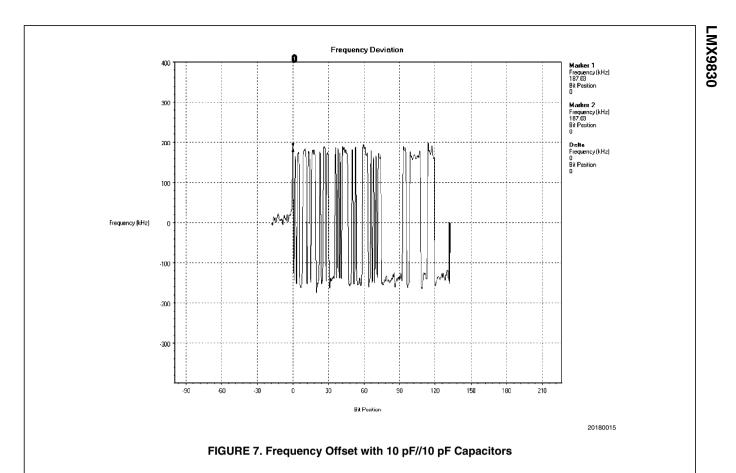

The RF local oscillator and internal digital clocks for the LMX9830 is derived from the reference clock at the CLK+ input. This reference may either come from an external clock or a dedicated crystal oscillator. The crystal oscillator connections require an Xtal and two grounded capacitors.