# LMX2531 High Performance Frequency Synthesizer System with Integrated VCO

## **General Description**

The LMX2531 is a low power, high performance frequency synthesizer system which includes a fully integrated deltasigma PLL and VCO with fully integrated tank circuit. The third and fourth poles are also integrated and also adjustable. Also included are integrated ultra-low noise and high precision LDOs for the PLL and VCO which give higher supply noise immunity and also more consistent performance. When combined with a high quality reference oscillator, the LMX2531 generates very stable, low noise local oscillator signals for up and down conversion in wireless communication devices. The LMX2531 is a monolithic integrated circuit, fabricated in an advanced BiCMOS process. There are several different versions of this product in order to accomodate different frequency bands.

Device programming is facilitated using a three-wire MICROWIRE Interface that can operate down to 1.8 volts.

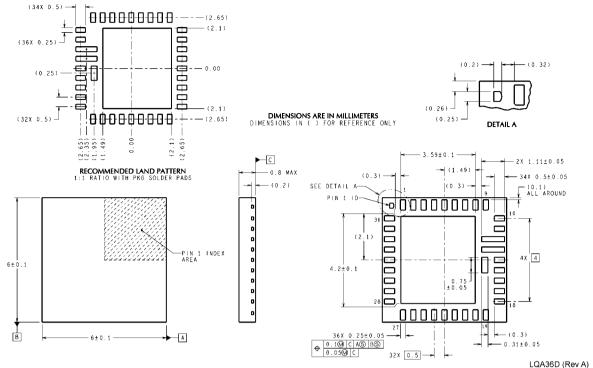

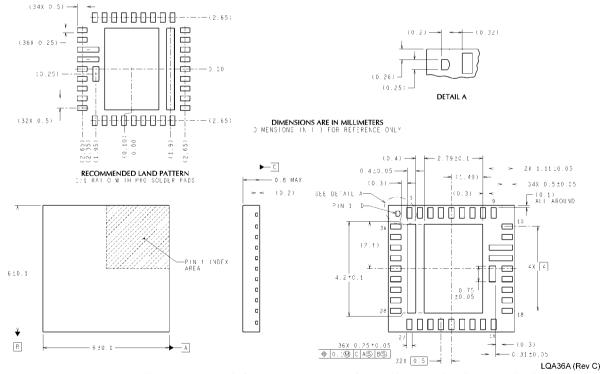

Supply voltage range is 2.8 to 3.2 Volts. The LMX2531 is available in a 36 pin 6x6x0.8 mm Lead-Free Leadless Lead-frame Package (LLP).

## **Target Applications**

- 3G Cellular Base Stations (WCDMA, TD-SCDMA,CDMA2000)

- 2G Cellular Base Stations (GSM/GPRS, EDGE, CDMA1xRTT)

- Wireless LAN

- Broadband Wireless Access

- Satellite Communications

- Wireless Radio

- Automotive

- CATV Equipment

- Instrumentation and Test Equipment

- RFID Readers

#### **Features**

- Multiple Frequency Options Available

- See Selection Guide Below

- Frequencies from: 553 MHz 2790 MHz

#### ■ PLL Features

- Fractional-N Delta Sigma Modulator Order programmable up to 4th order

- FastLock/Cycle Slip Reduction with Timeout Counter

- Partially integrated, adjustable Loop Filter

- Very low phase noise and spurs

#### ■ VCO Features

- Integrated tank inductor

- Low phase noise

#### Other Features

- \_\_ 2.8 V to 3.2 V Operation

- Low Power-Down Current

- 1.8 V MICROWIRE Support

- Package: 36 Lead LLP

| Part           | Low Band        | High Band       |

|----------------|-----------------|-----------------|

| LMX2531LQ1146E | 553 - 592 MHz   | 1106 - 1184 MHz |

| LMX2531LQ1226E | 592 - 634 MHz   | 1184 - 1268 MHz |

| LMX2531LQ1312E | 634 - 680 MHz   | 1268 - 1360 MHz |

| LMX2531LQ1415E | 680 - 735 MHz   | 1360 - 1470 MHz |

| LMX2531LQ1515E | 725 - 790 MHz   | 1450 - 1580 MHz |

| LMX2531LQ1570E | 765 - 818 MHz   | 1530 - 1636 MHz |

| LMX2531LQ1650E | 795 - 850 MHz   | 1590 - 1700 MHz |

| LMX2531LQ1700E | 831 - 885 MHz   | 1662 - 1770 MHz |

| LMX2531LQ1742  | 880 - 933 MHz   | 1760 - 1866 MHz |

| LMX2531LQ1778E | 863 - 920 MHz   | 1726 - 1840 MHz |

| LMX2531LQ1910E | 917 - 1014 MHz  | 1834 - 2028 MHz |

| LMX2531LQ2080E | 952 - 1137 MHz  | 1904 - 2274 MHz |

| LMX2531LQ2265E | 1089 - 1200 MHz | 2178 - 2400 MHz |

| LMX2531LQ2570E | 1168 - 1395 MHz | 2336 - 2790 MHz |

|                |                 |                 |

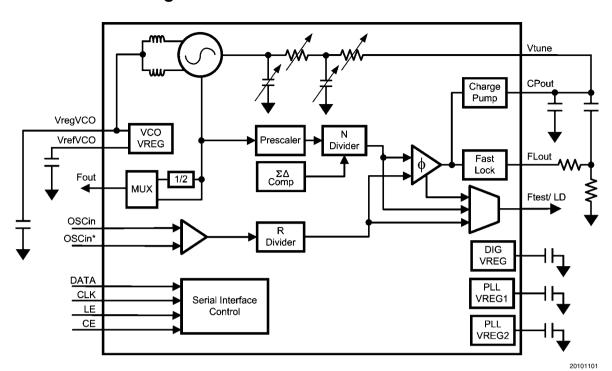

# **Functional Block Diagram**

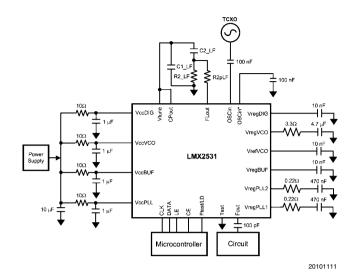

# **Connection Diagrams**

36-Pin LLP (LQ) Package, A Version (All Other Versions)

# Pin Descriptions

| Pin #                         | Pin Name | I/O | Description                                                                                                                                                                                                                                                                                                             |

|-------------------------------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                             | VccDIG   | -   | Power Supply for digital LDO circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                               |

| 3                             | GND      | -   | Ground                                                                                                                                                                                                                                                                                                                  |

| 2,4,5,7,<br>12, 13,<br>29, 35 | NC       | -   | No Connect.                                                                                                                                                                                                                                                                                                             |

| 6                             | VregBUF  | -   | Internally regulated voltage for the VCO buffer circuitry. Connect to ground with a capacitor.                                                                                                                                                                                                                          |

| 8                             | DATA     | ı   | MICROWIRE serial data input. High impedance CMOS input. This pin must not exceed 2.75V. Data is clocked in MSB first. The last bits clocked in form the control or register select bits.                                                                                                                                |

| 9                             | CLK      | ı   | MICROWIRE clock input. High impedance CMOS input. This pin must not exceed 2.75V. Data is clocked into the shift register on the rising edge.                                                                                                                                                                           |

| 10                            | LE       | 1   | MICROWIRE Latch Enable input. High impedance CMOS input. This pin must not exceed 2.75V. Data stored in the shift register is loaded into the selected latch register when LE goes HIGH.                                                                                                                                |

| 11                            | CE       | ı   | Chip Enable Input. High impedance CMOS input. This pin must not exceed 2.75V. When CE is brought high the LMX2531 is powered up corresponding to the internal power control bits. Although the part can be programmed when powered down, it is still necessary to reprogram the R0 register to get the part to re-lock. |

| 14, 15                        | NC       | -   | No Connect. Do NOT ground.                                                                                                                                                                                                                                                                                              |

| 16                            | VccVCO   | -   | Power Supply for VCO regulator circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                             |

| 17                            | VregVCO  | -   | Internally regulated voltage for VCO circuitry. Not intended to drive an external load. Connect to ground with a capacitor and some series resistance.                                                                                                                                                                  |

| 18                            | VrefVCO  | -   | Internal reference voltage for VCO LDO. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                                                                                                     |

| 19                            | GND      | -   | Ground for the VCO circuitry.                                                                                                                                                                                                                                                                                           |

| 20                            | GND      | -   | Ground for the VCO Output Buffer circuitry.                                                                                                                                                                                                                                                                             |

| 21                            | Fout     | 0   | Buffered RF Output for the VCO.                                                                                                                                                                                                                                                                                         |

| 22                            | VccBUF   | -   | Power Supply for the VCO Buffer circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                            |

| 23                            | Vtune    | I   | Tuning voltage input for the VCO. For connection to the CPout Pin through an external passive loop filter.                                                                                                                                                                                                              |

| 24                            | CPout    | 0   | Charge pump output for PLL. For connection to Vtune through an external passive loop filter.                                                                                                                                                                                                                            |

| 25                            | FLout    | 0   | An open drain NMOS output which is used for FastLock or a general purpose output.                                                                                                                                                                                                                                       |

| 26                            | VregPLL1 | -   | Internally regulated voltage for PLL charge pump. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                                                                                           |

| 27                            | VccPLL   | -   | Power Supply for the PLL. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                                             |

| 28                            | VregPLL2 | -   | Internally regulated voltage for RF digital circuitry. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                                                                                      |

| 30                            | Ftest/LD | 0   | Multiplexed CMOS output. Typically used to monitor PLL lock condition.                                                                                                                                                                                                                                                  |

| 31                            | OSCin    | I   | Oscillator input.                                                                                                                                                                                                                                                                                                       |

| 32                            | OSCin*   | I   | Oscillator complimentary input. When a single ended source is used, then a bypass capacitor should be placed as close as possible to this pin and be connected to ground.                                                                                                                                               |

| 33                            | Test     | 0   | This pin is for test purposes and should be grounded for normal operation.                                                                                                                                                                                                                                              |

| 34                            | GND      | -   | Ground                                                                                                                                                                                                                                                                                                                  |

| 36                            | VregDIG  | -   | Internally regulated voltage for LDO digital circuitry.                                                                                                                                                                                                                                                                 |

# **Connection Diagram**

| Pin(s)                               | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VccDIG<br>VccVCO<br>VccBUF<br>VccPLL | These pins are inputs to voltage regulators. Because the LMX2531 contains internal regulators, the power supply noise rejection is very good and capacitors at this pin are not critical. An RC filter can be used to reduce supply noise, but if the capacitor is too large and is placed too close to these pins, they can sometimes cause phase noise degradation in the 100 - 300 kHz offset range. Recommended values are from open to 1 $\mu$ F. The series resistors serve to filter power supply noise and isolate these pins from large capacitances. |

| VregDIG                              | There is not really any reason to use any other values than the recommended value of 10 nF                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VrefVCO                              | If the VrefVCO capacitor is changed, it is recommended to keep this capacitor between 1/100 and 1/1000 of the value of the VregVCO capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VregVCO                              | Because this pin is the output of a regulator, there are stability concerns if there is not sufficient series resistance. For ceramic capacitors, the ESR (Equivalent Series Resistance) is too low, and it is recommended that a series resistance of 1 - $3.3\Omega$ is necessary. If there is insufficient ESR, then there may be degradation in the phase noise, especially in the 100 - 300 kHz offset. Recommended values are from 1 $\mu$ F to 10 $\mu$ F.                                                                                              |

| VregPLL1<br>VregPLL2                 | The choice of the capacitor value at this pin involves a trade-off between integer spurs and phase noise in the 100 - 300 kHz offset range. Using a series resistor of about 220 m $\Omega$ in series with a capacitance that has an impedance of about 150 m $\Omega$ at the phase detector frequency seems to give an optimal trade-off. For instance, if the phase detector frequency is 2.5 MHz, then make this series capacitor 470 nF. If the phase detector frequency is 10 MHz, make this capacitance about 100 nF.                                    |

| CLK<br>DATA<br>LE                    | Since the maximum voltage on these pins is less than the minimum Vcc voltage, level shifting may be required if the output voltage of the microcontroller is too high. This can be accomplished with a resistive divider.                                                                                                                                                                                                                                                                                                                                      |

| CE                                   | As with the CLK, DATA, and LE pins, level shifting may be required if the output voltage of the microcontroller is too high. A resistive divider or a series diode are two ways to accomplish this. The diode has the advantage that no current flows through it when the chip is powered down.                                                                                                                                                                                                                                                                |

| Ftest/LD                             | It is an option to use the lock detect information from this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fout                                 | This is the high frequency output. This needs to be AC coupled, and matching may also be required. The value of the DC blocking capacitor may be changed, depending on the output frequency.                                                                                                                                                                                                                                                                                                                                                                   |

| CPout<br>Vtune                       | In most cases, it is sufficient to short these together, although there always the option of adding additional poles. C1_LF, C2_LF, and R2_LF are used in conjunction with the internal loop filter to make a fourth order loop filter.                                                                                                                                                                                                                                                                                                                        |

| R2pLF                                | This is the fastlock resistor, which can be useful in many cases, since the spurs are often better with low charge pump currents, and the internal loop filter can be adjusted during fastlock.                                                                                                                                                                                                                                                                                                                                                                |

| OSCin                                | This is the reference oscillator input pin. It needs to be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSCin*                               | If the device is being driven single-ended, this pin needs to be shunted to ground with a capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

5

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Parameter                        | Symbol                                                 | Ratings     | Units |

|----------------------------------|--------------------------------------------------------|-------------|-------|

| Power Supply Voltage             | V <sub>CC</sub><br>(VccDIG, VccVCO,<br>VccBUF, VccPLL) | -0.3 to 3.5 | V     |

|                                  | All other pins (Except Ground)                         | -0.3 to 3.0 |       |

| Storage Temperature<br>Range     | T <sub>STG</sub>                                       | -65 to 150  | °C    |

| Lead Temperature (solder 4 sec.) | T <sub>L</sub>                                         | + 260       | °C    |

# **Recommended Operating Conditions**

| Parameter                                     | Symbol         | Min | Тур | Max  | Units |

|-----------------------------------------------|----------------|-----|-----|------|-------|

| Power Supply Voltage (VccDig, VccVCO, VccBUF) | Vcc            | 2.8 | 3.0 | 3.2  | V     |

| Serial Interface and Power Control Voltage    | V <sub>i</sub> | 0   |     | 2.75 | V     |

| Ambient Temperature<br>(Note 4)               | T <sub>A</sub> | -40 |     | +85  | °C    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only to the test conditions listed.

#### **Electrical Characteristics** $(V_{CC} = 3.0 \text{ V}, -40 ^{\circ}\text{C} \le T_{A} \le 85 ^{\circ}\text{C}; \text{ except as specified.})$ Units Symbol Parameter Conditions Min Тур Max **Current Consumption** All Other Options 34 Divider Disabled LMX2531LQ2265E 38 44 /2570E **Power Supply Current Power** $I_{CC}$ mA Supply Current All Other Options 37 46 Divider Enabled LMX2531LQ2265E 41 49 /2570E $I_{CC}PD$ CE = 0 V, Part Initialized Power Down Current 7 μΑ Oscillator I<sub>IH</sub>OSC Oscillator Input High Current $V_{IH} = 2.75 V$ 100 μΑ I<sub>II</sub> OSC $V_{II} = 0$ -100 Oscillator Input Low Current μΑ $\mathbf{f}_{\text{OSCin}}$ Frequency Range 5 80 MHz $v_{\text{OSCin}}$ Oscillator Sensitivity 0.5 2.0 Vpp PLL $f_{PD}$ Phase Detector Frequency 32 MHz ICP = 0μΑ 90 ICP = 1 180 μΑ Charge Pump I<sub>CPout</sub> **Output Current Magnitude** ICP = 3360 μΑ ICP = 15 1440 μΑ $I_{CPout}TRI$ **CP TRI-STATE Current** $0.4 \text{ V} < \text{V}_{\text{CPout}} < 2.0 \text{ V}$ 2 10 nΑ $V_{CPout} = \overline{1.2} \overline{V}$ Charge Pump $I_{CPout}MM$ 2 8 % Sink vs. Source Mismatch $T_A = 25^{\circ}C$ Charge Pump $0.4 \text{ V} < \text{V}_{\text{CPout}} < 2.0 \text{ V}$ Current vs. CP Voltage $I_{CPout}V$ 4 % $T_A = 25^{\circ}C$ Variation CP Current vs. Temperature $V_{CPout} = 1.2 V$ 8 % $I_{CPout}T$ Variation Normalized PLL 1/f Noise ICP = 1X Charge Pump Gain -94 $LN_{PLL\_flicker}(10 \text{ kHz})$ dBc/Hz ICP = 16X Charge Pump Gain -104 (Note 2) LN(f) Normalized PLL Noise Floor ICP = 1X Charge Pump Gain -202 dBc/Hz LN<sub>PLL flat</sub> ICP = 16X Charge Pump Gain -212 (Note 3)

| Symbol            | Parameter                                                         | Conditions      | Min            | Тур            | Max  | Units   |      |  |

|-------------------|-------------------------------------------------------------------|-----------------|----------------|----------------|------|---------|------|--|

|                   |                                                                   | VCO Frequencies |                |                |      |         |      |  |

|                   |                                                                   | LMX2531LQ1146E  | 1106           |                | 1184 |         |      |  |

|                   |                                                                   | LMX2531LQ1226E  | 1184           |                | 1268 |         |      |  |

|                   |                                                                   | LMX2531LQ1312E  | 1268           |                | 1360 |         |      |  |

|                   |                                                                   | LMX2531LQ1415E  | 1360           |                | 1470 |         |      |  |

|                   | Operating Frequency Range                                         |                 |                | LMX2531LQ1515E | 1450 |         | 1580 |  |

|                   |                                                                   |                 | LMX2531LQ1570E | 1530           |      | 1636    | 3    |  |

|                   | (All options have a frequency                                     | LMX2531LQ1650E  | 1590           |                | 1700 | N 41 1- |      |  |

| f <sub>Fout</sub> | divider, this applies before the divider. The frequency after the | LMX2531LQ1700E  | 1662           |                | 1770 | MHz     |      |  |

|                   | divider is half of what is shown)                                 | LMX2531LQ1742   | 1760           |                | 1866 |         |      |  |

|                   |                                                                   | LMX2531LQ1778E  | 1726           |                | 1840 |         |      |  |

|                   |                                                                   | LMX2531LQ1910E  | 1834           |                | 2028 |         |      |  |

|                   |                                                                   | LMX2531LQ2080E  | 1904           |                | 2274 |         |      |  |

|                   |                                                                   | LMX2531LQ2265E  | 2178           |                | 2400 |         |      |  |

|                   |                                                                   | LMX2531LQ2570E  | 2336           |                | 2790 |         |      |  |

| Symbol             | Parameter                                                        |                  | Conditions                       | Min | Тур         | Max | Units |  |

|--------------------|------------------------------------------------------------------|------------------|----------------------------------|-----|-------------|-----|-------|--|

|                    |                                                                  | Other VCC        | ) Specifications                 |     |             |     |       |  |

|                    |                                                                  | LI               | MX2531LQ1742                     | 65  |             |     |       |  |

|                    | Maximum Allowable Temperature Drift for                          | LMX2531LQ1570E/  | 1650E/1146E/1226/1312E/1415E/    | 90  |             |     |       |  |

| $\Delta T_{CL}$    | Continuous Lock                                                  |                  | 1515E                            | 90  |             |     | °C    |  |

|                    | (Note 4)                                                         | LMX2531LQ1700    | DE/1778E/1910E/2080E/2265E/      | 125 |             |     |       |  |

|                    | , , ,                                                            |                  | 2570E                            | 120 |             |     |       |  |

|                    |                                                                  |                  | LMX2531LQ1146E                   | 1   | 4.0         | 7   |       |  |

|                    |                                                                  |                  | LMX2531LQ1226E                   | 1   | 3.5         | 7   |       |  |

|                    |                                                                  |                  | LMX2531LQ1312E                   | 1   | 3.5         | 7   |       |  |

|                    |                                                                  |                  | LMX2531LQ1415E                   | 0   | 3.0         | 6   |       |  |

|                    |                                                                  |                  | LMX2531LQ1515E                   | -1  | 2.5         | 5   |       |  |

|                    |                                                                  |                  | LMX2531LQ1570E                   | 2   | 4.5         | 8   |       |  |

|                    |                                                                  | Divider Disabled | LMX2531LQ1650E                   | 2   | 4.5         | 8   | dBm   |  |

|                    |                                                                  | 2                | LMX2531LQ1700E                   | 1   | 3.5         | 7   |       |  |

|                    |                                                                  |                  | LMX2531LQ1742                    | 1   | 3.5         | 7   |       |  |

|                    |                                                                  |                  | LMX2531LQ1778E                   | 1   | 3.5         | 7   |       |  |

|                    |                                                                  |                  | LMX2531LQ1910E                   | 1   | 3.5         | 7   |       |  |

|                    |                                                                  |                  | LMX2531LQ2080E                   | 1   | 3.5         | 7   |       |  |

|                    | Output Dower to a FO O Load                                      |                  | LMX2531LQ2265E                   | 1   | 3.5         | 7   |       |  |

| $p_{Fout}$         | Output Power to a 50 $\Omega$ Load (Applies across entire tuning |                  | LMX2531LQ2570E                   | 0   | 3.0         | 6   |       |  |

| FFout              | range.)                                                          |                  | LMX2531LQ1146E                   | -1  | 2.0         | 5   | - dBm |  |

|                    |                                                                  |                  | LMX2531LQ1226E                   | -1  | 2.0         | 5   |       |  |

|                    |                                                                  |                  | LMX2531LQ1312E                   | -1  | 1.5         | 4   |       |  |

|                    |                                                                  |                  | LMX2531LQ1415E                   | -2  | 0.5         | 3   |       |  |

|                    |                                                                  | Divider Enabled  | LMX2531LQ1515E                   | -2  | 0.5         | 3   |       |  |

|                    |                                                                  |                  | LMX2531LQ1570E                   | 1   | 3.0         | 6   |       |  |

|                    |                                                                  |                  | LMX2531LQ1650E                   | 1   | 3.0         | 6   |       |  |

|                    |                                                                  | 2111001 21100100 | LMX2531LQ1700E                   | 1   | 3.0         | 6   |       |  |

|                    |                                                                  |                  | LMX2531LQ1742                    | 1   | 3.0         | 6   |       |  |

|                    |                                                                  |                  | LMX2531LQ1778E                   | 1   | 3.0         | 6   |       |  |

|                    |                                                                  |                  | LMX2531LQ1910E                   | 1   | 3.0         | 6   |       |  |

|                    |                                                                  |                  | LMX2531LQ2080E                   | 0   | 2.5         | 5   |       |  |

|                    |                                                                  |                  | LMX2531LQ2265E                   | 0   | 2.5         | 5   |       |  |

|                    |                                                                  |                  | LMX2531LQ2570E                   | -1  | 1.5         | 4   |       |  |

|                    |                                                                  | LN               | /X2531LQ1146E                    |     | 2.5         |     |       |  |

|                    |                                                                  |                  |                                  |     | -5.5        |     |       |  |

|                    |                                                                  |                  | 1X2531LQ1226E                    |     | 3-6         |     |       |  |

|                    |                                                                  | LN               | 1X2531LQ1312E                    |     | 3-6         |     |       |  |

|                    | Fine Tuning Sensitivity                                          | LN               | /IX2531LQ1415E                   |     | 3.5         |     |       |  |

|                    | (When a range is displayed in                                    | 1.5              | MX2531LQ1515E                    |     | -6.5<br>4-7 |     |       |  |

|                    | the typical column, indicates the                                |                  |                                  |     |             |     |       |  |

| K <sub>Vtune</sub> | lower sensitivity is typical at the                              |                  | MX2531LQ1570E<br>MX2531LQ1650E   |     | 4-7<br>4-7  |     | MHz/\ |  |

|                    | lower end of the tuning range, and the higher tuning sensitivity |                  | 1X2531LQ1650E<br>1X2531LQ1700E   |     | 6-10        |     |       |  |

|                    | is typical at the higher end of the                              |                  | MX2531LQ1740E                    |     | 4-7         |     |       |  |

|                    | tuning range.)                                                   |                  | MX2531LQ1742<br>MX2531LQ1778E    |     | 6-10        |     |       |  |

|                    |                                                                  |                  |                                  |     | 8-14        |     |       |  |

|                    |                                                                  |                  | MX2531LQ1910E<br>MX2531LQ2080E   |     | 9-20        |     |       |  |

|                    |                                                                  |                  | //X2531LQ2080E<br>//X2531LQ2265E |     | 10-16       |     |       |  |

|                    |                                                                  |                  | //X2531LQ2265E<br>//X2531LQ2570E |     | 10-16       |     |       |  |

|                    |                                                                  | LIV              | INCOUTEWED/UE                    |     | 10-23       |     |       |  |

9

| Symbol               | Parameter                     |                                 | Conditions               |                                                | Min                                            | Тур | Max  | Units |  |

|----------------------|-------------------------------|---------------------------------|--------------------------|------------------------------------------------|------------------------------------------------|-----|------|-------|--|

|                      | Harmonic Suppression          |                                 | Divider<br>Disabled      | LMX2531LQ1146E<br>/1226E/1312E<br>/1415E/1515E |                                                | -35 | -25  |       |  |

|                      |                               | 2nd Harmonic                    |                          | All Other Options                              |                                                | -30 | -25  |       |  |

|                      |                               | 50 Ω Load  Harmonic Suppression | Divider<br>Enabled       | LMX2531LQ1146E<br>/1226E/1312E<br>/1415E/1515E |                                                | -30 | -20  |       |  |

| $HS_Fout$            | (Applies Across Entire Tuning |                                 |                          | All Other Options                              |                                                | -20 | -15  | dBc   |  |

|                      | Range)                        |                                 | Divider<br>Disabled      | LMX2531LQ1146E<br>/1226E/1312E                 |                                                | -35 | -30  |       |  |

|                      |                               | 3rd Harmonic                    | Disabled                 | All Other Options                              |                                                | -40 | -35  |       |  |

|                      |                               | 50 Ω Load                       |                          | Divider<br>Enabled                             | LMX2531LQ1146E<br>/1226E/1312E<br>/1570E/1650E |     | -20  | -15   |  |

|                      |                               |                                 |                          | All Other Options                              |                                                | -25 | -20  |       |  |

| PUSH <sub>Fout</sub> | Frequency Pushing             | Creg = 0.1uF                    | , V <sub>DD</sub> ± 100m | V, Open Loop                                   |                                                | 300 |      | kHz/V |  |

| PULL <sub>Fout</sub> | Frequency Pulling             | VSW                             | R = 2:1, Open            | Loop                                           |                                                |     | ±600 | kHz   |  |

| Z <sub>Fout</sub>    | Output Impedance              |                                 |                          |                                                |                                                | 50  |      | Ω     |  |

| Symbol                                | Parameter                       | Co                                    | onditions                             | Min | Тур         | Max | Units   |

|---------------------------------------|---------------------------------|---------------------------------------|---------------------------------------|-----|-------------|-----|---------|

|                                       |                                 | VCO Phase N                           | oise (Note 5)                         |     |             |     |         |

|                                       |                                 |                                       | 10 kHz Offset                         |     | -96         |     |         |

|                                       |                                 | f <sub>Fout</sub> = 1146 MHz          | 100 kHz Offset                        |     | -121        |     |         |

|                                       |                                 | DIV2 = 0                              | 1 MHz Offset                          |     | -142        |     |         |

|                                       | Phase Noise                     |                                       | 5 MHz Offset                          |     | -156        |     |         |

| L(f) <sub>Fout</sub>                  | (LMX2531LQ1146E)                |                                       | 10 kHz Offset                         |     | -101        |     | dBc/H   |

|                                       | ,                               | f <sub>Fout</sub> = 573 MHz           | 100 kHz Offset                        |     | -126        |     |         |

|                                       |                                 | DIV2 = 1                              | 1 MHz Offset                          |     | -147        |     |         |

|                                       |                                 |                                       | 5 MHz Offset                          |     | -156        |     |         |

|                                       |                                 |                                       | 10 kHz Offset                         |     | -95         |     |         |

|                                       |                                 | f <sub>Fout</sub> = 1226 MHz          | 100 kHz Offset                        |     | -121        |     |         |

|                                       |                                 | DIV2 = 0                              | 1 MHz Offset                          |     | -142        |     |         |

|                                       | Phase Noise                     |                                       | 5 MHz Offset                          |     | -155        |     |         |

| L(f) <sub>Fout</sub>                  | (LMX2531LQ1226E)                |                                       | 10 kHz Offset                         |     | -101        |     | dBc/F   |

|                                       | (=, (=00 : = 0 : ==0 =)         | f <sub>Fout</sub> = 613 MHz           | 100 kHz Offset                        |     | -126        |     |         |

|                                       |                                 | DIV2 = 1                              | 1 MHz Offset                          | +   | -147        |     |         |

|                                       |                                 |                                       | 5 MHz Offset                          |     | -155        |     |         |

|                                       |                                 |                                       | 10 kHz Offset                         |     | -155        |     |         |

|                                       |                                 | f _ 1014 MU=                          | 100 kHz Offset                        |     | -95<br>-121 |     |         |

| L(f) <sub>Fout</sub>                  |                                 | f <sub>Fout</sub> = 1314 MHz DIV2 = 0 |                                       | +   |             |     |         |

|                                       | Dhara Naisa                     | DIV2 = 0                              | 1 MHz Offset                          | -   | -140        |     |         |

|                                       | Phase Noise<br>(LMX2531LQ1312E) |                                       | 5 MHz Offset                          |     | -154        |     | dBc/F   |

|                                       | (LIVIAZOSTEQTSTZE)              | ( 057.141                             | 10 kHz Offset                         |     | -101        |     |         |

|                                       |                                 | f <sub>Fout</sub> = 657 MHz           | 100 kHz Offset                        | _   | -126        |     |         |

|                                       |                                 | DIV2 = 1                              | 1 MHz Offset                          | _   | -146        |     |         |

|                                       |                                 |                                       | 5 MHz Offset                          | _   | -154        |     |         |

|                                       |                                 |                                       | 10 kHz Offset                         | -   | -95         |     |         |

|                                       |                                 | f <sub>Fout</sub> = 1415 MHz          | 100 kHz Offset                        | _   | -121        |     |         |

|                                       |                                 | DIV2 = 0                              | 1 MHz Offset                          | _   | -141        |     |         |

| L(f) <sub>Fout</sub>                  | Phase Noise                     |                                       | 5 MHz Offset                          |     | -154        |     | dBc/F   |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | (LMX2531LQ1415E)                |                                       | 10 kHz Offset                         |     | -100        |     | UBC/112 |

|                                       |                                 | f <sub>Fout</sub> = 707.5 MHz         | 100 kHz Offset                        |     | -126        |     |         |

|                                       |                                 | DIV2 = 1                              | 1 MHz Offset                          |     | -146        |     |         |

|                                       |                                 |                                       | 5 MHz Offset                          |     | -154        |     |         |

|                                       |                                 |                                       | 10 kHz Offset                         |     | -96         |     |         |

|                                       |                                 | f <sub>Fout</sub> = 1515 MHz          | 100 kHz Offset                        |     | -122        |     |         |

|                                       |                                 | DIV2 = 0                              | 1 MHz Offset                          |     | -142        |     |         |

| L(f) <sub>Fout</sub>                  | Phase Noise                     |                                       | 5 MHz Offset                          |     | -153        |     | dBc/F   |

| ーいFout                                | (LMX2531LQ1515E)                |                                       | 10 kHz Offset                         |     | -99         |     | ubt/F   |

|                                       |                                 | f <sub>Fout</sub> = 757.5 MHz         | 100 kHz Offset                        |     | -125        |     |         |

|                                       |                                 | DIV2 = 1                              | 1 MHz Offset                          |     | -145        |     |         |

|                                       |                                 |                                       | 5 MHz Offset                          |     | -154        |     |         |

|                                       |                                 |                                       | 10 kHz Offset                         |     | -93         |     |         |

|                                       |                                 | f <sub>Fout</sub> = 1583 MHz          | 100 kHz Offset                        |     | -118        |     |         |

|                                       |                                 | DIV2 = 0                              | 1 MHz Offset                          |     | -140        |     |         |

|                                       | Phase Noise                     |                                       | 5 MHz Offset                          |     | -154        |     |         |

| L(f) <sub>Fout</sub>                  | (LMX2531LQ1570E)                |                                       | 10 kHz Offset                         |     | -99         |     | dBc/F   |

|                                       | ,                               | f <sub>Fout</sub> = 791.5 MHz         | 100 kHz Offset                        |     | -122        |     |         |

|                                       |                                 |                                       | 1 MHz Offset                          |     | -144        |     |         |

|                                       |                                 | DIV2 = 1                              | DIV2 = 1 1 MHz Offset<br>5 MHz Offset | -   | -155        |     |         |

| Symbol               | Parameter                       |                                        | Conditions     | Min     | Тур  | Max                    | Units  |

|----------------------|---------------------------------|----------------------------------------|----------------|---------|------|------------------------|--------|

|                      |                                 |                                        | 10 kHz Offset  |         | -93  |                        |        |

|                      |                                 | f <sub>Fout</sub> = 1645 MHz           | 100 kHz Offset |         | -118 |                        |        |

|                      |                                 | DIV2 = 0                               | 1 MHz Offset   |         | -140 |                        |        |

|                      | Phase Noise                     |                                        | 5 MHz Offset   |         | -154 |                        |        |

| L(f) <sub>Fout</sub> | (LMX2531LQ1650E)                |                                        | 10 kHz Offset  |         | -99  |                        | dBc/H  |

|                      | ,                               | f <sub>Fout</sub> = 822.5 MHz          | 100 kHz Offset |         | -122 |                        |        |

|                      |                                 | DIV2 = 1                               | 1 MHz Offset   |         | -144 |                        |        |

|                      |                                 |                                        | 5 MHz Offset   |         | -155 |                        |        |

|                      |                                 |                                        | 10 kHz Offset  |         | -92  |                        |        |

|                      |                                 | f <sub>Fout</sub> = 1716 MHz           | 100 kHz Offset |         | -117 |                        |        |

|                      |                                 | DIV2 = 0                               | 1 MHz Offset   |         | -139 |                        |        |

|                      | Dhaca Naisa                     | BIVE = 0                               | 5 MHz Offset   |         | -153 |                        |        |

| L(f) <sub>Fout</sub> | Phase Noise<br>(LMX2531LQ1700E) |                                        | 10 kHz Offset  |         |      |                        | dBc/F  |

|                      | (LIVIAZ33TLQ1700L)              | 4 050 MH-                              |                |         | -98  | -                      |        |

|                      |                                 | f <sub>Fout</sub> = 858 MHz            | 100 kHz Offset |         | -122 |                        |        |

|                      |                                 | DIV2 = 1                               | 1 MHz Offset   | -       | -144 |                        |        |

|                      |                                 | +                                      | 5 MHz Offset   | _       | -154 |                        |        |

|                      |                                 |                                        | 10 kHz Offset  | $\perp$ | -92  |                        |        |

|                      |                                 | f <sub>Fout</sub> = 1813 MHz           | 100 kHz Offset |         | -117 |                        |        |

| L(f) <sub>Fout</sub> |                                 | DIV2 = 0                               | 1 MHz Offset   |         | -140 |                        |        |

|                      | Phase Noise                     |                                        | 5 MHz Offset   |         | -152 |                        | dBc/F  |

| -\'/Fout             | (LMX2531LQ1742)                 |                                        | 10 kHz Offset  |         | -99  |                        | GB6/11 |

|                      |                                 | f <sub>Fout</sub> = 906.5 MHz          | 100 kHz Offset |         | -122 |                        |        |

|                      |                                 | DIV2 = 1                               | 1 MHz Offset   |         | -143 |                        |        |

|                      |                                 |                                        | 5 MHz Offset   |         | -152 |                        |        |

|                      |                                 |                                        | 10 kHz Offset  |         | -92  |                        |        |

|                      |                                 | f <sub>Fout</sub> = 1783 MHz           | 100 kHz Offset |         | -117 |                        |        |

|                      |                                 | DIV2 = 0                               | 1 MHz Offset   |         | -139 |                        |        |

|                      | Phase Noise                     |                                        | 5 MHz Offset   |         | -152 |                        |        |

| L(f) <sub>Fout</sub> | (LMX2531LQ1778E)                |                                        | 10 kHz Offset  |         | -97  |                        | dBc/Hz |

|                      |                                 | f <sub>Fout</sub> = 891.5 MHz          | 100 kHz Offset |         | -122 |                        |        |

|                      |                                 | DIV2 = 1                               | 1 MHz Offset   |         | -144 |                        |        |

|                      |                                 |                                        | 5 MHz Offset   |         | -154 |                        |        |

|                      |                                 | +                                      | 10 kHz Offset  |         | -89  |                        |        |

|                      |                                 | f <sub>Fout</sub> = 1931 MHz           | 100 kHz Offset | _       | -115 |                        | -      |

|                      |                                 | DIV2 = 0                               | 1 MHz Offset   |         | -138 |                        |        |

|                      | Phase Noise                     | 52 - v                                 | 5 MHz Offset   |         | -151 | $\vdash \vdash$        |        |

| L(f) <sub>Fout</sub> | (LMX2531LQ1910E)                |                                        | 10 kHz Offset  | +       | -95  |                        | dBc/F  |

|                      | (2000/20010102)                 | f _ 065 5 MU-                          | 100 kHz Offset |         | -121 |                        |        |

|                      |                                 | f <sub>Fout</sub> = 965.5 MHz DIV2 = 1 | 1 MHz Offset   |         |      | $\vdash \vdash \vdash$ |        |

|                      |                                 |                                        |                |         | -143 |                        |        |

|                      |                                 | +                                      | 5 MHz Offset   |         | -155 |                        |        |

|                      |                                 |                                        | 10 kHz Offset  |         | -87  | $\vdash$               |        |

|                      |                                 | f <sub>Fout</sub> = 2089 MHz           | 100 kHz Offset | _       | -113 | $\vdash \vdash \vdash$ |        |

|                      |                                 | DIV2 = 0                               | 1 MHz Offset   |         | -136 |                        |        |

| L(f) <sub>Fout</sub> | Phase Noise                     |                                        | 5 MHz Offset   | $\bot$  | -150 |                        | dBc/F  |

| · /I out             | (LMX2531LQ2080E)                |                                        | 10 kHz Offset  |         | -93  |                        |        |

|                      |                                 | f <sub>Fout</sub> = 1044.5 MHz         | 100 kHz Offset |         | -119 |                        |        |

|                      |                                 | DIV2 = 1                               | 1 MHz Offset   |         | -142 |                        |        |

|                      |                                 |                                        | 5 MHz Offset   | _ I     | -154 |                        |        |

| Symbol               | Parameter        |                                | Conditions     | Min  | Тур  | Max | Units   |

|----------------------|------------------|--------------------------------|----------------|------|------|-----|---------|

|                      |                  |                                | 10 kHz Offset  |      | -88  |     |         |

|                      |                  | f <sub>Fout</sub> = 2264 MHz   | 100 kHz Offset |      | -113 |     |         |

|                      |                  | DIV2 = 0                       | 1 MHz Offset   |      | -136 |     |         |

| I (f)                | Phase Noise      |                                | 5 MHz Offset   |      | -150 |     | dBc/Hz  |

| L(f) <sub>Fout</sub> | (LMX2531LQ2265E) |                                | 10 kHz Offset  |      | -94  |     | UDC/FIZ |

|                      |                  | f <sub>Fout</sub> = 1132 MHz   | 100 kHz Offset |      | -118 |     |         |

|                      | DIV2 = 1         | DIV2 = 1                       | 1 MHz Offset   |      | -141 |     |         |

|                      |                  | 5 MHz Offset                   |                | -154 |      |     |         |

|                      |                  |                                | 10 kHz Offset  |      | -86  |     |         |

|                      |                  | f <sub>Fout</sub> = 2563 MHz   | 100 kHz Offset |      | -112 |     |         |

|                      |                  | DIV2 = 0                       | 1 MHz Offset   |      | -135 |     |         |

| I (f)                | Phase Noise      |                                | 5 MHz Offset   |      | -149 |     | dBc/Hz  |

| L(f) <sub>Fout</sub> | (LMX2531LQ2570E) |                                | 10 kHz Offset  |      | -91  |     | UDC/FIZ |

|                      |                  | f <sub>Fout</sub> = 1281.5 MHz | 100 kHz Offset |      | -117 |     |         |

|                      |                  | DIV2 = 1                       | 1 MHz Offset   |      | -139 |     |         |

|                      |                  |                                | 5 MHz Offset   |      | -152 |     |         |

| Symbol           | Parameter                   | Conditions                                        | Min  | Тур  | Max  | Units |

|------------------|-----------------------------|---------------------------------------------------|------|------|------|-------|

|                  | Digit                       | al Interface (DATA, CLK, LE, CE, Ftest/LD, FLout) | •    |      |      |       |

| V <sub>IH</sub>  | High-Level Input Voltage    |                                                   | 1.6  |      | 2.75 | V     |

| V <sub>IL</sub>  | Low-Level Input Voltage     |                                                   |      |      | 0.4  | V     |

| I <sub>IH</sub>  | High-Level Input Current    | V <sub>IH</sub> = 1.75                            | -3.0 |      | 3.0  | μΑ    |

| I <sub>IL</sub>  | Low-Level Input Current     | V <sub>IL</sub> = 0 V                             | -3.0 |      | 3.0  | μA    |

| V <sub>OH</sub>  | High-Level Output Voltage   | I <sub>OH</sub> = 500 μA                          | 2.0  | 2.65 |      | V     |

| V <sub>OL</sub>  | Low-Level Output Voltage    | I <sub>OL</sub> = -500 μA                         |      | 0.0  | 0.4  | V     |

|                  |                             | MICROWIRE Timing                                  |      |      |      |       |

| t <sub>CS</sub>  | Data to Clock Set Up Time   | See Data Input Timing                             | 25   |      |      | ns    |

| t <sub>CH</sub>  | Data to Clock Hold Time     | See Data Input Timing                             | 20   |      |      | ns    |

| $t_{CWH}$        | Clock Pulse Width High      | See Data Input Timing                             | 25   |      |      | ns    |

| $t_{CWL}$        | Clock Pulse Width Low       | See Data Input Timing                             | 25   |      |      | ns    |

| t <sub>ES</sub>  | Clock to Enable Set Up Time | See Data Input Timing                             | 25   |      |      | ns    |

| t <sub>CES</sub> | Enable to Clock Set Up Time | See Data Input Timing                             | 25   |      |      | ns    |

| t <sub>EWH</sub> | Enable Pulse Width High     | See Data Input Timing                             | 25   |      |      | ns    |

Note 2: One of the specifications for modeling PLL in-band phase noise is the PLL 1/f noise normalized to 1 GHz carrier frequency and 10 kHz offset,  $L_{PLL\_flicker}$  (10 kHz). From this normalized index of PLL 1/f noise, the PLL 1/f noise can be calculated for any carrier and offset frequency as:  $L_{PLL\_flicker}$  (10 kHz) - 10-log(10 kHz/f) + 20-log(Fout / 1 GHz). Flicker noise can dominate at low offsets from the carrier and has a 10 dB/decade slope and improves with higher charge pump currents and at higher offset frequencies . To accurately measure  $L_{PLL\_flicker}$  (10 kHz) it is important to use a high phase detector frequency and a clean reference to make it such that this measurement is on the 10 dB/decade slope close to the carrier.  $L_{PLL\_flicker}$  (f) can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL in-band phase noise performance is the sum of  $L_{PLL\_flicker}$  (f) and  $L_{PLL\_flicker}$ . In other words,  $L_{PLL}$  (f) = 10-log(10( $L_{PLL\_flicker}$  (f) 10)

Note 3: A specification used for modeling PLL in-band phase noise floor is the Normalized PLL noise floor,  $LN_{PLL\_flat}$ , and is defined as:  $LN_{PLL\_flat} = L(f) - 20 \cdot log(N) - 10 \cdot log(f_{PD})$ .  $L_{PLL\_flat}$  is the single side band phase noise in a 1 Hz Bandwidth and  $f_{PD}$  is the phase detector frequency of the synthesizer.  $L_{PLL\_flat}$  contributes to the total noise, L(f). To measure  $L_{PLL\_flat}$  the offset frequency must be chosen sufficiently smaller then the loop bandwidth of the PLL, and yet large enough to avoid a substantial noise contribution from the reference and PLL flicker noise.  $L_{PLL\_flat}$  can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL in-band phase noise performance is the sum of  $L_{PLL\_flat}$  in other words,  $L_{PLL\_flat}$  10 ·log( $10(LN_{PLL\_flat})$  10 ·log(10

Note 4: Maximum Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction from the value it was at the time that the R0 register was last programmed, and still have the part stay in lock. The action of programming the R0 register, even to the same value, activates a frequency calibration routine. This implies that the part will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reload the R0 register to ensure that it stays in lock. Regardless of what temperature the part was initially programmed at, the temperature can never drift outside the frequency range of -40°C  $\leq$ T<sub>A</sub> $\leq$  85°C without violating specifications.

Note 5: The VCO phase noise is measured assuming that the loop bandwidth is sufficiently narrow that the VCO noise dominates. The maximum limits apply only at center frequency and over temperature, assuming that the part is reloaded at each test frequency. Over frequency, the phase noise can vary 1 to 2 dB, with the worst case performance typically occurring at the highest frequency. Over temperature, the phase noise typically varies 1 to 2 dB, assuming the part is reloaded.

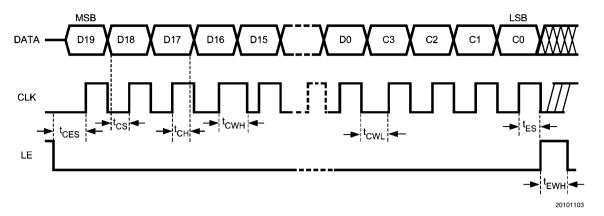

# **Serial Data Timing Diagram**

The DATA is clocked into a shift register on each rising edge of the CLK signal. On the rising edge of the LE signal, the data is sent from the shift registers to an actual counter. A slew rate of at least 30 V/µs is recommended for these signals. After the programming is complete, the CLK, DATA, and LE signals should be returned to a low state. Although it is strongly recommended to keep LE low after programming, LE can be kept high if bit R5[23] is changed to 0 (from its default value of 1). If this bit is changed, then the operation of the part is not guaranteed because it is not tested under these conditions. If the CLK and DATA lines are toggled while the in VCO is in lock, as is sometimes the case when these lines are shared with other parts, the phase noise may be degraded during the time of this programming.

# **Typical Performance Characteristics**

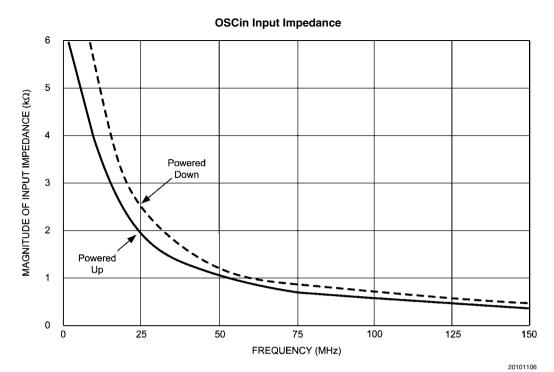

| Frequency |      | Powered Up (kΩ) | l         | F    | Powered Down (kg | Ω)        |

|-----------|------|-----------------|-----------|------|------------------|-----------|

| (MHz)     | Real | Imaginary       | Magnitude | Real | Imaginary        | Magnitude |

| 1         | 4.98 | -2.70           | 5.66      | 6.77 | -8.14            | 10.59     |

| 5         | 3.44 | -3.04           | 4.63      | 5.73 | -6.72            | 9.03      |

| 10        | 1.42 | -2.67           | 3.02      | 1.72 | -5.24            | 5.51      |

| 20        | 0.52 | -1.63           | 1.71      | 0.53 | -2.94            | 2.98      |

| 30        | 0.29 | -1.22           | 1.25      | 0.26 | -2.12            | 2.14      |

| 40        | 0.18 | -0.92           | 0.94      | 0.17 | -1.58            | 1.59      |

| 50        | 0.13 | -0.74           | 0.75      | 0.14 | -1.24            | 1.25      |

| 60        | 0.10 | -0.63           | 0.64      | 0.10 | -1.06            | 1.06      |

| 70        | 0.09 | -0.56           | 0.56      | 0.09 | -0.95            | 0.95      |

| 80        | 0.07 | -0.50           | 0.50      | 0.08 | -0.86            | 0.87      |

| 90        | 0.07 | -0.46           | 0.46      | 0.07 | -0.80            | 0.80      |

| 100       | 0.06 | -0.41           | 0.42      | 0.07 | -0.72            | 0.72      |

| 110       | 0.06 | -0.37           | 0.38      | 0.07 | -0.65            | 0.65      |

| 120       | 0.05 | -0.34           | 0.34      | 0.06 | -0.59            | 0.59      |

| 130       | 0.05 | -0.32           | 0.32      | 0.06 | -0.55            | 0.55      |

| 140       | 0.04 | -0.29           | 0.30      | 0.05 | -0.50            | 0.50      |

| 150       | 0.04 | -0.27           | 0.28      | 0.05 | -0.47            | 0.47      |

## 1.0 Functional Description

The LMX2531 is a low power, high performance frequency synthesizer system which includes the PLL, VCO, and partially integrated loop filter. The following sections give a discussion of the various blocks of this device.

#### 1.1 REFERENCE OSCILLATOR INPUT

Because the VCO frequency calibration algorithm is based on clocks from the OSCin pin, there are certain bits that need to be set depending on the OSCin frequency. XTLSEL (R6[22:20]) and XTLDIV (R7[9:8]) are both need to be set based on the OSCin frequency, f<sub>OSCin</sub>. For some options and for low OSCin frequencies, the XTLMAN (R7[21:10]) and XTLMAN2 (R8[4]) words need to be set to the correct value.

#### 1.2 R DIVIDER

The R divider divides the OSCin frequency down to the phase detector frequency. The R divider value, R, is restricted to the values of 1, 2, 4, 8, 16, and 32. If R is greater than 8, then this also puts restrictions on the fractional denominator, FDEN, than can be used. This is discussed in greater depth in later sections.

#### 1.3 PHASE DETECTOR AND CHARGE PUMP

The phase detector compares the outputs of the R and N dividers and puts out a correction current corresponding to the phase error. The phase detector frequency,  $f_{PD}$ , can be calculated as follows:

$$f_{PD} = f_{OSCin} / R$$

Choosing R = 1 yields the highest possible phase detector frequency and is optimum for phase noise, although there are restrictions on the maximum phase detector frequency which could force the R value to be larger. The far out PLL noise improves 3 dB for every doubling of the phase detector frequency, but at lower offsets, this effect is much less due to the PLL 1/f noise. Aside from getting the best PLL phase noise, higher phase detector frequencies also make it easier to filter the noise that the delta-sigma modulator produces, which peaks at an offset frequency of  $f_{\rm PD}/2$  from the carrier. The LMX2531 also has 16 levels of charge pump currents and a highly flexible fractional modulus. Increasing the charge pump current improves the phase noise about 3 dB per doubling of the charge pump current, although there are small diminishing returns as the charge pump current increases.

From a loop filter design and PLL phase noise perspective, one might think to always design with the highest possible phase detector frequency and charge pump current. However, if one considers the worst case fractional spurs that occur at an output frequency equal to 1 channel spacing away from a multiple of the f<sub>OSCin</sub>, then this gives reason to reconsider. If the phase detector frequency or charge pump currents are too high, then these spurs could be degraded, and the loop filter may not be able to filter these spurs as well as theoretically predicted. For optimal spur performance, a phase detector frequency around 2.5 MHz and a charge pump current of 1X are recommended.

#### 1.4 N DIVIDER AND FRACTIONAL CIRCUITRY

The N divider in the LMX2531 includes fractional compensation and can achieve any fractional denominator between 1 and 4,194,303. The integer portion,  $N_{\text{Integer}}$ , is the whole part of the N divider value and the fractional portion,  $N_{\text{Fractional}}$ , is the remaining fraction. So in general, the total N divider value, N, is determined by:

$$N = N_{Integer} + N_{Fractional}$$

For example, if the phase detector frequency ( $f_{PD}$ ) was 10 MHz and the VCO frequency ( $f_{VCO}$ ) was 1736.1 MHz, then N would be 173.61. This would imply that N $_{Integer}$  is 173 and N $_{Fractional}$  is 61/100. N $_{Integer}$  has some minimum value restrictions that are arise due to the architecture of this divider. The first restrictions arise because the N divider value is actually formed by a quadruple modulus 16/17/20/21 prescaler, which creates minimum divide values. N $_{Integer}$  is further restricted because the LMX2531 due to the fractional engine of the N divider.

The fractional word,  $N_{Fractional}$ , is a fraction formed with the NUM and DEN words. In the example used here with the fraction of 61/100, NUM = 61 and DEN = 100. The fractional denominator value, DEN, can be set from 2 to 4,194,303. The case of DEN=0 makes no sense, since this would cause an infinite N value; the case of 1 makes no sense either (but could be done), because integer mode should be used in these applications. All other values in this range, like 10, 32, 42, 734, or 4,000,000 are all valid. Once the fractional denominator, DEN, is determined, the fractional numerator, NUM, is intended to be varied from 0 to DEN-1.

In general, the fractional denominator, DEN, can be calculated by dividing the phase detector frequency by the greatest common divisor (GCD) of the channel spacing ( $f_{CH}$ ) and the phase detector frequency. If the channel spacing is not obvious, then it can be calculated as the greatest common divisor of all the desired VCO frequencies.

$$\begin{aligned} \text{FDEN} &= k \cdot f_{\text{PD}} \, / \, \text{GCD}(f_{\text{PD}} \; , \, f_{\text{CH}}) \\ &\quad k = 1, \, 2, \, 3 \; .. \end{aligned}$$

For example, consider the case of a 10 MHz phase detector frequency and a 200 kHz channel spacing at the VCO output. The greatest common divisor of 10 MHz and 200 kHz is just 200 kHz. If one takes 10 MHz divided by 200 kHz, the result is 50. So a fractional denominator of 50, or any multiple of 50 would work in this example. Now consider a case with a 10 MHz phase detector frequency and a 30 kHz channel spacing. The greatest common divisor of 10 MHz and 30 kHz is 10 kHz. The fractional denominator therefore must be a multiple 1000, since this is 10 MHz divided by 10 kHz. For a final example, consider an application with a fixed output frequency of 2110.8 MHz and a OSCin frequency of 19.68 MHz. If the phase detector frequency is chosen to be 19.68 MHz, then the channel spacing can be calculated as the greatest common multiple of 19.68 MHz and 2110.8 MHz, which is 240 kHz. The fractional denominator is therefore a multiple of 41, which is 19.68 MHz / 240 kHz. Refer to appliction note 1865 for more details on frequency planning.