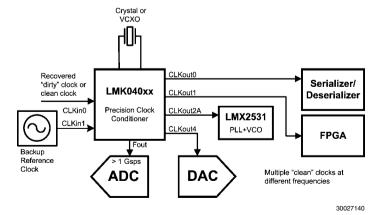

### LMK04000 Family of Precision Clock Conditioners Low-Noise Clock Jitter Cleaner with Cascaded PLLs

### 1.0 General Description

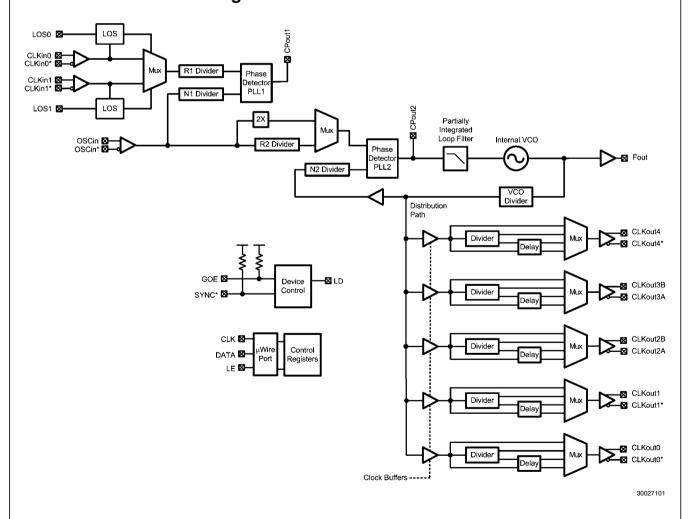

The LMK04000 family of precision clock conditioners provides low-noise jitter cleaning, clock multiplication and distribution without the need for high-performance voltage controlled crystal oscillators (VCXO) module. Using a cascaded PLLatinum™ architecture combined with an external crystal and varactor diode, the LMK04000 family provides sub-200 femtosecond (fs) root mean square (RMS) jitter performance. The cascaded architecture consists of two high-performance phase-locked loops (PLL), a low-noise crystal oscillator circuit, and a high-performance voltage controlled oscillator (VCO). The first PLL (PLL1) provides a low-noise jitter cleaner function while the second PLL (PLL2) performs the clock generation. PLL1 can be configured to either work with an external VCXO module or use the integrated crystal oscillator with an external crystal and a varactor diode. When used with a very narrow loop bandwidth, PLL1 uses the superior close-in phase noise (offsets below 50 kHz) of the VCXO module or the crystal to clean the input clock. The output of PLL1 is used as the clean input reference to PLL2 where it locks the integrated VCO. The loop bandwidth of PLL2 can be optimized to clean the far-out phase noise (offsets above 50 kHz) where the integrated VCO outperforms the VCXO module or crystal used in PLL1.

The LMK04000 family features dual redundant inputs, five differential outputs, and an optional default-clock upon power up. The input block is equipped with loss of signal detection and automatic or manual selection of the reference clock. Each clock output pair consists of a programmable divider, a phase synchronization circuit, a programmable delay, and an LVDS, LVPECL, or LVCMOS output buffer. The default start-up clock is available on CLKout2 and it can be used to provide an initial clock for the field-programmable gate array (FPGA) or microcontroller that programs the jitter cleaner during the system power up sequence.

#### 2.0 Features

- Cascaded PLLatinum PLL Architecture

- \_\_ PI I 1

- Phase detector rate of up to 40 MHz

- Integrated Low-Noise Crystal Oscillator Circuit

- Dual redundant input reference clock with LOS

- PLL2

- Normalized [1 Hz] PLL noise floor of -224 dBc/Hz

- Phase detector rate up to 100 MHz

- Input frequency-doubler

- Integrated Low-Noise VCO

- Ultra-Low RMS Jitter Performance

- 150 fs RMS jitter (12 kHz 20 MHz)

- 200 fs RMS jitter (100 Hz 20 MHz)

- LVPECL/2VPECL, LVDS, and LVCMOS outputs

- Support clock rates up to 1080 MHz

- Default Clock Output (CLKout2) at power up

- Five dedicated channel divider and delay blocks

- Pin compatible family of clocking devices

- Industrial Temperature Range: -40 to 85 °C

- 3.15 V to 3.45 V operation

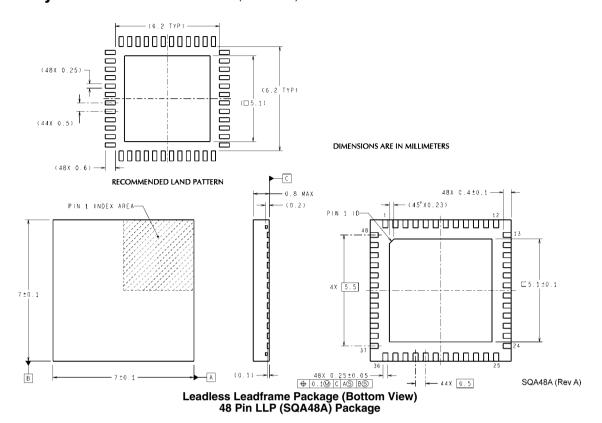

- Package: 48 pin LLP (7.0 x 7.0 x 0.8 mm)

### 3.0 Target Applications

- Data Converter Clocking

- Wireless Infrastructure

- Networking, SONET/SDH, DSLAM

- Medical

- Military / Aerospace

- Test and Measurement

PLLatinum™ is a trademark of National Semiconductor Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

#### **Device Configuration Information** (Note 1)

| NSID         | PROCESS | 2VPECL / LVPECL<br>OUTPUTS | LVDS OUTPUTS | LVCMOS<br>OUTPUTS | vco              |

|--------------|---------|----------------------------|--------------|-------------------|------------------|

| LMK04000BISQ | BiCMOS  | 3                          |              | 4                 | 1185 to 1296 MHz |

| LMK04001BISQ | BiCMOS  | 3                          |              | 4                 | 1430 to 1570 MHz |

| LMK04011BISQ | BiCMOS  | 5                          |              |                   | 1430 to 1570 MHz |

| LMK04031BISQ | BiCMOS  | 2                          | 2            | 2                 | 1430 to 1570 MHz |

| LMK04033BISQ | BiCMOS  | 2                          | 2            | 2                 | 1840 to 2160 MHz |

| NSID         | CLKout0         | CLKout1         | CLKout1 CLKout2 CLKout3 |                 | CLKout4         |

|--------------|-----------------|-----------------|-------------------------|-----------------|-----------------|

| LMK04000BISQ | 2VPECL / LVPECL | LVCMOS x 2      | LVCMOS x 2              | 2VPECL / LVPECL | 2VPECL / LVPECL |

| LMK04001BISQ | 2VPECL / LVPECL | LVCMOS x 2      | LVCMOS x 2              | 2VPECL / LVPECL | 2VPECL / LVPECL |

| LMK04011BISQ | 2VPECL / LVPECL | 2VPECL / LVPECL | 2VPECL / LVPECL         | 2VPECL / LVPECL | 2VPECL / LVPECL |

| LMK04031BISQ | LVDS            | 2VPECL / LVPECL | LVCMOS x 2              | 2VPECL / LVPECL | LVDS            |

| LMK04033BISQ | LVDS            | 2VPECL / LVPECL | LVCMOS x 2              | 2VPECL / LVPECL | LVDS            |

Note 1: LMK04000B and LMK04001B devices are not yet fully characterized and released.

### 4.0 Functional Block Diagram

### **Table of Contents**

| 1.0 General Description                                                                           |    |

|---------------------------------------------------------------------------------------------------|----|

| 2.0 Features                                                                                      |    |

| 3.0 Target Applications                                                                           |    |

| 4.0 Functional Block Diagram                                                                      |    |

| 5.0 Connection Diagram 6.0 Pin Descriptions                                                       |    |

| 7.0 Absolute Maximum Ratings                                                                      |    |

| 8.0 Package Thermal Resistance                                                                    |    |

| 9.0 Recommended Operating Conditions                                                              | 0  |

| 10.0 Electrical Characteristics                                                                   | 0  |

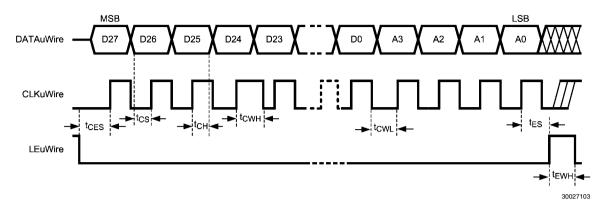

| 11.0 Serial Data Timing Diagram                                                                   |    |

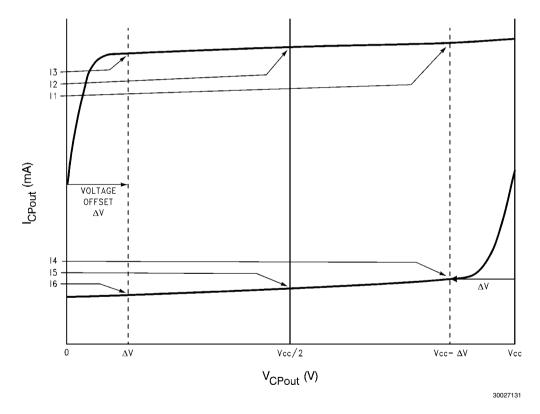

| 12.0 Charge Pump Current Specification Definitions                                                | 19 |

| 12.1 CHARGE PUMP OUTPUT CURRENT MAGNITUDE VARIATION VS. CHARGE PUMP OUTPUT                        | 10 |

| VOLTAGE                                                                                           | 20 |

| VOLTAGE12.2 CHARGE PUMP SINK CURRENT VS. CHARGE PUMP OUTPUT SOURCE CURRENT                        |    |

| MISMATCH                                                                                          | 20 |

| 12.3 CHARGE PUMP OUTPUT CURRENT MAGNITUDE VARIATION VS. TEMPERATURE                               | 20 |

| 13.0 Typical Performance Characteristics                                                          | 21 |

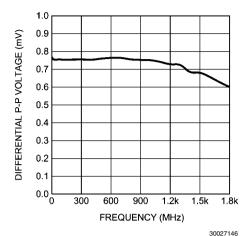

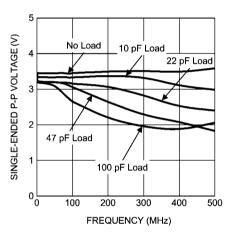

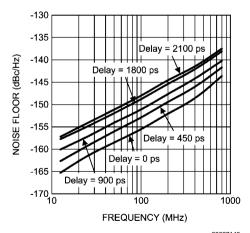

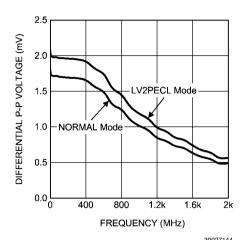

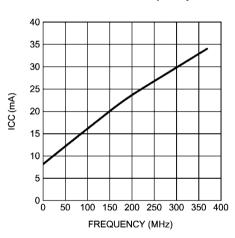

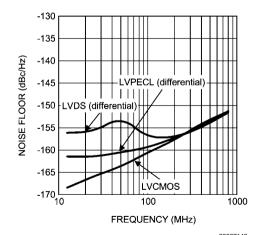

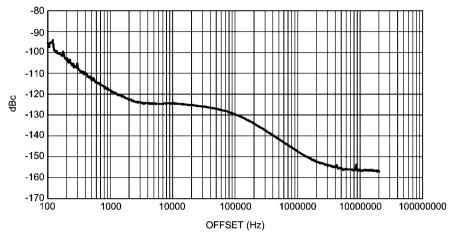

| 13.1 CLOCK OUTPUT AC CHARACTERISTICS                                                              | 21 |

| 14.0 Features                                                                                     |    |

| 14.1 SYSTEM ARCHITECTURE                                                                          | 23 |

| 14.2 REDUNDANT REFERENCE INPUTS (CLKin0/CLKin0*, CLKin1/CLKin1*)                                  | 23 |

| 14.3 PLL1 CLKinX (X=0,1) LOSS OF SIGNAL (LOS)                                                     | 23 |

| 14.4 INTEGRATED LOOP FILTER POLES                                                                 | 23 |

| 14.5 CLOCK DISTRIBUTION                                                                           | 23 |

| 14.6 CLKout DIVIDE (CLKoutX_DIV, X = 0 to 4)                                                      | 23 |

| 14.7 CLKout DELAY (CLKoutX_DLY, X = 0 to 4)                                                       | 23 |

| 14.8 GLOBAL CLOCK OUTPUT SYNCHRONIZATION (SYNC*)                                                  | 23 |

| 14.9 GLOBAL OUTPUT ENABLE AND LOCK DETECT                                                         |    |

| 15.0 Functional Description                                                                       | 24 |

| 15.1 ARCHITECTURAL OVERVIEW                                                                       |    |

| 15.2 PHASE DETECTOR 1 (PD1)                                                                       |    |

| 15.3 PHASE DETECTOr 2 (PD2)                                                                       | 24 |

| 15.4 PLL2 FREQUENCY DOUBLER                                                                       | 24 |

|                                                                                                   |    |

| 15.6 INPUTS / OUTPUTS                                                                             | 24 |

| 15.6.1 PLL1 Reference Inputs (CLKin0 / CLKin0*, CLKin1 / CLKin1*) 15.6.2 PLL2 OSCin / OSCin* Port | 24 |

| 15.6.3 CPout1 / CPout2                                                                            | 24 |

| 15.6.4 Fout                                                                                       |    |

| 15.6.5 Digital Lock Detect 1 Bypass                                                               | 25 |

| 15.6.6 Bias                                                                                       |    |

| 16.0 General Programming Information                                                              |    |

| 16.1 RECOMMENDED PROGRAMMING SEQUENCE                                                             | 25 |

| 16.2 DEFAULT DEVICE REGISTER SETTINGS AFTER POWER ON/RESET                                        | 28 |

| 16.3 REGISTER R0 TO R4                                                                            |    |

| 16.3.1 CLKoutX_DIV: Clock Channel Divide Registers                                                | 29 |

| 16.3.2 EN_CLKoutX: Clock Channel Output Enable                                                    |    |

| 16.3.3 CLKoutX_DLY: Clock Channel Phase Delay Adjustment                                          |    |

| 16.3.4 CLKoutX/CLKoutX* LVCMOS Mode Control                                                       | 29 |

| 16.3.5 CLKoutX/CLKoutX* LVPECL Mode Control                                                       | 30 |

| 16.3.6 CLKoutX_MUX: Clock Output Mux                                                              |    |

| 16.4 REGISTERS 5, 6                                                                               | 30 |

| 16.5 REGISTER 7                                                                                   |    |

| 16.5.1 RESET bit                                                                                  |    |

| 16.6 REGISTERS 8, 9                                                                               |    |

| 16.7 REGISTER 10                                                                                  |    |

| 16.7.1 RC_DLD1_Start: PLL1 Digital Lock Detect Run Control bit                                    |    |

| 16.8 REGISTER 11                                                                                  | 30 |

| 16.8.1 CLKinX_BUFTYPE: PLL1 CLKinX/CLKinX* Buffer Mode Control                                    | 30 |

| 16.8.2 CLKin_SEL: PLL1 Reference Clock Selection and Revertive Mode Control Bits                  |    |

| 16.8.3 CLKinX_LOS                                                                                 | 31 |

|                                                                                                   |    |

| 16.8.5 LOS Output Type Control                                                                    | 31 |

| 16.9 REGISTER 12                                                                       |    |

|----------------------------------------------------------------------------------------|----|

| 16.9.1 PLL1_N: PLL1_N Counter                                                          |    |

| 16.9.2 PLL1_R: PLL1_R Counter                                                          | 32 |

| 16.9.3 PLL1 Charge Pump Current Gain (PLL1_CP_GAIN) and Polarity Control (PLL1_CP_POL) |    |

| 16.10 REGISTER 13                                                                      | 32 |

| 16.10.1 EN_PLL2_XTAL: Crystal Oscillator Option Enable                                 | 32 |

| 16.10.2 EN_Fout: Fout Power Down Bit                                                   |    |

| 16.10.3 CLK Global Enable: Clock Global enable bit                                     |    |

| 16.10.4 POWERDOWN Bit Device Power Down                                                | 32 |

| 16.10.5 EN_PLL2 REF2X: PLL2 Frequency Doubler control bit                              | 32 |

| 16.10.6 PLL2 Internal Loop Filter Component Values                                     | 32 |

| 16.10.6 PLL2 Internal Loop Filter Component Values                                     | 33 |

| 16.11 REGISTER 14                                                                      | 33 |

| 16.11.1 OSCin_FREQ: PLL2 Oscillator Input Frequency Register                           | 33 |

| 16.11.2 PLL2 R: PLL2 R Counter                                                         | 33 |

| 16.11.3 PLL_MUX: LD Pin Selectable Output                                              | 33 |

| 16.12 REGISTER 15                                                                      |    |

| 16.12.1 PLL2_N: PLL2_N Counter                                                         | 34 |

| 16.12.2 PLL2_CP_GAIN: PLL2 Charge Pump Current and Output Control                      | 34 |

| 16.12.3 VCO_DIV: PLL2 VCO Divide Register                                              | 34 |

| 17.0 Application Information                                                           | 35 |

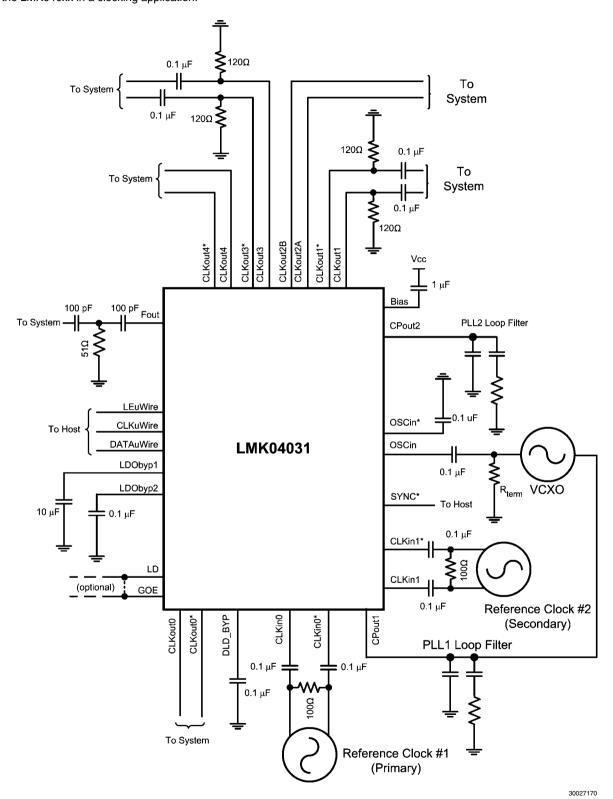

| 17.1 SYSTEM LEVEL DIAGRAM                                                              | 35 |

| 17.2 LDO BYPASS AND BIAS PIN                                                           |    |

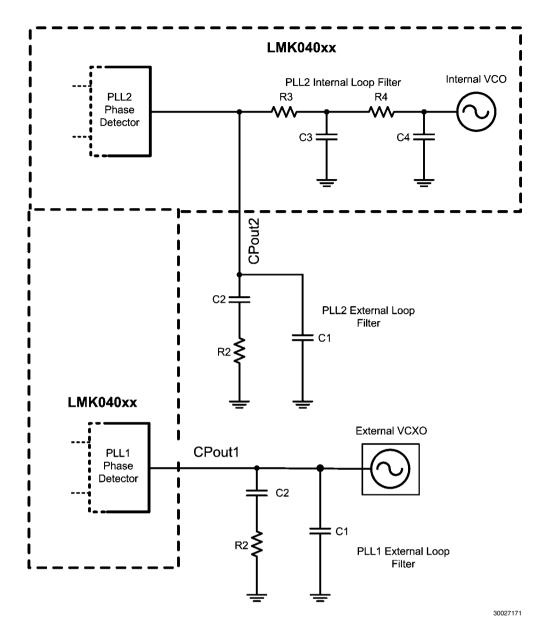

| 17.3 LOOP FILTER                                                                       | 36 |

| 17.4 CURRENT CONSUMPTION / POWER DISSIPATION CALCULATIONS                              | 39 |

| 17.5 POWER SUPPLY CONDITIONING                                                         | 39 |

| 17.6 THERMAL MANAGEMENT                                                                | 39 |

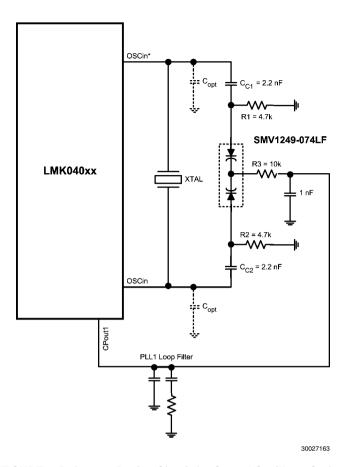

| 17.7 OPTIONAL CRYSTAL OSCILLATOR IMPLEMENTATION (OSCin/OSCin*)                         | 40 |

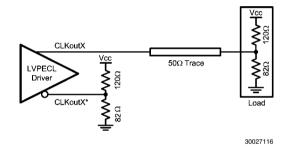

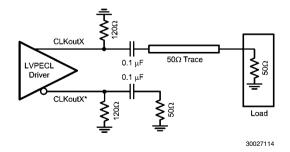

| 17.8 TERMINATION AND USE OF CLOCK OUTPUT (DRIVERS)                                     | 43 |

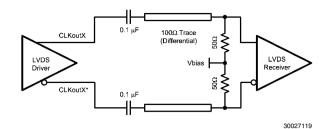

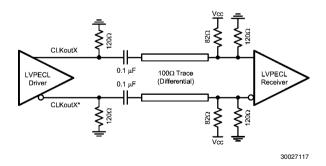

| 17.8.1 Termination for DC Coupled Differential Operation                               |    |

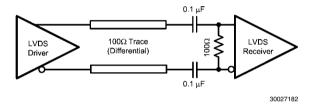

| 17.8.2 Termination for AC Coupled Differential Operation                               | 43 |

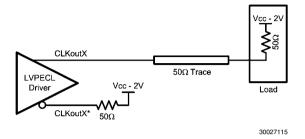

| 17.8.3 Termination for Single-Ended Operation                                          | 44 |

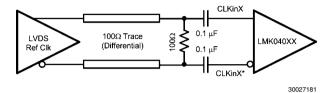

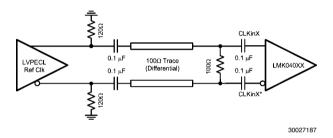

| 17.9 DRIVING CLKin AND ÖSCin INPUTS                                                    | 45 |

| 17.9.1 Driving CLKin Pins with a Differential Source                                   |    |

| 17.9.2 Driving CLKin Pins with a Single-Ended Source                                   |    |

| 17.10 ADDITIONAL OUTPUTS WITH AN LMK04000 FAMILY DEVICE                                | 45 |

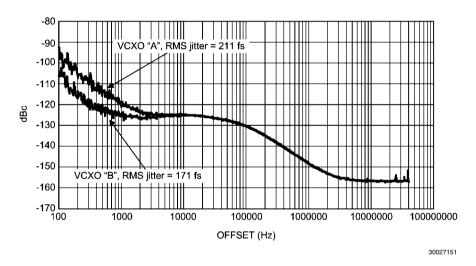

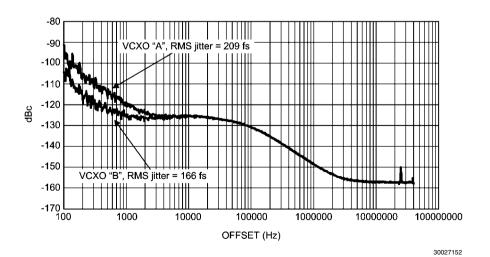

| 17.11 OUTPUT CLOCK PHASE NOISE PERFORMANCE VS. VCXO PHASE NOISE                        |    |

| 18.0 Physical Dimensions                                                               |    |

| 19.0 Ordering Information                                                              | 49 |

|                                                                                        |    |

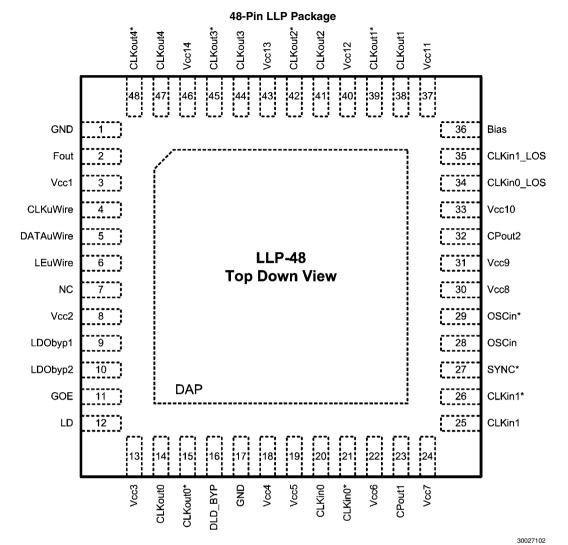

### 5.0 Connection Diagram

# 6.0 Pin Descriptions

| Pin Number | Name(s)            | I/O | Туре        | Description                                                                       |

|------------|--------------------|-----|-------------|-----------------------------------------------------------------------------------|

| 1          | GND                |     | GND         | Ground (For Fout Buffer)                                                          |

| 2          | Fout               | 0   | ANLG        | VCO Frequency Output Port                                                         |

| 3          | V <sub>CC</sub> 1  |     | PWR         | Power Supply                                                                      |

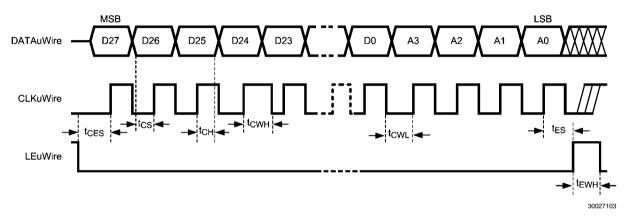

| 4          | CLKuWire           | I   | CMOS        | Microwire Clock Input                                                             |

| 5          | DATAuWire          | I   | CMOS        | Microwire Data Input                                                              |

| 6          | LEuWire            | I   | CMOS        | Microwire Latch Enable Input                                                      |

| 7          | NC                 |     |             | No Connection                                                                     |

| 8          | V <sub>CC</sub> 2  |     | PWR         | Power Supply                                                                      |

| 9          | LDObyp1            |     | ANLG        | LDO Out, bypassed to ground with 10 $\mu\text{F}$ and 0.1 $\mu\text{F}$ capacitor |

| 10         | LDObyp2            |     | ANLG        | LDO Bypass, bypassed to ground with a 0.1 μF capacitor                            |

| 11         | GOE                | 1   | CMOS        | Global Output Enable                                                              |

| 12         | LD                 | 0   | CMOS        | Lock Detect and PLL multiplexer Output                                            |

| 13         | V <sub>CC</sub> 3  |     | PWR         | Power Supply CLKout0                                                              |

| 14         | CLKout0            | 0   | LVDS/LVPECL | Clock Channel 0 Output                                                            |

| 15         | CLKout0*           | 0   | LVDS/LVPECL | Clock Channel 0* Output                                                           |

| 16         | DLD_BYP            |     | ANLG        | DLD Bypass, bypassed to ground with a 0.1 µF capacitor                            |

| 17         | GND                |     | GND         | Ground (Digital)                                                                  |

| 18         | V <sub>CC</sub> 4  |     | PWR         | Power Supply (Digital)                                                            |

| 19         | V <sub>CC</sub> 5  |     | PWR         | Power Supply (CLKin0)                                                             |

| 20         | CLKin0             | I   | ANLG        | Reference Clock Input Port for PLL1 - AC or DC Coupled (Note 2)                   |

| 21         | CLKin0*            | I   | ANLG        | Reference Clock Input Port for PLL1 (complimentary) - AC or DC Coupled (Note 2)   |

| 22         | V <sub>CC</sub> 6  |     | PWR         | Power Supply (PDCP1)                                                              |

| 23         | CPout1             | 0   | ANLG        | Charge Pump1 Output                                                               |

| 24         | V <sub>CC</sub> 7  |     | PWR         | Power Supply                                                                      |

| 25         | CLKin1             | I   | ANLG        | Reference Clock Input Port for PLL1 - AC or DC Coupled (Note 2)                   |

| 26         | CLKin1*            | I   | ANLG        | Reference Clock Input Port for PLL1 (complimentary) - AC or DC Coupled (Note 2)   |

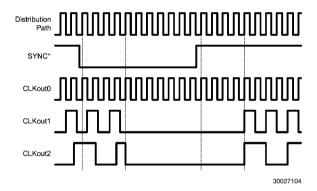

| 27         | SYNC*              | I   | CMOS        | Global Clock Output Synchronization                                               |

| 28         | OSCin              | I   | ANLG        | Reference oscillator Input for PLL2 - AC or DC Coupled (Note 2)                   |

| 29         | OSCin*             | I   | ANLG        | Reference oscillator Input for PLL2 - AC or DC Coupled (Note 2)                   |

| 30         | V <sub>CC</sub> 8  |     | PWR         | Power Supply (OSCin)                                                              |

| 31         | V <sub>CC</sub> 9  |     | PWR         | Power Supply (PDCP2)                                                              |

| 32         | CPout2             | 0   | ANLG        | Charge Pump2 Output                                                               |

| 33         | V <sub>CC</sub> 10 |     | PWR         | Power Supply (VCO Divider, PLL2 N-Counter)                                        |

| 34         | CLKin0_LOS         | 0   | LVCMOS      | Status of CLKin0 reference clock input                                            |

| 35         | CLKin1_LOS         | 0   | LVCMOS      | Status of CLKin1 reference clock input                                            |

| 36         | Bias               | ı   | ANLG        | Bias Bypass. AC coupled with 1 µF capacitor to Vcc1                               |

| 37         | V <sub>CC</sub> 11 |     | PWR         | Power Supply (CLKout1)                                                            |

| 38         | CLKout1            | 0   | LVPECL      | Clock Channel 1 Output                                                            |

| 39         | CLKout1*           | 0   | LVPECL      | Clock Channel 1* Output                                                           |

| 40         | V <sub>CC</sub> 12 |     | PWR         | Power Supply (CLKout2)                                                            |

| Pin Number | Name(s)            | I/O | Туре          | Description                    |

|------------|--------------------|-----|---------------|--------------------------------|

| 41         | CLKout2            | 0   | LVPECL/LVCMOS | Clock Channel 2 Output         |

| 42         | CLKout2*           | 0   | LVPECL/LVCMOS | Clock Channel 2* Output        |

| 43         | V <sub>CC</sub> 13 |     | PWR           | Power Supply (CLKout3)         |

| 44         | CLKout3            | 0   | LVPECL/LVCMOS | Clock Channel 3 Output         |

| 45         | CLKout3*           | 0   | LVPECL/LVCMOS | Clock Channel 3* Output        |

| 46         | V <sub>CC</sub> 14 |     | PWR           | Power Supply (CLKout4)         |

| 47         | CLKout4            | 0   | LVDS/LVPECL   | Clock Channel 4 Output         |

| 48         | CLKout4*           | 0   | LVDS/LVPECL   | Clock Channel 4* Output        |

| DAP        | DAP                |     |               | DIE ATTACH PAD, connect to GND |

Note 2: The reference clock inputs may be either AC or DC coupled.

### 7.0 Absolute Maximum Ratings (Notes 3, 4, 5)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Parameter                                            | Symbol           | Ratings                         | Units |

|------------------------------------------------------|------------------|---------------------------------|-------|

| Supply Voltage (Note 6)                              | V <sub>cc</sub>  | -0.3 to 3.6                     | V     |

| Input Voltage                                        | V <sub>IN</sub>  | -0.3 to (V <sub>CC</sub> + 0.3) | V     |

| Storage Temperature Range                            | T <sub>STG</sub> | -65 to 150                      | °C    |

| Lead Temperature (solder 4 sec)                      | $T_L$            | +260                            | °C    |

| Differential Input Current (CLKinX/X*, OSCin/OSCin*) | I <sub>IN</sub>  | ± 5                             | mA    |

**Note 3:** "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only to the test conditions listed.

**Note 4:** This device is a high performance RF integrated circuit with an ESD rating up to 8 KV Human Body Model, up to 300 V Machine Model and up to 1,250 V Charged Device Model and is ESD sensitive. Handling and assembly of this device should only be done at ESD-free workstations.

**Note 5:** Stresses in excess of the absolute maximum ratings can cause permanent or latent damage to the device. These are absolute stress ratings only. Functional operation of the device is only implied at these or any other conditions in excess of those given in the operation sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

Note 6: Never to exceed 3.6 V.

### 8.0 Package Thermal Resistance

| Package              | $\theta_{JA}$ | θ <sub>J-PAD (Thermal Pad)</sub> |

|----------------------|---------------|----------------------------------|

| 48-Lead LLP (Note 7) | 27.4° C/W     | 5.8° C/W                         |

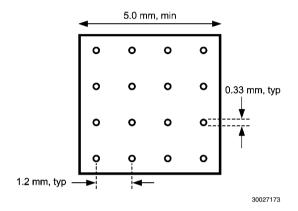

Note 7: Specification assumes 16 thermal vias connect the die attach pad to the embedded copper plane on the 4-layer JEDEC board. These vias play a key role in improving the thermal performance of the LLP. It is recommended that the maximum number of vias be used in the board layout.

### 9.0 Recommended Operating Conditions

| Parameter              | Symbol          | Condition               | Min  | Typical | Max  | Unit |

|------------------------|-----------------|-------------------------|------|---------|------|------|

| Ambient<br>Temperature | T <sub>A</sub>  | V <sub>CC</sub> = 3.3 V | -40  | 25      | 85   | °C   |

| Supply Voltage         | V <sub>CC</sub> |                         | 3.15 | 3.3     | 3.45 | V    |

### **10.0 Electrical Characteristics**

$(3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40 ^{\circ}\text{C} \le \text{T}_{A} \le 85 ^{\circ}\text{C}$ . Typical values represent most likely parametric norms at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 ^{\circ}\text{C}$ , at the Recommended Operating Conditions at the time of product characterization and are not guaranteed.)

| Symbol                                                | Parameter                                                       | Conditions                                                               | Min   | Тур | Max             | Units |

|-------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------|-------|-----|-----------------|-------|

|                                                       | Curr                                                            | ent Consumption                                                          |       |     | -               | _     |

| I <sub>CC_PD</sub>                                    | Power Down Supply Current                                       |                                                                          |       |     | 1               | mA    |

| I <sub>CC CLKS</sub>                                  | Supply Current with all clocks                                  | LMK04011 (Note 9)                                                        |       | 378 | 435             | mA    |

| _                                                     | enabled, all delay bypassed,                                    | LMK04031, LMK04033                                                       |       | 335 | 385             |       |

|                                                       | Fout disabled. (Note 8)                                         | (Note 9)                                                                 |       |     |                 |       |

|                                                       | CLKin0/0* and CLK                                               | n1/1* Input Clock Specification                                          | าร    |     |                 |       |

| f <sub>CLKin</sub>                                    | Clock Input Frequency                                           | Manual Select mode                                                       | 0.001 |     | 400             | MHz   |

|                                                       | (Note 10)                                                       | Auto-Switching mode                                                      | 1     |     | 400             |       |

| SLEW <sub>CLKin</sub>                                 | Slew Rate on CLKin<br>(Note 11)                                 | 20% to 80%                                                               | 0.15  | 0.5 |                 | V/ns  |

| V <sub>CLKin</sub> (Bipolar input buffer mode)        | Input Voltage Swing, single-ended input                         | AC coupled to CLKinX; CLKinX* AC coupled to Ground (CLKinX_TYPE=0)       | 0.25  |     | 2.0             | Vpp   |

|                                                       | Input Voltage Swing,<br>differential input                      | CLKinX and CLKinX* are both driven, AC coupled. (CLKinX_TYPE=0)          | 0.5   |     | 3.1             | Vpp   |

| V <sub>CLKin-offset</sub> (Bipolar input buffer mode) | DC offset voltage between<br>CLKinX/CLKinX*<br>ICLKinX-CLKinX*  | Each pin AC coupled<br>(CLKinX_TYPE=0)                                   |       | 44  |                 | mV    |

| V <sub>CLKin</sub> (MOS input buffer mode)            | Input Voltage Swing, single-<br>ended input                     | AC coupled to CLKinX; CLKinX* AC coupled to Ground (CLKinX_TYPE=1)       | 0.25  |     | 2.0             | Vpp   |

|                                                       | Input Voltage Swing,<br>differential input                      | CLKinX and CLKinX* are both driven, AC coupled. (CLKinX_TYPE=1)          | 0.5   |     | 3.1             | Vpp   |

| $V_{CLKin}V_{IH}$ (MOS input buffer mode)             | Maximum input voltage                                           | DC coupled to CLKinX;<br>CLKinX* AC coupled to Ground<br>(CLKinX_TYPE=1) | 2.0   |     | V <sub>CC</sub> | V     |

| $V_{CLKin}V_{IL}$ (MOS input buffer mode)             |                                                                 | DC coupled to CLKinX;<br>CLKinX* AC coupled to Ground<br>(CLKinX_TYPE=1) | 0.0   |     | 0.4             | V     |

| V <sub>CLKin-offset</sub> (MOS input<br>buffer mode)  | DC offset voltage between<br>CLKinX/CLKinX*<br>ICLKinX-CLKinX*I | Each pin AC coupled<br>(CLKinX_TYPE=1)                                   |       | 294 |                 | mV    |

| Symbol                            | Parameter                                                                | Conditions                                                                                                       | Min  | Тур  | Max | Units |

|-----------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

|                                   | PLL                                                                      | 1 Specifications                                                                                                 |      |      |     |       |

| f <sub>PD</sub>                   | PLL1 Phase Detector<br>Frequency                                         |                                                                                                                  |      |      | 40  | MHz   |

| I <sub>CPout1</sub> SOURCE        | PLL1 Charge Pump Source<br>Current (Note 12)                             | $V_{CPout1} = V_{CC}/2$ ,<br>PLL1_CP_GAIN = 100b                                                                 |      | 25   |     | μA    |

|                                   |                                                                          | $V_{CPout1} = V_{CC}/2$ ,<br>PLL1_CP_GAIN = 101b                                                                 |      | 50   |     |       |

|                                   |                                                                          | $V_{CPout1} = V_{CC}/2$ ,<br>PLL1_CP_GAIN = 110b                                                                 |      | 100  |     |       |

|                                   |                                                                          | $V_{CPout1} = V_{CC}/2$ ,<br>PLL1_CP_GAIN = 111b                                                                 |      | 400  |     |       |

|                                   |                                                                          | PLL1_CP_GAIN = 000b                                                                                              |      | NA   |     | ]     |

|                                   |                                                                          | PLL1_CP_GAIN = 001b                                                                                              |      | NA   |     | ]     |

|                                   |                                                                          | V <sub>CPout1</sub> =V <sub>CC</sub> /2,<br>PLL1_CP_GAIN = 010b                                                  |      | 20   |     |       |

|                                   |                                                                          | V <sub>CPout1</sub> =V <sub>CC</sub> /2,<br>PLL1_CP_GAIN = 011b                                                  |      | 80   |     |       |

| I <sub>CPout1</sub> SINK          | PLL1 Charge Pump Sink<br>Current (Note 12)                               | $V_{CPout1}=V_{CC}/2$ ,<br>PLL1_CP_GAIN = 100b                                                                   |      | -25  |     | μA    |

|                                   |                                                                          | $V_{CPout1}=V_{CC}/2$ ,<br>PLL1_CP_GAIN = 101b                                                                   |      | -50  |     |       |

|                                   |                                                                          | $V_{CPout1}=V_{CC}/2$ ,<br>PLL1_CP_GAIN = 110b                                                                   |      | -100 |     |       |

|                                   |                                                                          | $V_{CPout1}=V_{CC}/2$ ,<br>PLL1_CP_GAIN = 111b                                                                   |      | -400 |     |       |

|                                   |                                                                          | PLL1_CP_GAIN = 000b                                                                                              |      | NA   |     |       |

|                                   |                                                                          | PLL1_CP_GAIN = 001b                                                                                              |      | NA   |     |       |

|                                   |                                                                          | $V_{CPout1}=V_{CC}/2$ ,<br>PLL1_CP_GAIN = 010b                                                                   |      | -20  |     |       |

|                                   |                                                                          | $V_{CPout1}=V_{CC}/2$ ,<br>PLL1_CP_GAIN = 011b                                                                   |      | -80  |     |       |

| I <sub>CPout1</sub> %MIS          | Charge Pump Sink / Source<br>Mismatch                                    | $V_{CPout1} = V_{CC}/2$ , $T = 25  ^{\circ}C$                                                                    |      | 3    | 10  | %     |

| $I_{CPout1}V_{TUNE}$              | Magnitude of Charge Pump<br>Current vs. Charge Pump<br>Voltage Variation | $0.5 \text{ V} < \text{V}_{\text{CPout1}} < \text{V}_{\text{CC}} - 0.5 \text{ V}$ $T_{\text{A}} = 25 \text{ °C}$ |      | 4    |     | %     |

| I <sub>CPout1</sub> %TEMP         | Charge Pump Current vs. Temperature Variation                            |                                                                                                                  |      | 4    |     | %     |

| PLL1 I <sub>CPout1</sub> TRI      | Charge Pump TRI-<br>STATE®Leakage Current                                | 0.5 V < V <sub>CPout</sub> < V <sub>CC</sub> - 0.5 V                                                             |      |      | 5   | nA    |

|                                   | PLL2 Reference                                                           | Input (OSCin) Specifications                                                                                     |      |      |     |       |

| f <sub>OSCin</sub>                | PLL2 Reference Input<br>(Note 13)                                        | EN_PLL2_REF 2X = 0<br>(Note 14)                                                                                  |      |      | 250 | MHz   |

|                                   |                                                                          | EN_PLL2_REF 2X = 1                                                                                               |      |      | 50  |       |

| SLEW <sub>OSCin</sub>             | PLL2 Reference Clock minimum slew rate on OSCin                          | 20% to 80%                                                                                                       | 0.15 | 0.5  |     | V/ns  |

| V <sub>OSCin</sub> (Single-ended) | Input Voltage for OSCin or OSCin*                                        | AC coupled; Single-ended<br>(Unused pin AC coupled to<br>GND)                                                    | 0.2  |      | 2.0 | Vpp   |

| V <sub>OSCin</sub> (Differential) | Differential voltage swing                                               | AC coupled                                                                                                       | 0.4  |      | 3.1 | Vpp   |

| Symbol                                | Parameter                                                                | Conditions                                                                                                       | Min  | Тур          | Max  | Units  |

|---------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|--------------|------|--------|

|                                       | Crystal Oscill                                                           | lator Mode Specifications                                                                                        |      |              |      |        |

| XTAL                                  | Crystal Frequency Range                                                  |                                                                                                                  | 6    |              | 20   | MHz    |

| ESR                                   | Crystal Effective Series<br>Resistance                                   | 6 MHz < F <sub>XTAL</sub> < 20 MHz                                                                               |      |              | 100  | Ohms   |

| XTAL                                  | Crystal Power Dissipation                                                |                                                                                                                  |      | (Note<br>15) |      | μW     |

| Pin                                   | Input Capacitance of<br>LMK040xx OSCin port                              | -40 to +85 °C                                                                                                    |      | 6            |      | pF     |

|                                       | PLL2 Phase Detector                                                      | and Charge Pump Specification                                                                                    | ons  |              |      |        |

| PD                                    | Phase Detector Frequency                                                 |                                                                                                                  |      |              | 100  | MHz    |

| CPoutSOURCE                           | PLL2 Charge Pump Source<br>Current (Note 12)                             | V <sub>CPout2</sub> =V <sub>CC</sub> /2,<br>PLL2_CP_GAIN = 00b                                                   |      | 100          |      | μА     |

|                                       |                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2,<br>PLL2_CP_GAIN = 01b                                                   |      | 400          |      |        |

|                                       |                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2,<br>PLL2_CP_GAIN = 10b                                                   |      | 1600         |      |        |

| OINIZ                                 | DLLO Obarras Duras Cial                                                  | V <sub>CPout2</sub> =V <sub>CC</sub> /2,<br>PLL2_CP_GAIN = 11b                                                   |      | 3200         |      |        |

| I <sub>CPout</sub> SINK               | PLL2 Charge Pump Sink<br>Current (Note 12)                               | V <sub>CPout2</sub> =V <sub>CC</sub> /2,<br>PLL2_CP_GAIN = 00b                                                   |      | -100         |      | μA     |

|                                       |                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2,<br>PLL2_CP_GAIN = 01b                                                   |      | -400         |      |        |

|                                       |                                                                          | $V_{CPout2}=V_{CC}/2$ ,<br>PLL2_CP_GAIN = 10b                                                                    |      | -1600        |      |        |

|                                       |                                                                          | $V_{CPout2}=V_{CC}/2$ ,<br>PLL2_CP_GAIN = 11b                                                                    |      | -3200        |      |        |

| I <sub>CPout2</sub> %MIS              | Charge Pump Sink/Source<br>Mismatch                                      | $V_{CPout2} = V_{CC}/2$ , $T_A = 25$ °C                                                                          |      | 3            | 10   | %      |

| I <sub>CPout2</sub> V <sub>TUNE</sub> | Magnitude of Charge Pump<br>Current vs. Charge Pump<br>Voltage Variation | $0.5 \text{ V} < \text{V}_{\text{CPout2}} < \text{V}_{\text{CC}} - 0.5 \text{ V}$ $T_{\text{A}} = 25 \text{ °C}$ |      | 4            |      | %      |

| I <sub>CPout2</sub> %TEMP             | Charge Pump Current vs. Temperature Variation                            |                                                                                                                  |      | 4            |      | %      |

| <sub>CPout2</sub> TRI                 | Charge Pump Leakage                                                      | 0.5 V < V <sub>CPout2</sub> < V <sub>CC</sub> - 0.5 V                                                            |      |              | 10   | nA     |

| PN10kHz                               | PLL 1/f Noise at 10 kHz offset                                           | i i                                                                                                              |      | -117         |      | dBc/Hz |

|                                       | (Note 16). Normalized to 1 GHz Output Frequency                          | PLL2_CP_GAIN = 3200 μA                                                                                           |      | -122         |      |        |

| PN1Hz                                 | Normalized Phase Noise                                                   | PLL2_CP_GAIN = 400 μA                                                                                            |      | -219         |      | dBc/Hz |

|                                       | Contribution (Note 17)                                                   | PLL2_CP_GAIN = 3200 µA                                                                                           |      | -224         |      | ]      |

|                                       | Internal                                                                 | VCO Specifications                                                                                               |      |              |      | ,      |

| VCO                                   | VCO Tuning Range                                                         | LMK040x0                                                                                                         | 1185 |              | 1296 | MHz    |

|                                       |                                                                          | LMK040x1                                                                                                         | 1430 |              | 1570 |        |

|                                       |                                                                          | LMK040x3                                                                                                         | 1840 |              | 2160 |        |

| Pvco                                  | VCO Output power to a $50 \Omega$ load driven by Fout                    | LMK040x0, T <sub>A</sub> = 25 °C, single-<br>ended                                                               |      | 3            |      | dBm    |

|                                       |                                                                          | LMK040x1, $T_A = 25$ °C, single-<br>ended                                                                        |      | 3            |      |        |

|                                       |                                                                          | LMK040x3, T <sub>A</sub> = 25 °C, single-<br>ended 1840 MHz                                                      |      | 0            |      |        |

|                                       |                                                                          | LMK040x3, T <sub>A</sub> = 25 °C, single-<br>ended 2160 MHz                                                      |      | -5           |      |        |

| Symbol               | Parameter                            | Conditions                     | Min      | Тур      | Max | Units     |

|----------------------|--------------------------------------|--------------------------------|----------|----------|-----|-----------|

| K <sub>vco</sub>     | Fine Tuning Sensitivity              | LMK040x0                       |          | 7 to 9   |     | MHz/V     |

|                      |                                      | LMK040x1                       |          | 8 to 11  |     | 1         |

|                      |                                      | LMK040x3                       |          | 14 to 26 |     | 7         |

| ΔT <sub>CL</sub> I   | Allowable Temperature Drift          | After programming R15 for      |          |          | 125 | °C        |

| 01                   | for Continuous Lock                  | lock, no changes to output     |          |          |     |           |

|                      | (Note 18)                            | configuration are permitted to |          |          |     |           |

|                      |                                      | guarantee continuous lock      |          |          |     |           |

|                      | ·                                    | n Loop Phase Noise and Jitter  |          |          |     |           |

| _(f) <sub>Fout</sub> | LMK040x0                             | Offset = 1 kHz                 |          | -64      |     | dBc/Hz    |

|                      | f <sub>VCO</sub> = 1296 MHz          | Offset = 10 kHz                |          | -91      |     | _         |

|                      | SSB Phase Noise                      | Offset = 100 kHz               |          | -117     |     | _         |

|                      | PLL2 = Open Loop<br>Measured at Fout | Offset = 1 MHz                 |          | -138     |     |           |

|                      | Measured at Fout                     | Offset = 10 MHz                |          | -157     |     |           |

|                      |                                      | Offset = 20 MHz                |          | -161     |     | ]         |

|                      | LMK040x0                             | Offset = 1 kHz                 |          | -66      |     | dBc/Hz    |

|                      | f <sub>VCO</sub> = 1185 MHz          | Offset = 10 kHz                |          | -94      |     | 1         |

|                      | SSB Phase Noise                      | Offset = 100 kHz               |          | -119     |     | 1         |

|                      | PLL2 = Open Loop                     | Offset = 1 MHz                 |          | -139     |     | 1         |

|                      | Measured at Fout                     | Offset = 10 MHz                |          | -158     |     | 1         |

|                      |                                      | Offset = 20 MHz                |          | -163     |     | 1         |

|                      | LMK040x1                             | Offset = 1 kHz                 |          | -61      |     | dBc/Hz    |

|                      | f <sub>VCO</sub> = 1440 MHz          | Offset = 10 kHz                |          | -91      |     | 1         |

|                      | SSB Phase Noise                      | Offset = 100 kHz               |          | -117     |     | †         |

|                      | PLL2 = Open Loop                     | Offset = 1 MHz                 |          | -138     |     | 1         |

|                      | Measured at Fout                     | Offset = 10 MHz                |          | -158     |     | 1         |

|                      |                                      | Offset = 20 MHz                |          | -160     |     | 1         |

|                      | LMK040x1                             | Offset = 1 kHz                 |          | -58      |     | dBc/Hz    |

|                      | f <sub>VCO</sub> = 1560 MHz          | Offset = 10 kHz                |          | -89      |     | - 450/112 |

|                      | SSB Phase Noise                      | Offset = 100 kHz               |          | -115     |     | 1         |

|                      | PLL2 = Open Loop                     | Offset = 1 MHz                 |          | -137     |     | 1         |

|                      | Measured at Fout                     | Offset = 10 MHz                |          | -157     |     | +         |

|                      |                                      | Offset = 20 MHz                |          | -162     |     | -         |

|                      | LMK040x3                             | Offset = 1 kHz                 |          | -102     |     | dBc/Hz    |

|                      | f <sub>VCO</sub> = 1840 MHz          |                                |          |          |     | UBC/F12   |

|                      | SSB Phase Noise                      | Offset = 10 kHz                |          | -88      |     | 4         |

|                      | PLL2 = Open Loop                     | Offset = 100 kHz               |          | -113     |     | -         |

|                      | Measured at Fout                     | Offset = 1 MHz                 |          | -135     |     | -         |

|                      |                                      | Offset = 10 MHz                |          | -155     |     | 4         |

|                      |                                      | Offset = 20 MHz                |          | -158     |     |           |

|                      | LMK040x3                             | Offset = 1 kHz                 |          | -54      |     | dBc/Hz    |

|                      | f <sub>VCO</sub> = 2160 MHz          | Offset = 10 kHz                |          | -84      |     | 1         |

|                      | SSB Phase Noise                      | Offset = 100 kHz               |          | -110     |     | _         |

|                      | PLL2 = Open Loop<br>Measured at Fout | Offset = 1 MHz                 |          | -132     |     | _         |

|                      | inicusured at 1 out                  | Offset = 10 MHz                |          | -154     |     | ]         |

|                      |                                      | Offset = 20 MHz                | <u> </u> | -157     |     |           |

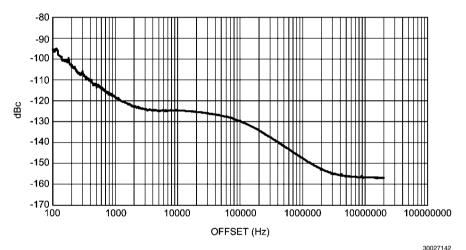

Internal VCO Closed Loop Phase Noise and Jitter Specifications using an Instrumentation Quality VCXO

| Symbol               | Parameter                                            | Conditions            | Min | Тур  | Max | Units  |

|----------------------|------------------------------------------------------|-----------------------|-----|------|-----|--------|

| L(f) <sub>Fout</sub> | LMK040x0 (Note 19)                                   | Offset = 1 kHz        |     | -111 |     | dBc/Hz |

|                      | f <sub>VCO</sub> = 1200 MHz                          | Offset = 10kHz        |     | -119 |     | ]      |

|                      | SSB Phase Noise                                      | Offset = 100 kHz      |     | -121 |     |        |

|                      | PLL2 = Closed Loop<br>Measured at Fout               | Offset = 1 MHz        |     | -133 |     |        |

|                      | Measured at Fout                                     | Offset = 10 MHz       |     | -157 |     | 1      |

|                      |                                                      | Offset = 20 MHz       |     | -162 |     | ]      |

|                      |                                                      | Offset = 40 MHz       |     | -165 |     | ]      |

|                      | LMK040x1 (Note 20)                                   | Offset = 1 kHz        |     | -110 |     | dBc/Hz |

|                      | f <sub>VCO</sub> = 1500 MHz                          | Offset = 10 kHz       |     | -117 |     | 1      |

|                      | SSB Phase Noise                                      | Offset = 100 kHz      |     | -120 |     | ]      |

|                      | PLL2 = Closed Loop                                   | Offset = 1 MHz        |     | -132 |     | ]      |

|                      | Measured at Fout                                     | Offset = 10 MHz       |     | -156 |     | 1      |

|                      |                                                      | Offset = 20 MHz       |     | -160 |     | ]      |

|                      |                                                      | Offset = 40 MHz       |     | -163 |     | 1      |

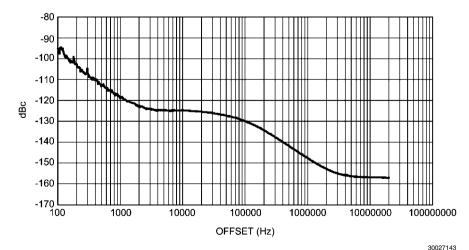

|                      | LMK040x3 (Note 21)                                   | Offset = 1 kHz        |     | -107 |     | dBc/Hz |

|                      | $f_{VCO} = 2000 \text{ MHz}$                         | Offset = 10 kHz       |     | -114 |     | 1      |

|                      | SSB Phase Noise                                      | Offset = 100 kHz      |     | -117 |     | ]      |

|                      | PLL2 = Closed Loop                                   | Offset = 1 MHz        |     | -126 |     | 1      |

|                      | Measured at Fout                                     | Offset = 10 MHz       |     | -152 |     | 1      |

|                      |                                                      | Offset = 20 MHz       |     | -156 |     | 1      |

|                      |                                                      | Offset = 40 MHz       |     | -160 |     | 1      |

| J <sub>Fout</sub>    | LMK040x0 (Note 19)                                   | BW = 12 kHz to 20 MHz |     | 105  |     | fs     |

|                      | f <sub>VCO</sub> = 1200 MHz<br>Integrated RMS Jitter | BW = 100 Hz to 20 MHz |     | 110  |     |        |

|                      | LMK040x1 (Note 20)                                   | BW = 12 kHz to 20 MHz |     | 100  |     | 1      |

|                      | f <sub>VCO</sub> = 1500 MHz<br>Integrated RMS Jitter | BW = 100 Hz to 20 MHz |     | 105  |     |        |

|                      | LMK040x3 (Note 21)                                   | BW = 12 kHz to 20 MHz |     | 105  |     | ]      |

|                      | f <sub>VCO</sub> = 2000 MHz<br>Integrated RMS Jitter | BW = 100 Hz to 20 MHz |     | 110  |     |        |

| Symbol                               | Parameter                                              | Conditions                     | Min            | Тур       | Max       | Units |

|--------------------------------------|--------------------------------------------------------|--------------------------------|----------------|-----------|-----------|-------|

| CLKout's Internal VC                 | O Closed Loop Phase Noise ar                           | nd Jitter Specifications using | an Instrur     | nentation | Quality V | cxo   |

| L(f) <sub>CLKout</sub>               | LMK040x0 (Note 22)                                     | Offset = 1 kHz                 |                | -125      |           | dBc/H |

|                                      | f <sub>CLKout</sub> = 250 MHz                          | Offset = 10 kHz                |                | -130      |           | _     |

|                                      | SSB Phase Noise                                        | Offset = 100 kHz               |                | -132      |           |       |

|                                      | Measured at Clock Outputs                              | Offset = 1 MHz                 |                | -148      |           |       |

|                                      | Value is average for all output                        | Offset = 10 MHz                |                | -157      |           | 1     |

|                                      | types                                                  | Offset = 1 kHz                 |                | -126      |           | -     |

|                                      | LMK040x1 (Note 23)<br>f <sub>CLKout</sub> = 250 MHz    | Offset = 10 kHz                |                |           |           | ┨     |

|                                      | SSB Phase Noise                                        |                                |                | -133      |           | -     |

|                                      | Measured at Clock Outputs                              | Offset = 100 kHz               |                | -136      |           | -     |

|                                      | Value is average for all output                        | Offset = 1 MHz                 |                | -147      |           | -     |

|                                      | types                                                  | Offset = 10 MHz                |                | -156      |           |       |

|                                      | LMK040x3 (Note 24)                                     | Offset = 1 kHz                 |                | -125      |           | 1     |

|                                      | f <sub>CLKout</sub> = 250 MHz                          | Offset = 10 kHz                |                | -132      |           | 1     |

|                                      | SSB Phase Noise                                        | Offset = 100 kHz               |                | -135      |           | 1     |

|                                      | Measured at Clock Outputs                              | Offset = 1 MHz                 |                | -145      |           | 1     |

|                                      | Value Is average for all output                        | Offset = 10 MHz                |                | -156      |           | 1     |

|                                      | types                                                  | Oliset = 10 MHz                |                | -130      |           |       |

| $J_{CLKout}$                         | LMK040x0 (Note 22)                                     | BW = 12 kHz to 20 MHz          |                | 130       |           | fs    |

| LVPECL/2VPECL/LVDS                   | f <sub>CLKout</sub> = 250 MHz                          | BW = 100 Hz to 20 MHz          |                | 135       |           |       |

|                                      | Integrated RMS Jitter                                  |                                |                |           |           | _     |

|                                      | LMK040x1 (Note 23)                                     | BW = 12 kHz to 20 MHz          |                | 115       |           | 1     |

|                                      | f <sub>CLKout</sub> = 250 MHz                          | BW = 100 Hz to 20 MHz          |                | 120       |           |       |

|                                      | Integrated RMS Jitter                                  |                                |                |           |           | 4     |

|                                      | LMK040x3 (Note 24)                                     | BW = 12 kHz to 20 MHz          |                | 125       |           | 1     |

|                                      | f <sub>CLKout</sub> = 250 MHz                          | BW = 100 Hz to 20 MHz          |                | 130       |           |       |

|                                      | Integrated RMS Jitter                                  | DW 40111 1 00 MH               |                | 440       |           |       |

| JCLKout                              | LMK040x0 (Note 22)                                     | BW = 12 kHz to 20 MHz          |                | 140       |           | fs    |

| LVCMOS                               | f <sub>CLKout</sub> = 250 MHz                          | BW = 100 Hz to 20 MHz          |                | 145       |           |       |

|                                      | Integrated RMS Jitter                                  | DW 40 kH = += 00 MH =          |                | 110       |           | -     |

|                                      | LMK040x1 (Note 23)                                     | BW = 12 kHz to 20 MHz          |                | 110       |           | -     |

|                                      | f <sub>CLKout</sub> = 250 MHz<br>Integrated RMS Jitter | BW = 100 Hz to 20 MHz          |                | 115       |           |       |

|                                      | LMK040x3 (Note 24)                                     | BW = 12 kHz to 20 MHz          |                | 120       |           | ┨     |

|                                      | f <sub>CLKout</sub> = 250 MHz                          |                                |                |           |           | -     |

|                                      | Integrated RMS Jitter                                  | BW = 100 Hz to 20 MHz          |                | 125       |           |       |

| CI Kout's                            | Internal VCO Closed Loop Jitte                         | er Specifications using a Com  | ı<br>mercial C | uality VC | XO.       | 1     |

|                                      | LMK040x1 (Notes 26, 28)                                | BW = 12 kHz to 20 MHz          |                | 130       | 200       | fs    |

| J <sub>CLKout</sub><br>LVPECL/2VPECL | f <sub>CLKout</sub> = 250 MHz                          | BW = 12 KHz to 20 MHz          |                | 190       | 200       | - '3  |

| LVI LODZVI LOL                       | Integrated RMS Jitter                                  | BVV = 100 HZ tO 20 IVIHZ       |                | 190       |           |       |

|                                      | LMK040x3 (Notes 27, 28)                                | BW = 12 kHz to 20 MHz          |                | 145       | 200       | 1     |

|                                      | f <sub>CLKout</sub> = 250 MHz                          | BW = 12 KHz to 20 MHz          |                | 200       | 200       | 1     |

|                                      | Integrated RMS Jitter                                  | BVV = 100 112 to 20 WII 12     |                | 200       |           |       |

| J <sub>CLKout</sub>                  | LMK040x1 (Note 26)                                     | BW = 12 kHz to 20 MHz          |                | 130       |           | fs    |

| CLKout<br>LVDS                       | f <sub>CLKout</sub> = 250 MHz                          | BW = 12 KHz to 20 MHz          |                | 190       |           | ┧ ¨   |

| <del>-</del>                         | Integrated RMS Jitter                                  | DVV - 100 112 10 20 1VII 12    |                | 130       |           |       |

|                                      | LMK040x3 (Note 27)                                     | BW = 12 kHz to 20 MHz          |                | 145       |           | 1     |

|                                      | f <sub>CLKout</sub> = 250 MHz                          | BW = 12 KHz to 20 MHz          |                | 200       |           | 1     |

|                                      | Integrated RMS Jitter                                  | DVV - 100 112 to 20 WII IZ     |                | 200       |           | 1     |

| Symbol                                                                                      | Parameter                                                                                                                                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                                                                       | Min                         | Тур       | Max                            | Units                |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|--------------------------------|----------------------|

| J <sub>CLKout</sub>                                                                         | LMK040x1 (Note 26)                                                                                                                                                                                                                                                                                                   | BW = 12 kHz to 20 MHz                                                                                                                                                                                                                                                                                                                                            |                             | 125       |                                | fs                   |

| LVCMOS                                                                                      | f <sub>CLKout</sub> = 250 MHz                                                                                                                                                                                                                                                                                        | BW = 100 Hz to 20 MHz                                                                                                                                                                                                                                                                                                                                            |                             | 185       |                                |                      |

|                                                                                             | Integrated RMS Jitter                                                                                                                                                                                                                                                                                                | DVV = 100 112 to 20 Wil 12                                                                                                                                                                                                                                                                                                                                       |                             | 100       |                                |                      |

|                                                                                             | LMK040x3 (Note 27)                                                                                                                                                                                                                                                                                                   | BW = 12 kHz to 20 MHz                                                                                                                                                                                                                                                                                                                                            |                             | 145       |                                |                      |

|                                                                                             | f <sub>CLKout</sub> = 250 MHz                                                                                                                                                                                                                                                                                        | BW = 100 Hz to 20 MHz                                                                                                                                                                                                                                                                                                                                            |                             | 195       |                                |                      |

|                                                                                             | Integrated RMS Jitter                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                  |                             |           |                                |                      |

| CLKout's Internal VC                                                                        | CO Closed Loop Jitter Specific                                                                                                                                                                                                                                                                                       | ations using the Integrated Lo                                                                                                                                                                                                                                                                                                                                   | w Noise C                   | rystal Os | cillator Ci                    | rcuit                |

| J <sub>CLKout</sub>                                                                         | LMK040x1 (Note 29)                                                                                                                                                                                                                                                                                                   | BW = 12 kHz to 20 MHz                                                                                                                                                                                                                                                                                                                                            |                             | 200       |                                | fs                   |

| LVPECL/2VPECL/LVDS                                                                          | f <sub>CLKout</sub> = 245.76 MHz<br>Integrated RMS Jitter                                                                                                                                                                                                                                                            | BW = 100 Hz to 20 MHz                                                                                                                                                                                                                                                                                                                                            |                             | 230       |                                |                      |

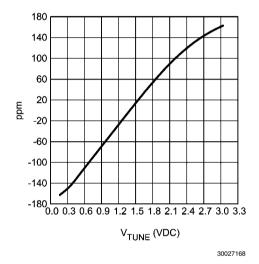

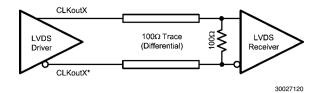

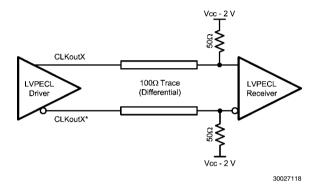

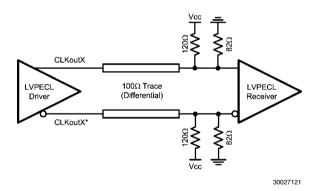

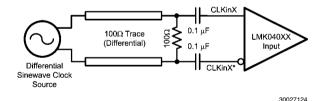

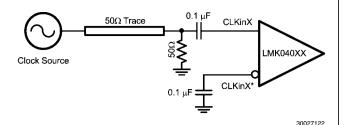

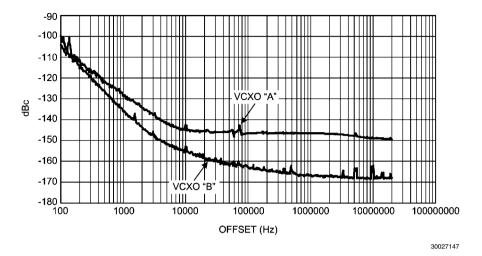

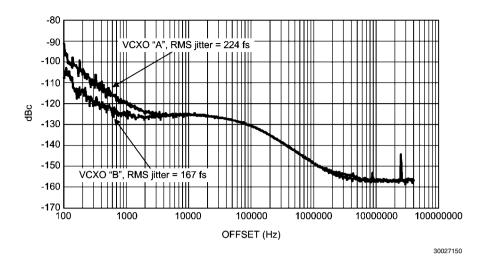

|                                                                                             | LMK040x3 (Note 30)                                                                                                                                                                                                                                                                                                   | BW = 12 kHz to 20 MHz                                                                                                                                                                                                                                                                                                                                            |                             | 245       |                                |                      |