# LM98555 CCD Driver

## General Description

The LM98555 is a highly integrated driver circuit intended for CCD driving applications. It combines 25 drivers of varying drive strengths into one chip to provide a complete CCD driving solution. Due to this one-chip integration, optimal skew control is achieved for this demanding application.

## Features

- All CCD drivers integrated into one package

- High strength drivers designed specifically for CCD loads

- Ability to scale clock driver strength

- Skew specifications guaranteed

- Separate input and output power supplies

- CMOS process technology

- 64-pin TSSOP package with extended power handling capability

## Key Specifications

|                        |                             |             |

|------------------------|-----------------------------|-------------|

| Supply Voltage         | Inputs                      | 3.0 to 5.5V |

|                        | Drivers                     | 4.5 to 5.8V |

| Maximum Output Skew    | Between P1A and P2A outputs | 0.5 ns      |

| Maximum Power Handling |                             | 2.0W        |

## Functional Description

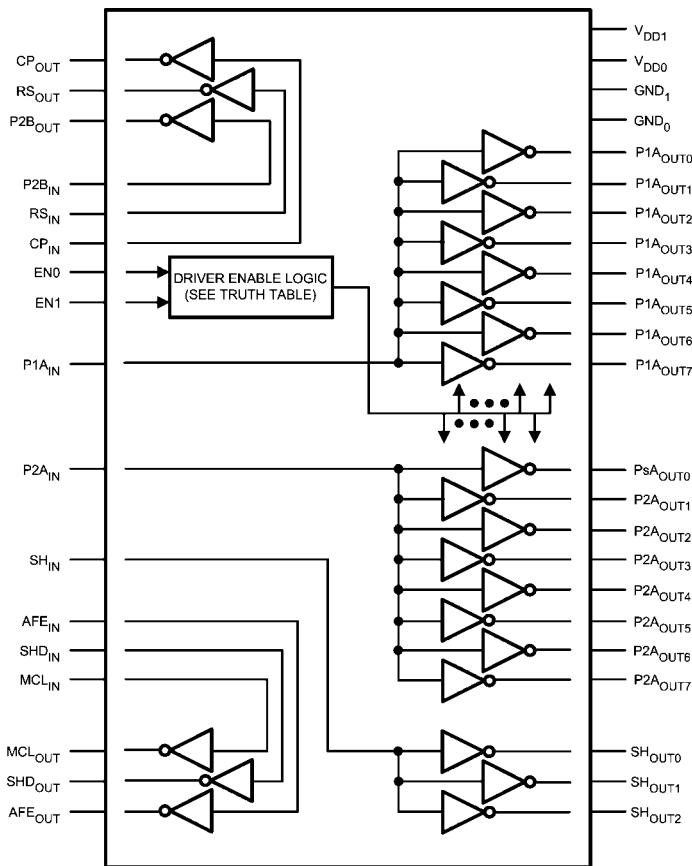

20126401

**FIGURE 1. Functional Block Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

## Ordering Information

| Commercial Temperature Range | NS Package               |

|------------------------------|--------------------------|

| LM98555CCMH                  | 64-Pin Exposed Pad TSSOP |

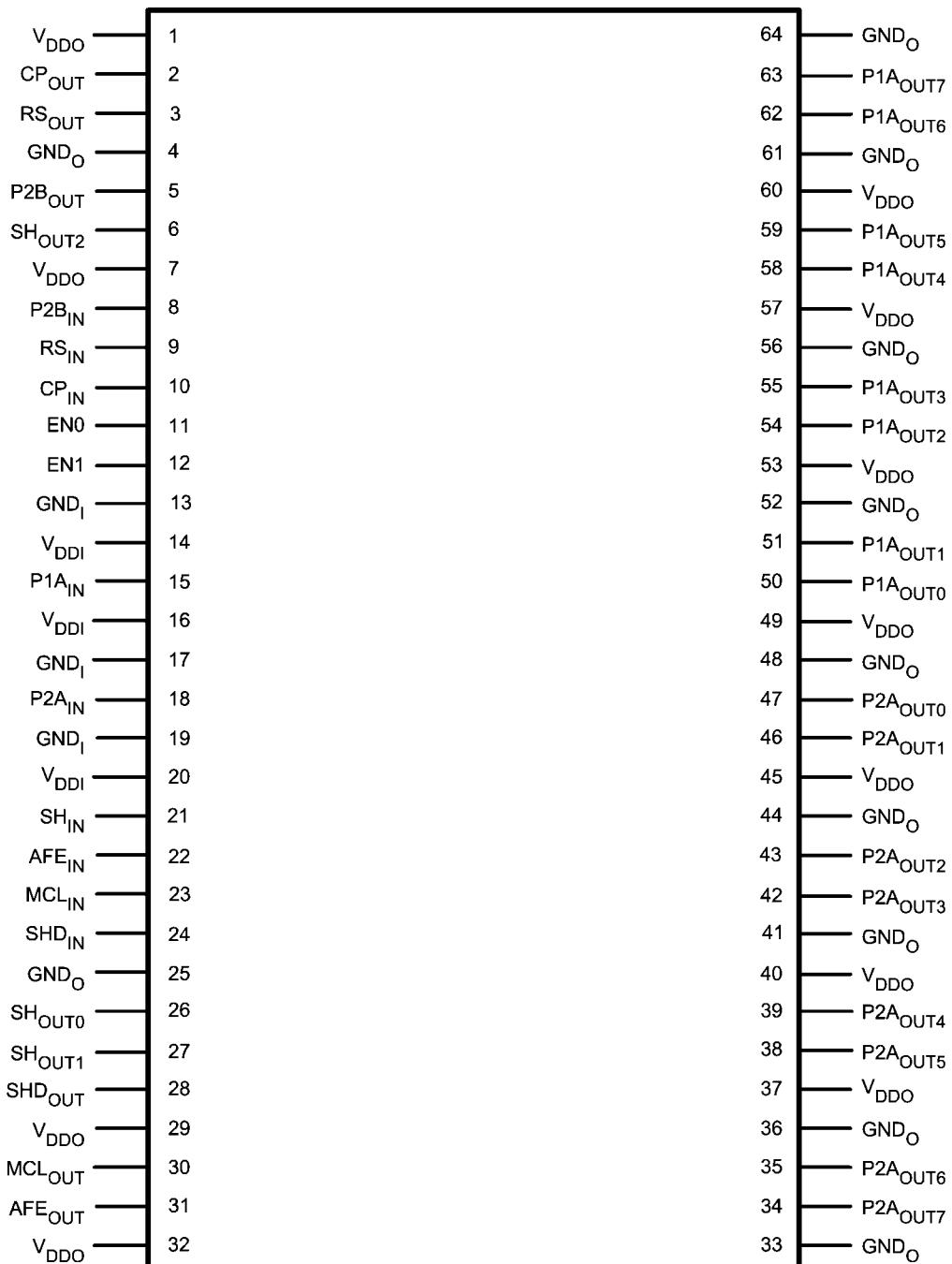

## Connection Diagram

20126402

FIGURE 2. TSSOP Package Pinout

## Pin Descriptions

| Symbol                                                                                                                                                                               | Pin                                          | Type                              | Description                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Driver inputs</b>                                                                                                                                                                 |                                              |                                   |                                                                                                                                                                                                                                                                     |

| P2B <sub>IN</sub>                                                                                                                                                                    | 8                                            | Input                             | CMOS logic input for the P2B driver.                                                                                                                                                                                                                                |

| RS <sub>IN</sub>                                                                                                                                                                     | 9                                            | Input                             | CMOS logic input for the RS driver.                                                                                                                                                                                                                                 |

| CP <sub>IN</sub>                                                                                                                                                                     | 10                                           | Input                             | CMOS logic input for the CP driver.                                                                                                                                                                                                                                 |

| P1A <sub>IN</sub>                                                                                                                                                                    | 15                                           | Input                             | CMOS logic input for the P1A ganged (8) driver set.                                                                                                                                                                                                                 |

| P2A <sub>IN</sub>                                                                                                                                                                    | 18                                           | Input                             | CMOS logic input for the P2A ganged (8) driver set.                                                                                                                                                                                                                 |

| SH <sub>IN</sub>                                                                                                                                                                     | 21                                           | Input                             | CMOS logic input for the SH ganged (3) driver set.                                                                                                                                                                                                                  |

| AFE <sub>IN</sub>                                                                                                                                                                    | 22                                           | Input                             | CMOS logic input for the AFE driver.                                                                                                                                                                                                                                |

| MCL <sub>IN</sub>                                                                                                                                                                    | 23                                           | Input                             | CMOS logic input for the MCL driver.                                                                                                                                                                                                                                |

| SHD <sub>IN</sub>                                                                                                                                                                    | 24                                           | Input                             | CMOS logic input for the SHD driver.                                                                                                                                                                                                                                |

| <b>Driver Outputs</b>                                                                                                                                                                |                                              |                                   |                                                                                                                                                                                                                                                                     |

| SHD <sub>OUT</sub>                                                                                                                                                                   | 28                                           | Output; Low-Strength              | Driver output for the SHD <sub>IN</sub> input signal.                                                                                                                                                                                                               |

| MCL <sub>OUT</sub>                                                                                                                                                                   | 30                                           | Output; Low-Strength              | Driver output for the MCL <sub>IN</sub> input signal.                                                                                                                                                                                                               |

| AFE <sub>OUT</sub>                                                                                                                                                                   | 31                                           | Output; Low-Strength              | Driver output for the AFE <sub>IN</sub> input signal.                                                                                                                                                                                                               |

| CP <sub>OUT</sub>                                                                                                                                                                    | 2                                            | Output; Low-Strength              | Driver output for the CP <sub>IN</sub> input signal. Typically used to drive the Clamp Gate input of the CCD.                                                                                                                                                       |

| RS <sub>OUT</sub>                                                                                                                                                                    | 3                                            | Output; Low-Strength              | Driver output for the RS <sub>IN</sub> input signal. Typically used to drive the Reset Gate input of the CCD.                                                                                                                                                       |

| P2B <sub>OUT</sub>                                                                                                                                                                   | 5                                            | Output; Low-Strength              | Driver output for the P2B <sub>IN</sub> input signal.                                                                                                                                                                                                               |

| P2A <sub>OUT0</sub><br>P2A <sub>OUT1</sub><br>P2A <sub>OUT2</sub><br>P2A <sub>OUT3</sub><br>P2A <sub>OUT4</sub><br>P2A <sub>OUT5</sub><br>P2A <sub>OUT6</sub><br>P2A <sub>OUT7</sub> | 47<br>46<br>43<br>42<br>39<br>38<br>35<br>34 | Output; TRI-STATE®; High-Strength | Ganged driver outputs for the P2A <sub>IN</sub> input. Typically the user may join together these outputs to drive the $\varphi_2$ clock input of the CCD. Some of these outputs may be disabled using the EN(1:0) inputs - see the Functional Description section. |

| P1A <sub>OUT0</sub><br>P1A <sub>OUT1</sub><br>P1A <sub>OUT2</sub><br>P1A <sub>OUT3</sub><br>P1A <sub>OUT4</sub><br>P1A <sub>OUT5</sub><br>P1A <sub>OUT6</sub><br>P1A <sub>OUT7</sub> | 50<br>51<br>54<br>55<br>58<br>59<br>62<br>63 | Output; TRI-STATE; High-Strength  | Ganged driver outputs for the P1A <sub>IN</sub> input. Typically the user may join together these outputs to drive the $\varphi_1$ clock input of the CCD. Some of these outputs may be disabled using the EN(1:0) inputs - see the Functional Description section. |

| SH <sub>OUT0</sub><br>SH <sub>OUT1</sub><br>SH <sub>OUT2</sub>                                                                                                                       | 26<br>27<br>6                                | Output; Low-Strength              | Ganged driver outputs for the SH <sub>IN</sub> input signal. Typically used to drive the Shift Gate input of the CCD.                                                                                                                                               |

| <b>Logic Inputs</b>                                                                                                                                                                  |                                              |                                   |                                                                                                                                                                                                                                                                     |

| EN0                                                                                                                                                                                  | 11                                           | Input                             | Driver enable control. Some of the P1A and P2A drivers can be disabled using these inputs. See the Functional Description section.                                                                                                                                  |

| EN1                                                                                                                                                                                  | 12                                           |                                   |                                                                                                                                                                                                                                                                     |

| Symbol                         | Pin                                                           | Type   | Description                                                             |

|--------------------------------|---------------------------------------------------------------|--------|-------------------------------------------------------------------------|

| <b>Power &amp; Ground Pins</b> |                                                               |        |                                                                         |

| $V_{DDI}$                      | 14<br>16<br>20                                                | Power  | $V_{DD}$ for pre-drivers.                                               |

| $V_{DDO}$                      | 1<br>7<br>29<br>32<br>37<br>40<br>45<br>49<br>53<br>57<br>60  | Power  | $V_{DD}$ for final-stage driver.                                        |

| $GND_I$                        | 13<br>17<br>19                                                | Ground | Ground connection for all circuitry other than the Final-Stage Drivers. |

| $GND_O$                        | 4<br>25<br>33<br>36<br>41<br>44<br>48<br>52<br>56<br>61<br>64 | Ground | Ground connection for the Final-Stage Drivers.                          |

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

|                                       |                         |

|---------------------------------------|-------------------------|

| Supply Voltage                        | -0.5V to 6.2V           |

| Package Power Rating at 25°C (Note 2) | 2.0 Watts               |

| Voltage on Any Input or Output Pin    | -0.5V to $V_{DD}$ +0.5V |

| DC Input Current at Any Pin           | 25 mA                   |

| DC Package Input Current              | 50 mA                   |

| Storage Temperature                   | -65°C to +150°C         |

| Lead temperature (Soldering, 10 sec.) | 300°C                   |

| ESD Susceptibility                    |                         |

| Human Body Model                      | 2000V                   |

| Machine Model                         | 200V                    |

## Package Thermal Resistances

| Package                   | $\theta_{J-A}$<br>(Note 5) | $\theta_{J-PAD}$<br>(Thermal Pad) |

|---------------------------|----------------------------|-----------------------------------|

| 64-Lead Exposed Pad TSSOP | 36.8°C / W                 | 6.2°C / W                         |

## Operating Conditions

|                               |                            |

|-------------------------------|----------------------------|

| Supply Voltage<br>$V_{DDI}$   | +3.0V to +5.5V             |

| Supply Voltage<br>$V_{DDO}$   | +4.5V to +5.8V             |

| Supply Sequencing (Note 3)    | $V_{DDI} < V_{DDO} + 0.2V$ |

| Ambient Temperature ( $T_A$ ) | 0 to 70°C                  |

| Operating Frequency           | 30 MHz                     |

| Power Dissipation (Note 4)    | 2.0W                       |

## DC Electrical Characteristics

The following specifications apply for GND = 0V,  $V_{DDI}$  = 3.3V,  $V_{DDO}$  = 5.0V, unless noted otherwise. **Boldface limits apply for  $T_A = T_{MIN}$  to  $T_{MAX}$** ; all other limits  $T_A = 25^\circ C$

| Symbol          | Parameter                            | Conditions                                                                             | Min         | Typical | Max         | Units    |

|-----------------|--------------------------------------|----------------------------------------------------------------------------------------|-------------|---------|-------------|----------|

| $I_I$           | Logic 1 Input Current                | $V_I = V_{DDI}$                                                                        | <b>-1</b>   | 0.004   | <b>1</b>    | $\mu A$  |

|                 | Logic 0 Input Current                | $V_I = GND_I$                                                                          | <b>-1</b>   | 0.006   | <b>1</b>    | $\mu A$  |

| $V_{IT}$        | Input Threshold                      | $V_{DDI} = 3.3V$                                                                       | <b>1.41</b> | 1.57    | <b>1.75</b> | V        |

|                 | Input Threshold                      | $V_{DDI} = 5.0V$                                                                       |             | 2.48    |             | V        |

|                 | Input Threshold Hysteresis           | $V_{DDI} = 3.3V$                                                                       | <b>-72</b>  | 11      | <b>100</b>  | mV       |

| $\Delta V_{IT}$ | Input Threshold Variation            | Between P1A, P2A inputs                                                                | -100        |         | 100         | mV       |

| $R_O$           | Output Impedance P1A and P2A Outputs | $I_{LOAD} = 525 \text{ mA}$<br>$R_O = (V_{DDO} - V_O)/I_{OH}$ or<br>$R_O = V_O/I_{OL}$ |             | 6.1     | <b>9.9</b>  | $\Omega$ |

| $R_O$           | Output Impedance All Other Outputs   | $I_{LOAD} = 280 \text{ mA}$<br>$R_O = (V_{DDO} - V_O)/I_{OH}$ or<br>$R_O = V_O/I_{OL}$ |             | 10.2    | <b>17.4</b> | $\Omega$ |

## AC Electrical Characteristics

The following specifications apply for  $GND = 0V$ ,  $V_{DDI} = 3.3V$ ,  $V_{DDO} = 5.0V$ , unless noted otherwise. **Boldface limits apply for  $T_A = T_{MIN}$  to  $T_{MAX}$** ; all other limits  $T_A = 25^\circ C$

| Symbol    | Parameter                                      | Conditions                                                                                      | Min         | Typical | Max         | Units |

|-----------|------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------|---------|-------------|-------|

| $t_{PHL}$ | Prop Delay: High-to-Low<br>P1A and P2A Outputs | $C_L = 220 \text{ pF}$ , $R_L = 10\Omega$<br>(Note 6)                                           | <b>3.06</b> | 4.6     | <b>6.55</b> | ns    |

| $t_{PHL}$ | Prop Delay: High-to-Low<br>CP, RS, P2B Outputs | $C_L = 82 \text{ pF}$ , $R_L = 10\Omega$<br>(Note 6)<br>(Note 8)                                |             | 4.1     |             | ns    |

| $t_{PLH}$ | Prop Delay: Low-to-High<br>P1A and P2A Outputs | $C_L = 220 \text{ pF}$ , $R_L = 10\Omega$<br>(Note 7)                                           | <b>3.38</b> | 4.9     | <b>6.68</b> | ns    |

| $t_{PLH}$ | Prop Delay: Low-to-High<br>CP, RS, P2B Outputs | $C_L = 82 \text{ pF}$ , $R_L = 10\Omega$<br>(Note 7)<br>(Note 8)                                |             | 4.2     |             | ns    |

| $t_{SKW}$ | Prop Delay Skew High-to-Low                    | Between any P1A or P2A Outputs<br>on a Single Unit<br>$C_L = 220 \text{ pF}$ , $R_L = 10\Omega$ |             | 109     | <b>387</b>  | ps    |

|           | Prop Delay Skew Low-to-High                    |                                                                                                 |             | 157     | <b>490</b>  |       |

**Important Note:** Not all drivers can be loaded to the highest specified load at the same time without violating the maximum power dissipation limit. The system design must guarantee that the maximum power dissipation specification is never exceeded.

**Note 1:** Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

**Note 2:** Package power rating assumes the exposed thermal pad is soldered to the printed circuit board as recommended, with significant heat spreading provided by vias to internal or bottom heat dissipation planes or pad. If this is not the case, then the package power rating should be reduced. See the Thermal Guidelines in the applications section for more information.

**Note 3:** When powering up and down, transient voltage levels on  $V_{DDI}$  must be lower than  $(V_{DDO} + 0.2V)$

**Note 4:** This is the power dissipated on-chip due to all currents flowing through the device - both DC and AC. This operating condition will be violated if all driver outputs are fully loaded and operating at the same time at the rated  $F_{MAX}$ . The system design must constrain the chip's operating conditions (loads, power supply, number of parallel drivers enabled, frequency of operation) to make certain that this limit is never exceeded.

**Note 5:** Package thermal resistance for junction to ambient is based on a 5.5 inch by 3 inch, 4 layer printed circuit board, with thermal vias connecting the heat sinking pad to a full internal ground plane. Tests were done in still air, with a power dissipation of 2.0 W, at an ambient temperature of 22°C.

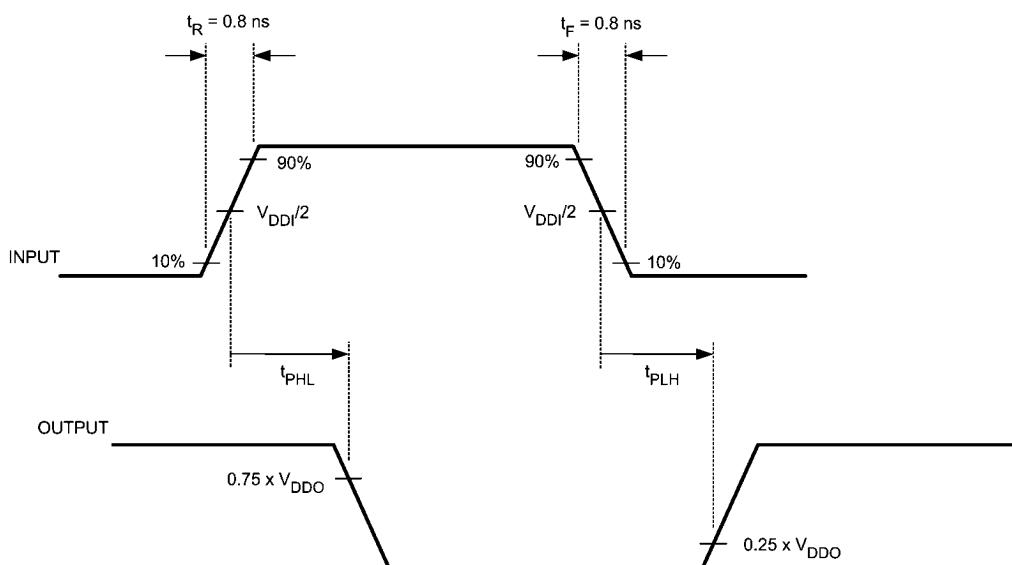

**Note 6:** Propagation Delay High-to-Low with output low trigger voltage at  $V_{DDO} \cdot 0.75$ .

**Note 7:** Propagation Delay Low-to-High with output high trigger voltage at  $V_{DDO} \cdot 0.25$ .

**Note 8:** Typical values determined from characterization testing only. Not production tested or guaranteed.

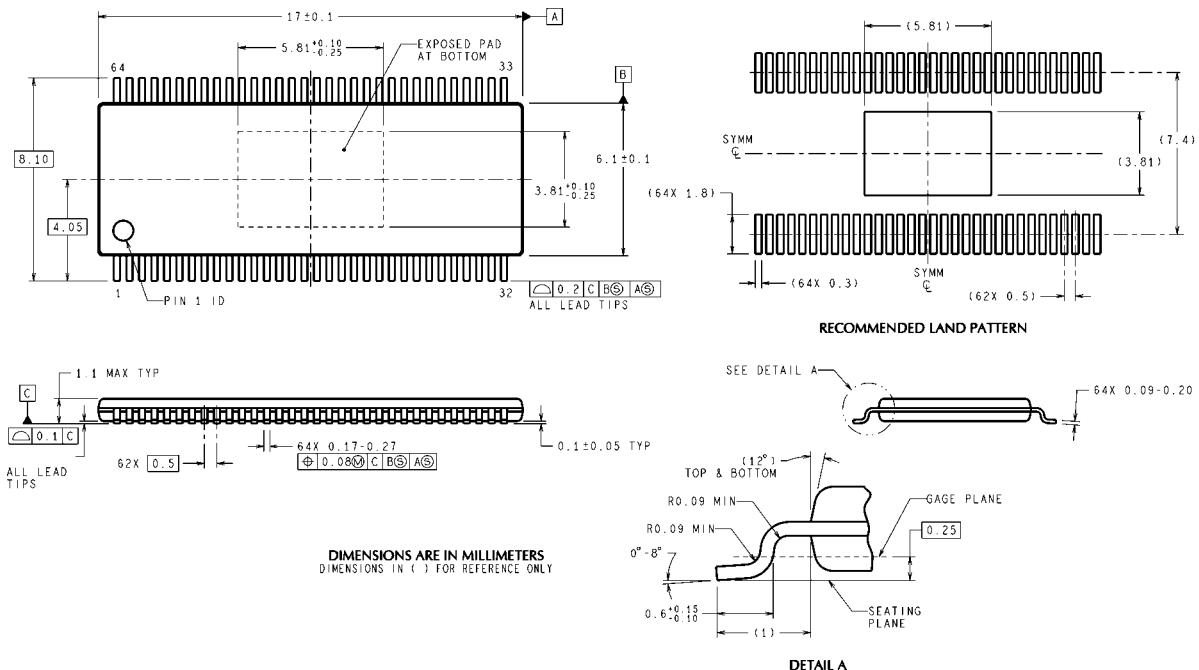

## Test Conditions

20126403

FIGURE 3. AC Test Conditions

## Application Information

The LM98555 is a fully integrated clock driver/buffer for high speed CCD applications. It provides high performance low impedance drivers, with optimized low skew performance of the P1 and P2 outputs. Enable inputs allow use of two, four, six, or all eight P1 and P2 drivers to optimize the amount of drive for the application. The 64 pin thermally enhanced TSSOP provides excellent power handling through the use of an exposed heat transfer pad on the underside of the package.

### THERMAL GUIDELINES

The LM98555's maximum power dissipation limit, shown in the Operating Conditions section, must be strictly adhered to. The product's multiple high-strength drivers, with their ability to drive a wide-range of loads, make it possible to be within spec on each output and yet violate the aggregate maximum power dissipation limit for the total product. Special caution must be paid to this by limiting the chip's operating conditions (loads, power supply, number of parallel drivers enabled, frequency of operation) to make certain that the maximum power dissipation limit is never exceeded.

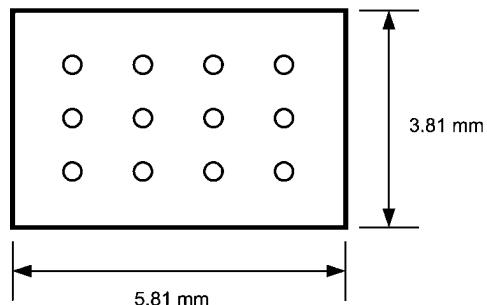

Thermal characterization of the device has been done to provide reference points under specific conditions.  $\theta_{j-a}$  junction to ambient was measured using a 5.5 inch by 3 inch, 4 layer PCB. The thermal contact pad on the board was connected using vias to a full ground plane on one of the internal layers. The recommended thermal pad is shown in *Figure 4*.

Exposed thermal pad mounting area.

Vias are 0.3 mm diameter at 1.2 mm pitch.

Recommended via plating of 1 oz copper.

20126406

**FIGURE 4. Exposed Pad Land Pattern**

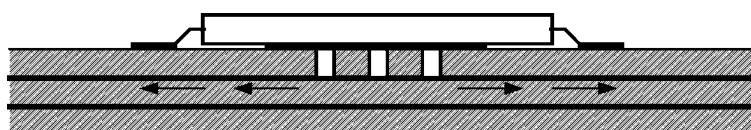

The vias shown provide a path for heat to flow from the pad to a heat sinking or dissipating area of the printed circuit board. The following figures show several typical examples of how this can be done, and illustrate how heat is conducted away from the IC to larger areas where it is dissipated.

Vias couple thermal energy to internal ground plane to transfer heat away from package.

20126407

**FIGURE 5. 4 Layer PCB - Example 1**

Vias couple thermal energy to internal ground planes and heat spreader pad on bottom layer to transfer heat away from package.

20126409

**FIGURE 6. 4 Layer PCB - Example 2**

Vias couple thermal energy to copper plane on bottom layer to transfer heat away from package.

20126408

**FIGURE 7. 2 Layer PCB**

In multi-layer board applications, one or more internal planes are usually dedicated as a ground plane. Connecting the thermal pad to this ground plane with vias will usually provide adequate heat management. In 2 layer boards, it is important to provide a large heat spreading pad on the opposite side of the board. The vias will provide a good thermal connection between the pad under the IC, and the heat spreading pad on the bottom of the board. Thermal modelling can be done using the  $\theta$  junction to pad information provided, to calculate the required area of copper based on the ambient temperature of the system, and the calculated amount of thermal dissipation in the LM98555.

### POWER DISSIPATION

The amount of power dissipated in the device can be determined by considering the following factors:

- Power dissipated delivering energy to the load capacitance

- Power dissipated delivering energy to parasitic capacitance

- Power dissipated due to leakage in the IC

The amount of power dissipated due to leakage is very small in this CMOS device. Most of the power will be due to the load capacitance being switched, with a small additional amount caused by the parasitic capacitance of the output circuitry, output pins, and PCB traces. A typical parasitic capacitance would be on the order of 5 pF. Since the load capacitance will be on the order of 100 pF or more, this usually dominates the power dissipation calculation. The following equation can be used to calculate the power dissipation due to capacitive switching of the loads:

$$P = \text{Sum}[\text{Output Frequency} \times \text{Load Capacitance} \times \text{Output Voltage Squared}] \text{ (summed for all outputs)}$$

### INPUT SIGNALS

Care should be taken to match the trace lengths between timing signals that require low skew. Usually, the P1A and P2A signals will be the most critical. In some applications, the timing of P2B with respect to P1A and P2A can also be important, and that input trace should also be carefully designed.

Trace shape and width should also be carefully controlled. The trace geometry will determine the characteristic impedance of each trace. The impedance should be set to give reasonable immunity to noise coupling into the trace. With a known trace impedance, the signals can be terminated using a series resistor at the source that is equal to the characteristic impedance. This will provide a signal with minimum overshoot and ringing, and will contribute to better performance of the final signal reaching the CCD.

### OUTPUT CONNECTIONS AND LOADING EXAMPLES

The LM98555 can be used with a wide variety of different CCD sensors. The P1Aoutx and P2Aoutx outputs can be selectively enabled to provide 2, 4, 6, or 8 drivers. This allows the available drive strength to be optimized for the sensor and application. Connecting multiple outputs together in parallel as shown in the typical application circuit provides lower drive impedance as needed to suit the load being driven. When driving smaller loads, lower switching noise will be generated if the minimum necessary outputs are enabled and used.

The output signal traces should also be designed for a known impedance. Source terminating resistors should be used in series with each output to provide good matching to the trace characteristic impedance. The resistors should be located as

close as possible to each output pin. If multiple outputs will be combined to drive a single load pin, the output signals should be combined after the termination resistors. This will provide the best summing of adjacent outputs. The combined signal should then pass through an EMI type ferrite bead. This component can be selected to change the bandwidth or shape of the clocking signal to achieve the best CCD transfer efficiency.

Several other techniques will also help maintain signal quality, and minimize timing differences between critical signals. Vias should not be used for critical timing signals. These can add impedance discontinuities that will affect the waveform quality. Traces should have gradual bends and avoid sharp changes in direction that can also introduce impedance discontinuities.

### SELECTIVE DRIVER ENABLING

With the Enable pins, the user has the capability to enable only the drivers that are required for the application, thus eliminating unnecessary outputs switching. The following table shows the details.

| EN1 | EN0 | Driver-set State                                              |

|-----|-----|---------------------------------------------------------------|

| 0   | 0   | P1Aout(1:0) and P2Aout(1:0) are enabled; all others disabled. |

| 0   | 1   | P1Aout(3:0) and P2Aout(3:0) are enabled; all others disabled. |

| 1   | 0   | P1Aout(5:0) and P2Aout(5:0) are enabled; all others disabled. |

| 1   | 1   | All P1Aout and P2Aout drivers are enabled.                    |

Note: The disabled drivers' outputs are in TRI-STATE.

### POWER SUPPLY SEQUENCING

During device power-up and power-down,  $V_{DD1}$  must be maintained less than  $(V_{DD0} + 0.2V)$  to prevent excessive current flow through the internal ESD protection circuitry. Since most applications will involve 3V on  $V_{DD1}$  and 5V on  $V_{DD0}$ , this can be easily met. If this voltage relationship cannot be met, then the DC pin and package limits for input current must be maintained by controlling the source impedance of the  $V_{DD1}$  supply.

### POWER AND GROUND - PLANES VERSUS BUSES

The best performance will be achieved by using planes rather than traces for power and ground. Planes provide lower electrical and thermal impedance. Ground bounce and ringing are reduced, electromagnetic emissions are minimized and the best thermal performance will be realized.

A single common ground plane should be used for all power and signal domains.

Another circuit board layer can be used to provide power to the various circuitry. Different power buses can be provided by isolated planes within this layer of the circuit board.

### EMI MANAGEMENT

Good EMI control will be achieved by addressing the following items:

- Provide proper source termination of output signals

- Limit length of output traces

- Ensure adequate power supply decoupling

- Provide power and ground planes as much as possible

- Provide common ground plane for all signals, especially between LM98555 outputs and load CCD

- Enable and use the minimum number of outputs needed

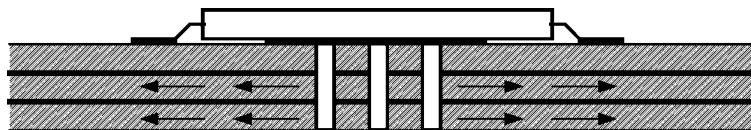

## Physical Dimensions

inches (millimeters) unless otherwise noted

**64-TSSOP**

**NS Package Number MXD64A**

MXD64A (Rev A)

## Notes

---

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

---

### LIFE SUPPORT POLICY

**NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.** As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

---

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at [www.national.com](http://www.national.com)

National Semiconductor

Americas Customer

Support Center

Email:

[new.feedback@nsc.com](mailto:new.feedback@nsc.com)

Tel: 1-800-272-9959

National Semiconductor Europe

Customer Support Center

Fax: +49 (0) 180-530-85-86

Email: [europe.support@nsc.com](mailto:europe.support@nsc.com)

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +49 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia

Pacific Customer Support Center

Email: [ap.support@nsc.com](mailto:ap.support@nsc.com)

National Semiconductor Japan

Customer Support Center

Fax: 81-3-5639-7507

Email: [jpn.feedback@nsc.com](mailto:jpn.feedback@nsc.com)

Tel: 81-3-5639-7560