#### **LM94**

# TruTherm™ Hardware Monitor with PI Loop Fan Control for Server Management

### 1.0 General Description

The LM94 hardware monitor has a two wire digital interface compatible with SMBus 2.0. Using a  $\Sigma\Delta$  ADC, the LM94 measures the temperature of four remote diode connected transistors as well as its own die and 16 power supply voltages. The LM94 has new TruTherm technology that supports precision thermal diode measurements of processors on sub-micron processes.

To set fan speed, the LM94 has two PWM outputs that are each controlled by up to six temperature zones. The fancontrol algorithm can be based on a lookup table, PI (proportional/integral) control loop, or a combination of both. The LM94 includes digital filters that can be invoked to smooth temperature readings for better control of fan speed such that acoustical noise is minimized. The LM94 has four tachometer inputs to measure fan speed. Limit and status registers for all measured values are included.

The LM94 builds upon the functionality of previous mother-board server management ASICs, such as the LM93. It also adds measurement and control support for dynamic Vccp monitoring for VRD10/11 and PROCHOT. It is designed to monitor a dual processor Xeon class motherboard with a minimum of external components.

#### 2.0 Features

- 8-bit Σ∆ ADC

- Monitors 16 power supplies

- Monitors 4 remote thermal diodes and 2 LM60

- New TruTherm technology support for precision thermal diode measurements

- Internal ambient temperature sensing

- Programmable autonomous fan control based on temperature readings with fan boost support

- Fan boost support on tachometer limit error event

- Fan control based on 13-step lookup table or PI Control Loop or combination of both

- PI fan control loop supports Tcontrol

- Temperature reading digital filters

- 0.5°C digital temperature sensor resolution

- 0.0625°C filtered temperature resolution for fan control

- 2 PWM fan speed control outputs

- 4 fan tachometer inputs

- Dual processor thermal throttling (PROCHOT) monitoring

- Dual dynamic VID monitoring (6/7 VIDs per processor) supports VRD10.2/11

- 8 general purpose I/Os:

- 4 can be configured as fan tachometer inputs

- 2 can be configured to connect to processor THERMTRIP

- 2 general purpose inputs that can be used to monitor the 7th VID signal for VRD11

- Limit register comparisons of all monitored values

- 2-wire serial digital interface, SMBus 2.0 compliant

- Supports byte/block read and write

- Selectable slave address (tri-level pin selects 1 of 3 possible addresses)

- ALERT output supports interrupt or comparator modes

- 2.5V reference voltage output

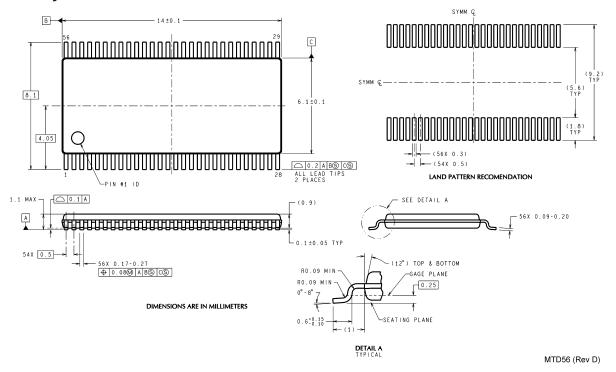

- 56-pin TSSOP package

- XOR-tree test mode

### 3.0 Key Specifications

| voltage Measurement Accuracy | ±2% F3 (IIIax  |

|------------------------------|----------------|

| Temperature Resolution       | 9-bits, 0.5°C  |

| Temperature Sensor Accuracy  | ±2.5 °C (max   |

| Temperature Range:           |                |

| — LM94 Operational           | 0°C to +85°C   |

| — Remote Temp Accuracy       | 0°C to +125°C  |

| Power Supply Voltage         | +3.0V to +3.6\ |

| Power Supply Current         | 1.6 mA         |

## 4.0 Applications

- Servers

- Workstations

- Multi-processor based equipment

## 5.0 Ordering Information

| Order Number | NS Package Number | Transport media             |

|--------------|-------------------|-----------------------------|

| LM94CIMT     | MTD56             | 34 units in rail            |

| LM94CIMTX    | MTD56             | 1000 units in tape-and-reel |

I<sup>2</sup>C is a registered trademark of the Philips Corporation.

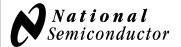

# **6.0 Block Diagram** The block diagram of LM94 hardware is illustrated below. The hardware implementation is a single chip ASIC solution.

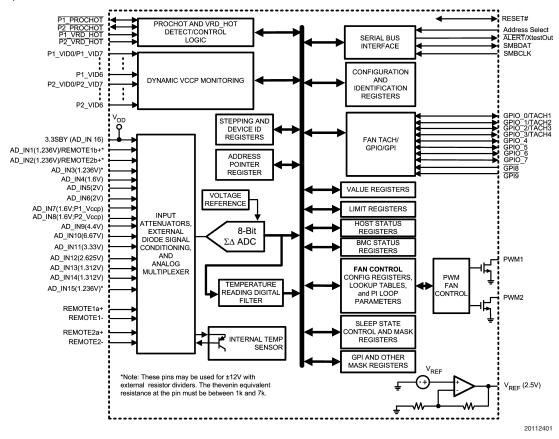

### 7.0 Application

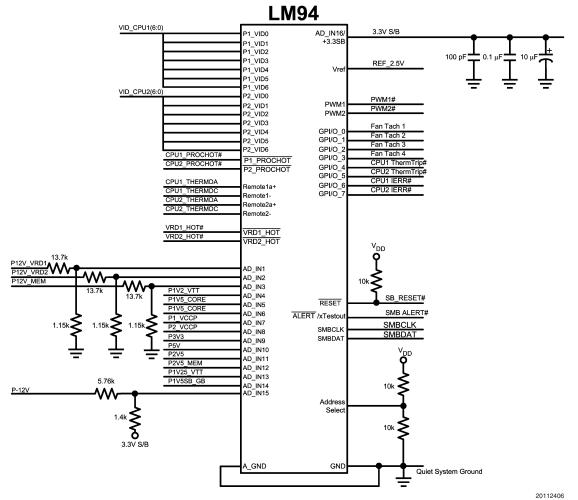

Baseboard management of a dual processor server. Two LM94s may be required to manage a quad processor board. The system diagram below shows a dual processor server

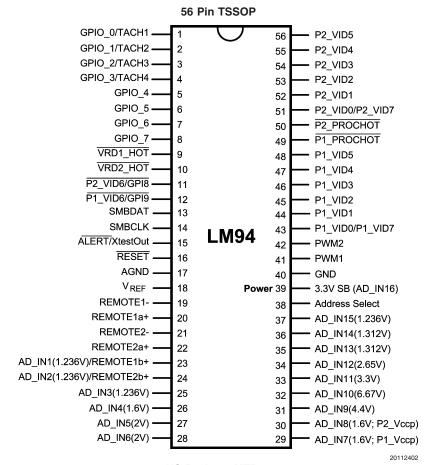

### 8.0 Connection Diagram

NS Package MTD56

Top View

NS Order Numbers:

LM94CIMT (34 units per rail), or

LM94CIMTX (1000 units per tape-and-reel)

# 9.0 Pin Descriptions

| Symbol           | Pin # | Туре           | Function                                                                 |

|------------------|-------|----------------|--------------------------------------------------------------------------|

| GPIO_0/TACH1     | 1     | Digital I/O    | Can be configured as fan tach input or a general purpose                 |

|                  |       | (Open-Drain)   | open-drain digital I/O.                                                  |

| GPIO_1/TACH2     | 2     | Digital I/O    | Can be configured as fan tach input or a general purpose                 |

|                  |       | (Open-Drain)   | open-drain digital I/O.                                                  |

| GPIO_2/TACH3     | 3     | Digital I/O    | Can be configured as fan tach input or a general purpose                 |

| oo_=,oo          |       | (Open-Drain)   | open-drain digital I/O.                                                  |

| GPIO_3/TACH4     | 4     | Digital I/O    | Can be configured as fan tach input or a general purpose                 |

| ar 10_0/1/10114  | -     | (Open-Drain)   | open-drain digital I/O                                                   |

| GPIO_4 /         | 5     | Digital I/O    | A general purpose open-drain digital I/O. Can be configured to           |

| P1_THERMTRIP     | 3     | (Open-Drain)   | monitor a CPU's THERMTRIP signal to mask other errors. Supports          |

| F I_IIILNWITNIF  |       | (Open-Diain)   | TTL input logic levels and AGTL compatible input logic levels.           |

| 000 5 /          |       | D: :: 11/0     |                                                                          |

| GPIO_5 /         | 6     | Digital I/O    | A general purpose open-drain digital I/O. Can be configured to           |

| P2_THERMTRIP     |       | (Open-Drain)   | monitor a CPU's THERMTRIP signal to mask other errors. Supports          |

|                  |       |                | TTL input logic levels and AGTL compatible input logic levels.           |

| GPIO_6           | 7     | Digital I/O    | Can be used to detect the state of CPU1 IERR or a general purpose        |

|                  |       | (Open-Drain)   | open-drain digital I/O. Supports TTL input logic levels and AGTL         |

|                  |       |                | compatible input logic levels.                                           |

| GPIO_7           | 8     | Digital I/O    | Can be used to detect the state of CPU2 IERR or a general purpose        |

|                  |       | (Open-Drain)   | open-drain digital I/O. Supports TTL input logic levels and AGTL         |

|                  |       |                | compatible input logic levels.                                           |

| VRD1_HOT         | 9     | Digital Input  | CPU1 voltage regulator HOT. Supports TTL input logic levels and          |

|                  |       |                | AGTL compatible input logic levels.                                      |

| VRD2_HOT         | 10    | Digital Input  | CPU2 voltage regulator HOT. Supports TTL input logic levels and          |

| _                |       |                | AGTL compatible input logic levels.                                      |

| P2_VID6/GPI8     | 11    | Digital Input  | CPU2 VID6 input. Could also be used as a general purpose input to        |

|                  | ' '   | 2.g.tapat      | trigger an error event. Supports TTL input logic levels and AGTL         |

|                  |       |                | compatible input logic levels.                                           |

| P1_VID6/GPI9     | 12    | Digital Input  | CPU1 VID6 input. Could also be used as a general purpose input to        |

| 1 1_V1D0/G1 13   | '-    | Digital Input  | trigger an error event. Supports TTL input logic levels and AGTL         |

|                  |       |                | compatible input logic levels.                                           |

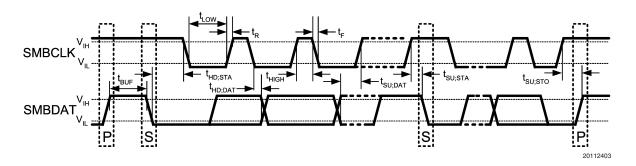

| SMBDAT           | 13    | Digital I/O    | Bidirectional System Management Bus Data. Output configured as           |

| SWIDDAT          | 13    | (Open-Drain)   | 5V tolerant open-drain. SMBus 2.0 compliant.                             |

| OMBOLIK          | 4.4   | <u> </u>       |                                                                          |

| SMBCLK           | 14    | Digital Input  | System Management Bus Clock. Driven by an open-drain output,             |

|                  |       |                | and is 5V tolerant. SMBus 2.0 Compliant.                                 |

| ALERT/XtestOut   | 15    | Digital Output | Open-drain ALERT output used in an interrupt driven system to            |

|                  |       | (Open-Drain)   | signal that an error event has occurred. Masked error events do not      |

|                  |       |                | activate the ALERT output. When in XOR tree test mode, functions         |

|                  |       |                | as XOR Tree output.                                                      |

| RESET            | 16    | Digital I/O    | Open-drain reset output when power is first applied to the LM94.         |

|                  |       | (Open-Drain)   | Used as a reset for devices powered by 3.3V stand-by. After reset,       |

|                  |       |                | this pin becomes a reset input. If this pin is not used, connection to   |

|                  |       |                | an external resistive pull-up is required to prevent LM94 malfunction.   |

| AGND             | 17    | GROUND Input   | Analog Ground. Digital ground and analog ground need to be tied          |

|                  |       |                | together at the chip then both taken to a low noise system ground.       |

|                  |       |                | A voltage difference between analog and digital ground may cause         |

|                  |       |                | erroneous results.                                                       |

| V <sub>REF</sub> | 18    | Analog Output  | 2.5V used for external ADC reference, or as a V <sub>REF</sub> reference |

| 1141             |       | 0 1            | voltage                                                                  |

# 9.0 Pin Descriptions (Continued)

| Symbol           | Pin # | Туре                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

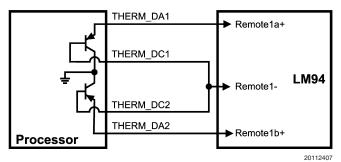

| REMOTE1-         | 19    | Remote Thermal Diode_1- Input (CPU 1 THERMDC)      | This is the negative input (current sink) from both of the CPU1 thermal diodes. Connected to THERMDC pin of Pentium processor or the emitter of a diode connected MMBT3904 NPN transistor. Serves as the negative input into the A/D for thermal diode voltage measurements. A 100 pF capacitor is optional and can be connected between REMOTE1– and REMOTE1+.                                                                   |

| REMOTE1a+        | 20    | Remote Thermal<br>Diode_1+ I/O (CPU1<br>THERMDA1)  | This is a positive connection to the first CPU1 thermal diode. Serves as the positive input into the A/D for thermal diode voltage measurements. It also serves as a current source output that forward biases the thermal diode. Connected to THERMDA pin of Pentium processor or the base of a diode connected MMBT3904 NPN transistor. A 100 pF capacitor is optional and can be connected between REMOTE1– and each REMOTE1+. |

| REMOTE2-         | 21    | Remote Thermal Diode_2 - Input (CPU2 THERMDC)      | This is the negative input (current sink) from both of the CPU2 thermal diodes. Connected to THERMDC pins of Pentium processor or the emitter of a diode connected MMBT3904 NPN transistor. Serves as the negative input into the A/D for thermal diode voltage measurements. A 100 pF capacitor is optional and can be connected between REMOTE2– and each REMOTE2+.                                                             |

| REMOTE2a+        | 22    | Remote Thermal<br>Diode_2 + I/O (CPU2<br>THERMDA1) | This is a positive connection to the first CPU2 thermal diode. Serves as the positive input into the A/D for thermal diode voltage measurements. It also serves as a current source output that forward biases the thermal diode. Connected to THERMDA pin of Pentium processor or the base of a diode connected MMBT3904 NPN transistor. A 100 pF capacitor is optional and can be connected between REMOTE2- and REMOTE2+.      |

| AD_IN1/REMOTE1b+ | 23    | Analog Input (+12V1<br>or CPU1<br>THERMDA2)        | Analog Input for +12V Rail 1 monitoring, for CPU1 voltage regulator. External attenuation resistors required such that 12V is attenuated to 0.927V for nominal 3/4 scale reading. This pin may also serve as the second positive thermal diode input for CPU1.                                                                                                                                                                    |

| AD_IN2/REMOTE2b+ | 24    | Analog Input (+12V2<br>or CPU2<br>THERMDA2)        | Analog Input for +12V Rail 2 monitoring, for CPU2 voltage regulator. External attenuation resistors required such that 12V is attenuated to 0.927V for nominal 3/4 scale reading. This pin may also serve as the second positive thermal diode input for CPU2.                                                                                                                                                                    |

| AD_IN3           | 25    | Analog Input (+12V3)                               | Analog Input for +12V Rail 3, for Memory/3GIO slots. External attenuation resistors required such that 12V is attenuated to 0.927V for nominal 3/4 scale reading.                                                                                                                                                                                                                                                                 |

| AD_IN4           | 26    | Analog Input<br>(FSB_Vtt)                          | Analog input for 1.2V monitoring, nominal ¾ scale reading                                                                                                                                                                                                                                                                                                                                                                         |

| AD_IN5           | 27    | Analog Input (3GIO /<br>PXH / MCH_Core)            | Analog input for 1.5V monitoring, nominal ¾ scale reading                                                                                                                                                                                                                                                                                                                                                                         |

| AD_IN6           | 28    | Analog Input<br>(ICH_Core)                         | Analog input for 1.5V monitoring, nominal ¾ scale reading                                                                                                                                                                                                                                                                                                                                                                         |

| AD_IN7 (P1_Vccp) | 29    | Analog Input<br>(CPU1_Vccp)                        | Analog input for +Vccp (processor voltage) monitoring.                                                                                                                                                                                                                                                                                                                                                                            |

| AD_IN8 (P2_Vccp) | 30    | Analog Input<br>(CPU2_Vccp)                        | Analog input for +Vccp (processor voltage) monitoring.                                                                                                                                                                                                                                                                                                                                                                            |

| AD_IN9           | 31    | Analog Input (+3.3V)                               | Analog input for +3.3V monitoring, nominal ¾ scale reading                                                                                                                                                                                                                                                                                                                                                                        |

| AD_IN10          | 32    | Analog Input (+5V)                                 | Analog input for +5V monitoring silver box supply monitoring, nominal 3/4 scale reading                                                                                                                                                                                                                                                                                                                                           |

# 9.0 Pin Descriptions (Continued)

| Symbol            | Pin # | Туре                                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD_IN11           | 33    | Analog Input<br>(SCSI_Core)                  | Analog input for +2.5V monitoring, nominal 3/4 scale reading. This pin may also be used to monitor an analog temperature sensor such as the LM60, since readings from this input can be routed to the fan control logic.                                                                                                                                                                                                                                                                                         |

| AD_IN12           | 34    | Analog Input<br>(Mem_Core)                   | Analog input for +1.969V monitoring, nominal ¾ scale reading.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AD_IN13           | 35    | Analog Input<br>(Mem_Vtt)                    | Analog input for +0.984V monitoring, nominal 3/4 scale reading.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AD_IN14           | 36    | Analog Input<br>(Gbit_Core)                  | Analog input for +0.984V S/B monitoring, nominal 3/4 scale reading.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AD_IN15           | 37    | Analog Input (-12V)                          | Analog input for -12V monitoring. External resistors required to scale to positive level. Full scale reading at 1.236V, , nominal 3/4 scale reading. This pin may also be used to monitor an analog temperature sensor such as the LM60, since readings from this input can be routed to the fan control logic.                                                                                                                                                                                                  |

| Address Select    | 38    | 3 level analog input                         | This input selects the lower two bits of the LM94 SMBus slave address.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3V SB (AD_IN16) | 39    | POWER (V <sub>DD</sub> ) +3.3V standby power | $V_{DD}$ power input for LM94. Generally this is connected to +3.3V standby power. The LM94 can be powered by +3.3V if monitoring in low power states is not required, but power should be applied to this input before any other pins. This pin also serves as the analog input to monitor the 3.3V stand-by (SB) voltage. It is necessary to bypass this pin with a 0.1 μF in parallel with 100 pF. A bulk capacitance of 10 μF should be in the near vicinity. The 100 pF should be closest to the power pin. |

| GND               | 40    | GROUND                                       | Digital Ground. Digital ground and analog ground need to be tied together at the chip then both taken to a low noise system ground. A voltage difference between analog and digital ground may cause erroneous results.                                                                                                                                                                                                                                                                                          |

| PWM1              | 41    | Digital Output<br>(Open-Drain)               | Fan control output 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PWM2              | 42    | Digital Output<br>(Open-Drain)               | Fan control output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1_VID0/P1_VID7   | 43    | Digital Input                                | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                        |

| P1_VID1           | 44    | Digital Input                                | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                        |

| P1_VID2           | 45    | Digital Input                                | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                        |

| P1_VID3           | 46    | Digital Input                                | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                        |

| P1_VID4           | 47    | Digital Input                                | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                        |

| P1_VID5           | 48    | Digital Input                                | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                        |

| P1_PROCHOT        | 49    | Digital I/O<br>(Open-Drain)                  | Connected to CPU1 PROCHOT (processor hot) signal through a bidirectional level shifter. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                  |

| P2_PROCHOT        | 50    | Digital I/O<br>(Open-Drain)                  | Connected to CPU2 PROCHOT (processor hot) signal through a bidirectional level shifter. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                  |

### 9.0 Pin Descriptions (Continued)

| Symbol          | Pin # | Туре          | Function                                                             |

|-----------------|-------|---------------|----------------------------------------------------------------------|

| P2_VID0/P2_VID7 | 51    | Digital Input | Voltage Identification signal from the processor. Supports TTL input |

|                 |       |               | logic levels and AGTL compatible input logic levels.                 |

| P2_VID1         | 52    | Digital Input | Voltage Identification signal from the processor. Supports TTL input |

|                 |       |               | logic levels and AGTL compatible input logic levels.                 |

| P2_VID2         | 53    | Digital Input | Voltage Identification signal from the processor. Supports TTL input |

|                 |       |               | logic levels and AGTL compatible input logic levels.                 |

| P2_VID3         | 54    | Digital Input | Voltage Identification signal from the processor. Supports TTL input |

|                 |       |               | logic levels and AGTL compatible input logic levels.                 |

| P2_VID4         | 55    | Digital Input | Voltage Identification signal from the processor. Supports TTL input |

|                 |       |               | logic levels and AGTL compatible input logic levels.                 |

| P2_VID5         | 56    | Digital Input | Voltage Identification signal from the processor. Supports TTL input |

|                 |       |               | logic levels and AGTL compatible input logic levels.                 |

The over-score indicates the signal is active low ("Not").

### 10.0 Recommended Implementation

Recommended implementation without thermal diode connections

#### 10.0 Recommended Implementation (Continued)

Note: 100 pF cap across each thermal diode is optional and should be placed close to the LM94, if used. The maximum capacitance between thermal diode pins is 300 pF.

#### Thermal diode recommended implementation

#### 11.0 Functional Description

The LM94 provides 16 channels of voltage monitoring, 4 remote thermal diode monitors, an internal/local ambient temperature sensor, 2 PROCHOT monitors, 4 fan tachometers, 8 GPIOs, THERMTRIP monitor for masking error events, 2 sets of 7 VID inputs, an ALERT output and all the associated limit registers on a single chip, and communicates to the rest of the baseboard over the System Management Bus (SMBus). The LM94 also provides 2 PWM outputs and associated fan control logic for controlling the speed of system fans. There are two sets of fan control logic, a lookup table and a PI (proportional/integral) loop controller. The lookup table and PI controller are interactive, such that the fans run at the fastest required speed. Upon a temperature or fan tach error event, the PWM outputs may be programmed such that they automatically boost to 100% duty cycle. A timer is included that sets the minimum time that the fans are in the boost condition when activated by a fan tach

The LM94 incorporates National Semiconductor's TruTherm technology for precision "Remote Diode" readings of processors on 90nm process geometry or smaller. Readings from the external thermal diodes and the internal temperature sensor are made available as an 9-bit two's-complement digital value with the LSb representing 0.5°C. Filtered temperature readings are available as a 12-bit two's-complement digital value with the LSb representing 0.0625°C.

All but 4 of the analog inputs include internal scaling resistors. External scaling resistors are required for measuring  $\pm 12 V$ . The inputs are converted to 8-bit digital values such that a nominal voltage appears at  $^{3}\!\!/_{\!4}$  scale for positive voltages and  $^{1}\!\!/_{\!4}$  scale for negative voltages. The analog inputs are intended to be connected to both baseboard resident VRDs and to standard voltage rails supplied by a SSI compliant power supply.

The LM94 has logic that ties a set of dynamically moving VID inputs to their associated Vccp analog input for real time window comparison fault determination. Voltage mapping for VRD10, VRD10 extended and VRD11are supported by the LM94. When VRD10 mode is selected GPI8 and GPI9 can be used to detect external error flags whose state is be reflected in the status registers.

Error events are captured in two sets of mirrored status registers (BMC Error Status Registers and Host Status Registers) allowing two controllers access to the status information without any interference.

The LM94's ALERT output supports interrupt mode or comparator mode of operation. The comparator mode is only functional for thermal monitoring.

The LM94 provides a number of internal registers, which are detailed in the register section of this document.

# 12.0 Please contact your local sales office for complete LM94 applications information.

### 13.0 Registers

#### 13.1 REGISTER WARNINGS

In most cases, reserved registers and register bits return zero when read. This should not be relied upon, since reserved registers can be used for future expansion of the LM94 functions.

Some registers have "N/D" for their default value. This means that the power-up default of the register is not defined. In the case of value registers, care should be taken to ensure that software does not read a value register until the associated measurement function has acquired a measurement. This applies to temperatures, voltages, fan RPM, and PROCHOT monitoring.

#### 13.2 REGISTER SUMMARY TABLE

### Register Key

| Term | Description            |  |  |  |

|------|------------------------|--|--|--|

| N/D  | Not Defined            |  |  |  |

| N/A  | Not Applicable         |  |  |  |

| R    | Read Only              |  |  |  |

| R/W  | Read or Write          |  |  |  |

| RWC  | Read or Write to Clear |  |  |  |

| Lock | Register Name                           | Address     | Description                                                                                      |

|------|-----------------------------------------|-------------|--------------------------------------------------------------------------------------------------|

| FACT | ORY REGISTERS                           |             |                                                                                                  |

| Х    | XOR Test                                | 00h         | Used to set the XOR test tree mode                                                               |

|      | SMBus Test                              | 01h         | SMBus read/write test register                                                                   |

|      | Reserved                                | 02h-04h     |                                                                                                  |

| "REM | OTE DIODE" MODE SELECT                  |             |                                                                                                  |

| Х    | Transistor Mode Select                  | 05h         | Selects Diode Mode (default) or Transistor Mode for "Remote Diode" measurements                  |

| VALU | E REGISTER SECTION 1                    | •           |                                                                                                  |

|      | Zone 1b (CPU1 Diode b) Temp             | 06h         | Measured value of remote thermal diode temperature channel 1b                                    |

|      | Zone 2b (CPU2 Diode b) Temp             | 07h         | Measured value of remote thermal diode temperature channel 2b                                    |

|      | Zone 1b (CPU1 Diode b) Filtered Temp    | 08h         | Filtered value of remote thermal diode temperature channel 1b                                    |

|      | Zone 2b (CPU2 Diode b) Fitlered<br>Temp | 09h         | Filtered value of remote thermal diode temperature channel 2                                     |

|      | PWM1 8-bit Duty Cycle Value             | 0Ah         | 8- bit value of the PWM1 duty cycle.                                                             |

|      | PWM2 8-bit Duty Cycle Value             | 0Bh         | 8-bit value of the PWM2 duty cycle                                                               |

| HIGH | RESOLUTION PWM OVERIDE REGIST           | TERS        |                                                                                                  |

| х    | PWM1 Duty Cycle Override (low byte)     | 0Ch         | Lower byte of the high resolution PWM1 duty cycle register                                       |

| Х    | PWM1 Duty Cycle Override (high byte)    | 0Dh         | Upper byte of the high resolution PWM1 duty cycle register                                       |

| Х    | PWM2 Duty Cycle Override (low byte)     | 0Eh         | Lower byte of the high resolution PWM2 duty cycle register                                       |

| Х    | PWM2 Duty Cycle Override (high byte)    | 0Fh         | Upper byte of the high resolution PWM2 duty cycle register                                       |

| EXTE | NDED RESOLUTION TEMPERATURE             | VALUE REGIS | TERS                                                                                             |

|      | Z1a_LSB                                 | 10h         | Zone 1a (CPU1) extended resolution unfiltered temperature value register, least-significant byte |

|      | Z1a_MSB                                 | 11h         | Zone 1a (CPU1) extended resolution unfiltered temperature value register, most-significant byte  |

|      | Z1b_LSB                                 | 12h         | Zone 1b (CPU1) extended resolution unfiltered temperature value register, least-significant-byte |

|      | Z1b_MSB                                 | 13h         | Zone 1b (CPU1) extended resolution unfiltered temperature value register, most-significant byte  |

|      | Z2a_LSB                                 | 14h         | Zone 2a (CPU2) extended resolution unfiltered temperature value register, least-significant-byte |

|      | Z2a_MSB                                 | 15h         | Zone 2a (CPU2) extended resolution unfiltered temperature value register, most-significant byte  |

| Lock | Register Name                 | Address     | Description                                                     |

|------|-------------------------------|-------------|-----------------------------------------------------------------|

| EXTE | NDED RESOLUTION TEMPERATURE   | VALUE REGIS | TERS                                                            |

|      | Z2b_LSB                       | 16h         | Zone 2b (CPU2) extended resolution unfiltered temperature       |

|      |                               |             | value register, least-significant-byte                          |

|      | Z2b_MSB                       | 17h         | Zone 2b (CPU2) extended resolution unfiltered temperature       |

|      |                               |             | value register, most-significant byte                           |

|      | Z1a_F_LSB                     | 18h         | Zone 1a (CPU1) extended resolution filtered temperature value   |

|      |                               |             | register, least-significant byte                                |

|      | Z1a_F_MSB                     | 19h         | Zone 1a (CPU1) extended resolution filtered temperature value   |

|      |                               |             | register, most-significant byte                                 |

|      | Z1b_F_LSB                     | 1Ah         | Zone 1b (CPU1) extended resolution filtered temperature value   |

|      |                               |             | register, least-significant-byte                                |

|      | Z1b_F_MSB                     | 1Bh         | Zone 1b (CPU1) extended resolution filtered temperature value   |

|      |                               |             | register, most-significant byte                                 |

|      | Z2a_F_LSB                     | 1Ch         | Zone 2a (CPU2) extended resolution filtered temperature value   |

|      |                               |             | register, least-significant-byte                                |

|      | Z2a_F_MSB                     | 1Dh         | Zone 2a (CPU2) extended resolution filtered temperature value   |

|      |                               |             | register, most-significant byte                                 |

|      | Z2b_F_LSB                     | 1Eh         | Zone 2b (CPU2) extended resolution filtered temperature value   |

|      |                               |             | register, least-significant-byte                                |

|      | Z2b_F_MSB                     | 1Fh         | Zone 2b (CPU2) extended resolution filtered temperature value   |

|      |                               |             | register, most-significant byte                                 |

|      | Z3_LSB                        | 20h         | Zone 3 (Internal) extended resolution temperature value         |

|      |                               |             | register, least-significant byte                                |

|      | Z3_MSB                        | 21h         | Zone 3 (Internal) extended resolution temperature value         |

|      |                               |             | register, least-significant byte                                |

|      | Z4_LSB                        | 22h         | Zone 4 (External Digital) extended resolution temperature value |

|      |                               |             | register, most-significant byte                                 |

|      | Z4_MSB                        | 23h         | Zone 4 (External Digital) extended resolution temperature value |

|      |                               |             | register, least-significant byte                                |

|      |                               |             |                                                                 |

|      | Reserved                      | 24h-30h     |                                                                 |

|      |                               |             |                                                                 |

| I LO | OP AND FAN CONTROL SETUP REGI | STERS       |                                                                 |

|      | Temperature Source Select     | 31h         | Selects the temperature source for some temperature zones.      |

|      | PWM Filter Settings           | 32h         | Sets the IIR filter coefficients for the PWM outputs for low    |

|      |                               |             | resolution sources                                              |

|      | PWM1 Filter Shutoff Threshold | 33h         | PWM1 Filter Shutoff Threshold                                   |

|      | PWM2 Filter Shutoff Threshold | 34h         | PWM2 Filter Shutoff Threshold                                   |

|      | PI/LUT Fan Control Bindings   | 35h         | PI/LUT fan control binding configuration                        |

|      | PI Controller Minimum PWM and | 36h         | PI Controller Minimum PWM and Hysteresis settings               |

|      | Hysteresis                    |             |                                                                 |

|      | Zone 1 Tcontrol               | 37h         | Zone 1 (CPU1) PI Controller Target Temperature (Tcontrol)       |

|      | Zone 2 Tcontrol               | 38h         | Zone 2 (CPU2) PI Controller Target Temperature (Tcontrol)       |

|      | Zone 1 Toff                   | 39h         | Zone 1 (CPU1) PI Controller Off Temperature (Toff)              |

|      | Zone 2 Toff                   | 3Ah         | Zone 2 (CPU2) PI Controller Off Temperature (Toff)              |

|      | P Coefficient                 | 3Bh         | PI controller proportional coefficient                          |

|      | I Coefficient                 | 3Ch         | PI controller integral coefficient                              |

|      | PI Exponents                  | 3Dh         | PI controller coefficient exponents                             |

|      | Exponente                     | JUII        | 1.1 Softional additional exponents                              |

|      | E IDENTIFICATION REGISTERS    |             |                                                                 |

| Lock Register Name                  | Address | Description                                                    |

|-------------------------------------|---------|----------------------------------------------------------------|

| PI LOOP AND FAN CONTROL SETUP REGIS | TERS    |                                                                |

| Version/Stepping                    | 3Fh     | Contains code for major and minor revisions                    |

| BMC ERROR STATUS REGISTERS          |         |                                                                |

| B_Error Status 1                    | 40h     | BMC error status register 1                                    |

| B_Error Status 2                    | 41h     | BMC error register 2                                           |

| B_Error Status 3                    | 42h     | BMC error register 3                                           |

| B_Error Status 4                    | 43h     | BMC error register 4                                           |

| B_P1_PROCHOT Error Status           | 44h     | BMC error register for P1_PROCHOT                              |

| B_P2_PROCHOT Error Status           | 45h     | BMC error register for P2_PROCHOT                              |

| B_GPI Error Status                  | 46h     | BMC error register for GPIs                                    |

| B_Fan Error Status                  | 47h     | BMC error register for Fans                                    |

| HOST ERROR STATUS REGISTERS         |         |                                                                |

| H_Error Status 1                    | 48h     | HOST error status register 1                                   |

| H_Error Status 2                    | 49h     | HOST error register 2                                          |

| H_Error Status 3                    | 4Ah     | HOST error register 3                                          |

| H_Error Status 4                    | 4Bh     | HOST error register 4                                          |

| H_P1_PROCHOT Error Status           | 4Ch     | HOST error register for P1_PROCHOT                             |

| H_P2_PROCHOT Error Status           | 4Dh     | HOST error register for P2_PROCHOT                             |

| H_GPI Error Status                  | 4Eh     | HOST error register for GPIs                                   |

| H_Fan Error Status                  | 4Fh     | HOST error register for Fans                                   |

| VALUE REGISTERS SECTION 2           |         |                                                                |

| Zone 1a (CPU1) Temp                 | 50h     | Measured value of remote thermal diode temperature channel  1a |

| Zone 2a (CPU2) Temp                 | 51h     | Measured value of remote thermal diode temperature channel 2a  |

| Zone 3 (Internal) Temp              | 52h     | Measured temperature from on-chip sensor                       |

| Zone 4 (External Digital) Temp      | 53h     | Measured temperature from external temperature sensor          |

| Zone 1a (CPU1) Filtered Temp        | 54h     | Filtered value of remote thermal diode temperature channel 1a  |

| Zone 2a (CPU2) Filtered Temp        | 55h     | Filtered value of remote thermal diode temperature channel 2a  |

| AD_IN1 Voltage                      | 56h     | Measured value of AD_IN1                                       |

| AD_IN2 Voltage                      | 57h     | Measured value of AD_IN2                                       |

| AD_IN3 Voltage                      | 58h     | Measured value of AD_IN3                                       |

| AD_IN4 Voltage                      | 59h     | Measured value of AD_IN4                                       |

| AD_IN5 Voltage                      | 5Ah     | Measured value of AD_IN5                                       |

| AD_IN6 Voltage                      | 5Bh     | Measured value of AD_IN6                                       |

| AD_IN7 Voltage                      | 5Ch     | Measured value of AD_IN7                                       |

| AD_IN8 Voltage                      | 5Dh     | Measured value of AD_IN8                                       |

| AD_IN9 Voltage                      | 5Eh     | Measured value of AD_IN9                                       |

| AD_IN10 Voltage                     | 5Fh     | Measured value of AD_IN10                                      |

| AD_IN11 Voltage                     | 60h     | Measured value of AD_IN11                                      |

| AD_IN12 Voltage                     | 61h     | Measured value of AD_IN12                                      |

| AD_IN13 Voltage                     | 62h     | Measured value of AD_IN13                                      |

| AD_IN14 Voltage                     | 63h     | Measured value of AD_IN14                                      |

| AD_IN15 Voltage                     | 64h     | Measured value of AD_IN15                                      |

| AD_IN16 Voltage                     | 65h     | Measured value of AD_IN16 (V <sub>DD</sub> 3.3V S/B)           |

| Reserved                            | 66h     |                                                                |

| Current P1_PDCCUCT                  | 675     | Magazirad D1 DDOCHOT through a consection                      |

| Current P1_PROCHOT                  | 67h     | Measured P1_PROCHOT throttle percentage                        |

| Lock  | Register Name                       | Address    | Description                                                                          |

|-------|-------------------------------------|------------|--------------------------------------------------------------------------------------|

| VALUE | E REGISTERS SECTION 2               |            |                                                                                      |

|       | Average P1_PROCHOT                  | 68h        | Average P1_PROCHOT throttle percentage                                               |

|       | Current P2_PROCHOT                  | 69h        | Measured P2_PROCHOT throttle percentage                                              |

|       | Average P2_PROCHOT                  | 6Ah        | Average P2_PROCHOT throttle percentage                                               |

|       |                                     |            |                                                                                      |

|       | GPI State                           | 6Bh        | Current GPIO state                                                                   |

|       | P1_VID                              | 6Ch        | Current VID value of Processor 1                                                     |

|       | P2_VID                              | 6Dh        | Current VID value of Processor 2                                                     |

|       | FAN Tach 1 LSB                      | 6Eh        | Measured FAN Tach 1 LSB                                                              |

|       | FAN Tach 1 MSB                      | 6Fh        | Measured FAN Tach 1 MSB                                                              |

|       |                                     |            |                                                                                      |

|       | FAN Tach 2 LSB                      | 70h        | Measured FAN Tach 2 LSB                                                              |

|       | FAN Tach 2 MSB                      | 71h        | Measured FAN Tach 2 MSB                                                              |

|       | FAN Tach 3 LSB                      | 72h        | Measured FAN Tach 3 LSB                                                              |

|       | FAN Tach 3 MSB                      | 73h        | Measured FAN Tach 3 MSB                                                              |

|       | FAN Tach 4 LSB                      | 74h        | Measured FAN Tach 4 LSB                                                              |

|       | FAN Tach 4 MSB                      | 75h        | Measured FAN Tach 4 MSB                                                              |

|       | Reserved                            | 76h-77h    |                                                                                      |

|       |                                     |            |                                                                                      |

| EMP   | ERATURE LIMIT REGISTERS             |            |                                                                                      |

|       | Zone 1 (CPU1) Low Temp              | 78h        | Low limit for external thermal diode temperature channel 1 (D1 measurement           |

|       | Zone 1 (CPU1) High Temp             | 79h        | High limit for external thermal diode temperature channel 1 (D1) measurement         |

|       | Zone 2 (CPU2) Low Temp              | 7Ah        | Low limit for external thermal diode temperature channel 2 (D2 measurement           |

|       | Zone 2 (CPU2) High Temp             | 7Bh        | High limit for external thermal diode temperature channel 2 (D2) measurement         |

|       | Zone 3 (Internal) Low Temp          | 7Ch        | Low limit for local temperature measurement                                          |

|       | Zone 3 (Internal) High Temp         | 7Dh        | High limit for local temperature measurement                                         |

|       | Zone 4 (External Digital) Low Temp  | 7Eh        | Low limit for external digital temperature sensor                                    |

|       | Zone 4 (External Digital) High Temp | 7Fh        | High limit for external digital temperature sensor                                   |

|       |                                     | 201        | 7 (00)                                                                               |

|       | Fan Boost Temp Zone 1               | 80h        | Zone 1 (CPU1) fan boost temperature                                                  |

|       | Fan Boost Temp Zone 2               | 81h        | Zone 2 (CPU2) fan boost temperature                                                  |

|       | Fan Boost Temp Zone 3               | 82h        | Zone 3 (Internal) fan boost temperature                                              |

|       | Fan Boost Temp Zone 4               | 83h        | Zone 4 (External Digital) fan boost temperature                                      |

|       | Zone1 and Zone 2 Hysteresis         | 84h        | Zone 1 and Zone 2 hysteresis for limit comparisons                                   |

|       | Zone 3 and Zone 4 Hysteresis        | 85h        | Zone 3 and Zone 4 hysteresis for limit comparisons                                   |

|       | Reserved                            | 86h-8Dh    |                                                                                      |

| 'ON-  | 46 and 06 TEMPERATURE REARING       | AD IIIOTAE | T DECICTEDS                                                                          |

| ONE   | 1b and 2b TEMPERATURE READING       |            |                                                                                      |

|       | Zone 1b Temp Adjust                 | 8Eh        | Allows all Zone 1b temperature measurements to be adjusted by a programmable offset. |

| 1     | 1                                   | 1          | 2) a programmatio ontota                                                             |

|       | Zone 2b Temp Adjust                 | 8Fh        | Allows all Zone 2b temperature measurements to be adjusted                           |

| _ock     | Register Name            | Address | Description                                           |

|----------|--------------------------|---------|-------------------------------------------------------|

| OTHE     | R LIMIT REGISTERS        |         |                                                       |

|          | AD_IN1 Low Limit         | 90h     | Low limit for analog input 1 measurement              |

|          | AD_IN1 High Limit        | 91h     | High limit for analog input 1 measurement             |

|          | AD_IN2 Low Limit         | 92h     | Low limit for analog input 2 measurement              |

|          | AD_IN2 High Limit        | 93h     | High limit for analog input 2 measurement             |

|          | AD_IN3 Low Limit         | 94h     | Low limit for analog input 3 measurement              |

|          | AD_IN3 High Limit        | 95h     | High limit for analog input 3 measurement             |

|          | AD_IN4 Low Limit         | 96h     | Low limit for analog input 4 measurement              |

|          | AD_IN4 High Limit        | 97h     | High limit for analog input 4 measurement             |

|          | AD_IN5 Low Limit         | 98h     | Low limit for analog input 5 measurement              |

|          | AD_IN5 High Limit        | 99h     | High limit for analog input 5 measurement             |

|          | AD_IN6 Low Limit         | 9Ah     | Low limit for analog input 6 measurement              |

|          | AD_IN6 High Limit        | 9Bh     | High limit for analog input 6 measurement             |

|          | AD_IN7 Low Limit         | 9Ch     | Low limit for analog input 7 measurement              |

|          | AD_IN7 High Limit        | 9Dh     | High limit for analog input 7 measurement             |

|          | AD_IN8 Low Limit         | 9Eh     | Low limit for analog input 8 measurement              |

|          | AD_IN8 High Limit        | 9Fh     | High limit for analog input 8 measurement             |

|          | AD_IN9 Low Limit         | A0h     | Low limit for analog input 9 measurement              |

|          | AD_IN9 High Limit        | A1h     | High limit for analog input 9 measurement             |

|          | AD_IN10 Low Limit        | A2h     | Low limit for analog input 10 measurement             |

|          | AD_IN10 High Limit       | A3h     | High limit for analog input 10 measurement            |

|          | AD_IN11 Low Limit        | A4h     | Low limit for analog input 11 measurement             |

|          | AD_IN11 High Limit       | A5h     | High limit for analog input 11 measurement            |

|          | AD_IN12 Low Limit        | A6h     | Low limit for analog input 12 measurement             |

|          | AD_IN12 High Limit       | A7h     | High limit for analog input 12 measurement            |

|          | AD_IN13 Low Limit        | A8h     | Low limit for analog input 13 measurement             |

|          | AD_IN13 High Limit       | A9h     | High limit for analog input 13 measurement            |

|          | AD_IN14 Low Limit        | AAh     | Low limit for analog input 14 measurement             |

|          | AD_IN14 High Limit       | ABh     | High limit for analog input 14 measurement            |

|          | AD_IN15 Low Limit        | ACh     | Low limit for analog input 15 measurement             |

|          | AD_IN15 High Limit       | ADh     | High limit for analog input 15 measurement            |

|          | AD_IN16 Low Limit        | AEh     | Low limit for analog input 16 measurement             |

|          | AD_IN16 High Limit       | AFh     | High limit for analog input 16 measurement            |

|          | AD_INTO Flight Limit     | AIII    | riigir iiriit lor aralog iriput 10 measurement        |

|          | P1_PROCHOT User Limit    | B0h     | User settable limit for P1_PROCHOT                    |

|          | P2_PROCHOT User Limit    | B1h     | User settable limit for P2_PROCHOT                    |

|          | 12_11toorio1 osei Liinit | Dill    | Oser settable little for 12_1 moonor                  |

|          | Vccp1 Limit Offsets      | B2h     | VID offset values for window comparator for CPU1 Vccp |

|          | Voop i Liinit Onsets     | DZII    | (AD_IN7)                                              |

|          | Vccp2 Limit Offsets      | B3h     | VID offset values for window comparator for CPU2 Vccp |

|          | 1 30p2 2 3               | 20      | (AD_IN8)                                              |

|          |                          |         | ′                                                     |

|          | FAN Tach 1 Limit LSB     | B4h     | FAN Tach 1 Limit LSB                                  |

|          | FAN Tach 1 Limit MSB     | B5h     | FAN Tach 1 Limit MSB                                  |

|          | FAN Tach 2 Limit LSB     | B6h     | FAN Tach 2 Limit LSB                                  |

| $\dashv$ | FAN Tach 2 Limit MSB     | B7h     | FAN Tach 2 Limit MSB                                  |

| $\dashv$ | FAN Tach 3 Limit LSB     | B8h     | FAN Tach 3 Limit USB                                  |

|          | FAN Tach 3 Limit MSB     | B9h     | FAN Tach 3 Limit MSB                                  |

| - 1      | FAN Tach 4 Limit LSB     | BAh     | FAN Tach 4 Limit LSB                                  |

| Lock | Register Name                     | Address | Description                                                                                                                                                     |

|------|-----------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTHE | R LIMIT REGISTERS                 |         |                                                                                                                                                                 |

|      | FAN Tach 4 Limit MSB              | BBh     | FAN Tach 4 Limit MSB                                                                                                                                            |

| SETU | PREGISTERS                        |         |                                                                                                                                                                 |

|      | Special Function Control 1        | BCh     | Controls the hysteresis for voltage limit comparisons. Also selects filtered or unfiltered temperature usage for temperature limit comparisons and fan control. |

|      | Special Function Control 2        | BDh     | Enables smart tach detection. Also selects 0.5°C or 1.0°C resolution for fan control.                                                                           |

| х    | GPI / VID Level Control           | BEh     | Control the input threshold levels for the P1_VIDx, P2_VIDx and GPIO_x inputs.                                                                                  |

| X    | PWM Ramp Control                  | BFh     | Controls the ramp rate of the PWM duty cycle when VRDx_HOT is asserted, as well as the ramp rate when PROCHOT exceeds the user threshold.                       |

| Х    | Fan Boost Hysteresis (Zones 1/2)  | C0h     | Fan Boost Hysteresis for zones 1 and 2                                                                                                                          |

| х    | Fan Boost Hysteresis (Zones 3/4)  | C1h     | Fan Boost Hysteresis for zones 3 and 4                                                                                                                          |

| X    | Zones 1/2 Spike Smoothing Control | C2h     | Configures Spike Smoothing for zones 1 and 2                                                                                                                    |

| Х    | LUT 1/2 MinPWM and Hysteresis     | C3h     | Controls MinPWM and hysteresis setting for LUT 1 and 2 auto-fan control                                                                                         |

| х    | LUT 3/4 MinPWM and Hysteresis     | C4h     | Controls MinPWM and hysteresis setting for LUT 3 and 4 auto-fan control                                                                                         |

|      | GPO                               | C5h     | Controls the output state of the GPIO pins                                                                                                                      |

|      | PROCHOT Control                   | C6h     | Controls assertion of P1_PROCHOT or P2_PROCHOT                                                                                                                  |

|      | PROCHOT Time Interval             | C7h     | Configures the time window over which the PROCHOT inputs are measured                                                                                           |

| Х    | PWM1 Control 1                    | C8h     | Controls PWM control source bindings.                                                                                                                           |

| Х    | PWM1 Control 2                    | C9h     | Controls PWM override and output polarity                                                                                                                       |

| Х    | PWM1 Control 3                    | CAh     | Controls PWM spin-up duration and duty cycle                                                                                                                    |

| Х    | PWM1 Control 4                    | CBh     | Frequency control for PWM1.                                                                                                                                     |

| Х    | PWM2 Control 1                    | CCh     | Controls PWM control source bindings.                                                                                                                           |

| Х    | PWM2 Control 2                    | CDh     | Controls PWM override and output polarity                                                                                                                       |

| Х    | PWM2 Control 3                    | CEh     | Controls PWM spin-up duration and duty cycle                                                                                                                    |

| Х    | PWM2 Control 4                    | CFh     | Frequency control for PWM2                                                                                                                                      |

| х    | LUT 1 Base Temperature            | D0h     | Base temperature to which look-up table offset is applied for LUT 1                                                                                             |

| х    | LUT 2 Base Temperature            | D1h     | Base temperature to which look-up table offset is applied for LUT 2                                                                                             |

| Х    | LUT 3 Base Temperature            | D2h     | Base temperature to which look-up table offset is applied for LUT 3                                                                                             |

| х    | LUT 4 Base Temperature            | D3h     | Base temperature to which look-up table offset is applied for LUT 4                                                                                             |

| Х    | Step 2 Temp Offset                | D4h     | Step 2 LUT 1/2 and LUT 3/4 Offset Temperatures                                                                                                                  |

| Х    | Step 3 Temp Offset                | D5h     | Step 3 LUT 1/2 and LUT 3/4 Offset Temperatures                                                                                                                  |

| х    | Step 4 Temp Offset                | D6h     | Step 4 LUT 1/2 and LUT 3/4 Offset Temperatures                                                                                                                  |

| х    | Step 5 Temp Offset                | D7h     | Step 5 LUT 1/2 and LUT 3/4 Offset Temperatures                                                                                                                  |

| Lock      |                                                                                                                                                           | Address                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|