SBAS262C - APRIL 2003 - REVISED JUNE 2007

# 12-Bit, 65MSPS Sampling, +3.3V ANALOG-TO-DIGITAL CONVERTER

### **FEATURES**

HIGH SNR: 70dBHIGH SFDR: 88dBFSLOW POWER: 285mW

INTERNAL/EXTERNAL REFERENCE OPTION

SINGLE-ENDED OR FULLY DIFFERENTIAL ANALOG INPUT

• FLEXIBLE DUTY CYCLE ADJUST CIRCUITRY

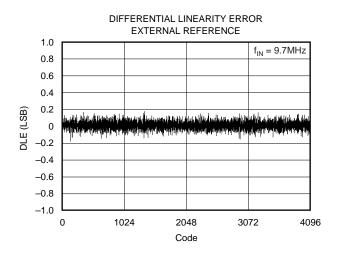

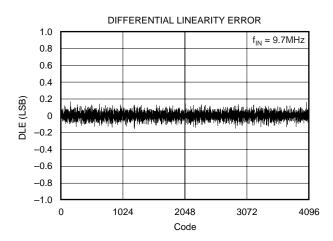

● LOW DNL: 0.5LSB

● SINGLE +3.3V SUPPLY OPERATION

• TQFP-48

## **APPLICATIONS**

- WIRELESS LOCAL LOOP

- COMMUNICATIONS

- MEDICAL IMAGING

- PORTABLE INSTRUMENTATION

### DESCRIPTION

The ADS5221 is a pipeline, CMOS Analog-to-Digital Converter (ADC) that operates from a single +3.3V power supply. This converter provides excellent performance with a single-ended input and can be operated with a differential input for added spurious performance. This high-performance converter includes a 12-bit quantizer, high bandwidth track-and-hold, and a high accuracy internal reference; it also allows for the user to disable the internal reference and utilize external references, providing excellent gain and offset matching in multi-channel applications or in applications where full-scale range adjustment is required.

The ADS5221 employs digital error correction techniques to enable excellent differential linearity for demanding imaging applications. Its low distortion and high SNR give the extra margin needed for medical imaging, communications, video, and test instrumentation. The ADS5221 offers power dissipation of 285mW and also provides two power-down modes.

The ADS5221 is specified at a maximum sampling frequency of 65MHz and a differential input range of 1V to 2V. The ADS5221 is available in a TQFP-48.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| AV <sub>DD</sub> , DV <sub>DD</sub> , VDRV | +3.8V                             |

|--------------------------------------------|-----------------------------------|

| Analog Input                               |                                   |

| Logic Input                                | 0.3V to (AV <sub>DD</sub> + 0.3V) |

| Case Temperature                           | +100°C                            |

| Junction Temperature                       | +150°C                            |

| Storage Temperature                        | +150°C                            |

|                                            |                                   |

NOTE: (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR |                |            | ORDERING<br>NUMBER         | TRANSPORT<br>MEDIA, QUANTITY              |

|---------|--------------|-----------------------|----------------|------------|----------------------------|-------------------------------------------|

| ADS5221 | TQFP-48      | PFB<br>"              | -40°C to +85°C | ADS5221PFB | ADS5221PFBT<br>ADS5221PFBR | Tape and Reel, 250<br>Tape and Reel, 2000 |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI website at www.ti.com.

## **ELECTRICAL CHARACTERISTICS:** AV<sub>DD</sub> = 3.3V

$T_{MIN} = -40^{\circ}C$ ,  $T_{MAX} = +85^{\circ}C$ , typical values are at  $T_{A} = +25^{\circ}C$ , sampling rate = 65MSPS, 50% clock duty cycle,  $AV_{DD} = 3.3V$ , VDRV = 2.5V, -1dBFS, internal reference voltage, and  $2V_{PP}$  differential input, unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |               | ADS5221                                                                  |                |                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                           | CONDITIONS                                                                                   | MIN           | TYP                                                                      | MAX            | UNITS                                                                   |

| RESOLUTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |               | 12 Tested                                                                |                | Bits                                                                    |

| SPECIFIED TEMPERATURE RANGE                                                                                                                                                                                                                                                                                                                                                                                                                         | Ambient Air                                                                                  |               | -40 to +85                                                               |                | °C                                                                      |

| ANALOG INPUT Single-Ended Input Range Optional Single-Ended Input Range Differential Input Range Analog Input Bias Current Input Impedance Analog Input Bandwidth                                                                                                                                                                                                                                                                                   | 2V <sub>PP</sub><br>1V <sub>PP</sub><br>2V <sub>PP</sub><br>Static, No Clock<br>–3dBFS Input | 0.5<br>1<br>1 | 1<br>1.25    5<br>300                                                    | 2.5<br>2<br>2  | V<br>V<br>V<br>μA<br>MΩ    pF<br>MHz                                    |

| CONVERSION CHARACTERISTICS Sample Rate Data Latency                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              | 1M            | 4.5                                                                      | 65M            | Samples/s<br>Clock Cycle                                                |

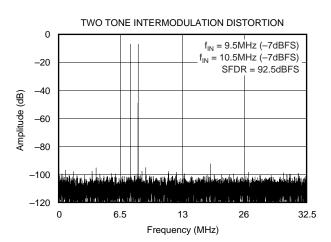

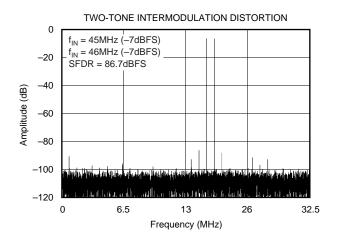

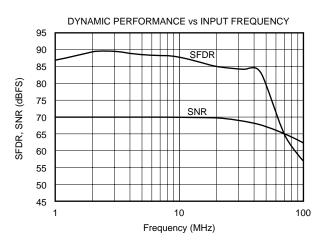

| DYNAMIC CHARACTERISTICS  Differential Linearity Error (largest code error)  f = 2.4MHz f = 9.7MHz  No Missing Codes Integral Nonlinearity Error, f = 2.4MHz  Spurious-Free Dynamic Range <sup>(1)</sup> f = 2.4MHz f = 9.7MHz f = 9.7MHz f = 32.5MHz 2-Tone Intermodulation Distortion <sup>(3)</sup> f = 9.5MHz and 10.5MHz (-7dB each tone)  Signal-to-Noise Ratio (SNR) f = 2.4MHz f = 9.7MHz f = 32.5MHz Signal-to-(Noise + Distortion) (SINAD) | Referred to Full-Scale at 25°C  Referred to Full-Scale at 25°C  Referred to Full-Scale       | 78<br>68      | ±0.3<br>±0.5<br>Tested<br>±0.5<br>90<br>88<br>85<br>92<br>70<br>70<br>69 | ±0.75<br>±1.75 | LSB<br>LSBs<br>LSBs<br>dBFS(2)<br>dBFS<br>dBFS<br>dBFS                  |

| f = 2.4MHz f = 9.7MHz f = 32.5MHz Effective Number of Bits <sup>(4)</sup> , f = 2.4MHz Output Noise Aperture Delay Time Aperture Jitter Over-Voltage Recovery Time Full-Scale Step Acquisition Time                                                                                                                                                                                                                                                 | at 25°C  Input Tied to Common-Mode                                                           | 67            | 70<br>70<br>68<br>11.2<br>0.2<br>3.0<br>1.2<br>1.0                       |                | dB<br>dB<br>dB<br>Bits<br>LSBs rms<br>ns<br>ps rms<br>Clock Cycle<br>ns |

# ELECTRICAL CHARACTERISTICS: $AV_{DD} = 3.3V$ (Cont.)

$T_{MIN} = -40^{\circ}C$ ,  $T_{MAX} = +85^{\circ}C$ , typical values are at  $T_{A} = +25^{\circ}C$ , sampling rate = 65MSPS, 50% clock duty cycle,  $AV_{DD} = 3.3V$ , VDRV = 2.5V, -1dBFS, internal reference voltage, and  $2V_{PP}$  differential input, unless otherwise noted.

|                                                                                                                                                                                                                                                                                |                                                                                                   |               | ADS5221                                                      |                     |                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------|---------------------|--------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                      | CONDITIONS                                                                                        | MIN TYP       |                                                              | MAX                 | UNITS                                |

| DIGITAL INPUTS Logic Family Convert Command High Level Input Current <sup>(5)</sup> (V <sub>IN</sub> = 3V <sub>DD</sub> ) Low Level Input Current (V <sub>IN</sub> = 0V) High Level Input Voltage Low Level Input Voltage Input Capacitance                                    | Start Conversion                                                                                  | Risiı<br>+1.7 | CMOS-Compatibng Edge of Conve                                |                     | μΑ<br>μΑ<br>V<br>V<br>pF             |

| DIGITAL OUTPUTS Logic Family Logic Coding Low Output Voltage ( $I_{OL} = 50\mu A$ to 1.5mA) High Output Voltage ( $I_{OH} = 50\mu A$ to 0.5mA) 3-State Enable Time 3-State Disable Time Output Capacitance                                                                     | VDRV = 2.5V<br><u>OE</u> = H<br><u>OE</u> = L                                                     | Stra<br>+2.4  | CMOS-Compatible ight Offset Binary of 20 2 5                 |                     | V<br>V<br>ns<br>ns                   |

| ACCURACY (Internal Reference, 2V <sub>PP</sub> , Unless Otherwise Noted)  Zero Error (referred to midscale)  Zero Error Drift (referred to midscale)  Gain Error <sup>(6)</sup> Gain Error Drift <sup>(6)</sup> Power-Supply Rejection of Gain                                 | $f_{\text{IN}}$ = 2.4MHz, at 25°C $f_{\text{IN}}$ = 9.7MHz, at 25°C $\Delta AV_{\text{DD}}$ = ±5% |               | ±0.5<br>5<br>±0.4<br>38<br>56                                | ±1.5                | %FS<br>ppm/°C<br>%FS<br>ppm/°C<br>dB |

| INTERNAL VOLTAGE REFERENCE Output Voltage Error (1V) Load Regulation at 1.0mA Output Voltage Error (0.5V) Load Regulation at 0.5mA                                                                                                                                             |                                                                                                   |               | ±5<br>0.8<br>±2.5<br>0.1                                     | ±35                 | mV<br>mV<br>mV                       |

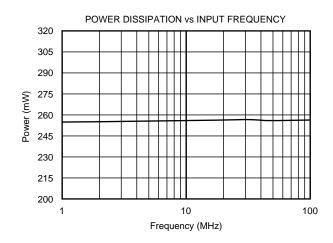

| POWER-SUPPLY REQUIREMENTS Supply Voltage: AV <sub>DD</sub> , DV <sub>DD</sub> Driver Supply Voltage: VDRV Supply Current: +I <sub>S</sub> Power Dissipation: VDRV = 2.5V VDRV = 3.3V Standard Power-Down Quasi Power-Down Thermal Resistance, $\theta_{\rm JA}$ TQFP-48 QFN-48 | Operating Operating (External Reference)                                                          | +3.0<br>+2.3  | +3.3<br>+2.5<br>86<br>285<br>290<br>15<br>70<br>63.7<br>26.1 | +3.6<br>+3.6<br>295 | V<br>V<br>mA<br>mW<br>mW<br>mW       |

NOTES: (1) Spurious-Free Dynamic Range refers to the magnitude of the largest harmonic.

- (2) dBFS means dB relative to Full-Scale.

- (3) 2-tone intermodulation distortion is referred to the largest fundamental tone. This number will be 6dB higher if it is referred to the magnitude of the 2-tone fundamental envelope.

- (4) Effective Number of Bits (ENOB) is defined by (SINAD 1.76)/6.02.

- (5) A  $50k\Omega$  pull-down resistor is inserted internally on the  $\overline{\text{OE}}$  pin.

- (6) Includes internal reference.

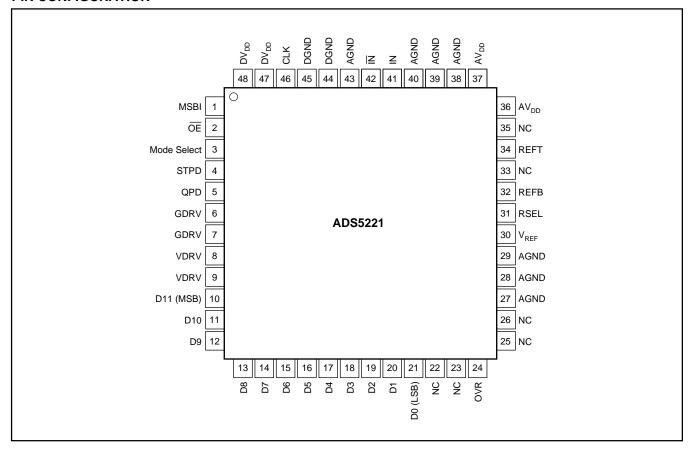

#### **PIN CONFIGURATION**

#### **PIN ASSIGNMENTS**

| PIN | I/O | NAME        | DESCRIPTION                                                | PIN | I/O | NAME             | DESCRIPTION                            |

|-----|-----|-------------|------------------------------------------------------------|-----|-----|------------------|----------------------------------------|

| 1   |     | MSBI        | Most Significant Bit Invert (HI = Binary Two's             | 25  |     | NC               | No Internal Connection                 |

|     |     |             | Complement, LO = Straight Offset Binary)                   | 26  |     | NC               | No Internal Connection                 |

| 2   |     | ŌĒ          | Tri-State (LO = Enabled, HI = Tri-State)                   | 27  |     | AGND             | Analog Ground                          |

| 3   |     | Mode Select | Duty Cycle Adjust (HI = Enabled,<br>LO = Normal Operation) | 28  |     | AGND             | Analog Ground                          |

| 4   |     | STPD        | Standard Power-Down (LO = Normal                           | 29  |     | AGND             | Analog Ground                          |

| -   |     | 011 0       | Operation, HI = Enabled)                                   | 30  |     | $V_{REF}$        | Internal Reference Voltage             |

| 5   |     | QPD         | Quasi Power-Down (LO = Normal Operation,                   |     |     |                  | (1/2V Reference)                       |

|     |     |             | HI = Enabled)                                              | 31  |     | RSEL             | Reference Mode Select (see Table I for |

| 6   |     | GDRV        | Output Driver Ground                                       |     |     |                  | settings)                              |

| 7   |     | GDRV        | Output Driver Ground                                       | 32  |     | REFB             | Bottom Reference Bypass                |

| 8   |     | VDRV        | Output Driver Supply                                       | 33  |     | NC               | No Internal Connection                 |

| 9   |     | VDRV        | Output Driver Supply                                       | 34  |     | REFT             | Top Reference Bypass                   |

| 10  | 0   | D11 (MSB)   | Data Bit 12                                                | 35  |     | NC               | No Internal Connection                 |

| 11  | 0   | D10         | Data Bit 11                                                | 36  |     | AV <sub>DD</sub> | Analog Supply                          |

| 12  | 0   | D9          | Data Bit 10                                                | 37  |     | AV <sub>DD</sub> | Analog Supply                          |

| 13  | 0   | D8          | Data Bit 9                                                 | 38  |     | AGND             | Analog Ground                          |

| 14  | 0   | D7          | Data Bit 8                                                 | 39  |     | AGND             | Analog Ground                          |

| 15  | 0   | D6          | Data Bit 7                                                 | 40  |     | AGND             | Analog Ground                          |

| 16  | 0   | D5          | Data Bit 6                                                 | 41  | ١.  | IN               | Analog Input                           |

| 17  | 0   | D4          | Data Bit 5                                                 | 42  | i   | I IN             | Complementary Analog Input             |

| 18  | 0   | D3          | Data Bit 4                                                 | 43  | l ' | AGND             | Analog Ground                          |

| 19  | 0   | D2          | Data Bit 3                                                 | 44  |     | DGND             | Digital Ground                         |

| 20  | 0   | D1          | Data Bit 2                                                 | 45  |     | DGND             | Digital Ground                         |

| 21  | 0   | D0 (LSB)    | Data Bit 1                                                 | 46  |     | CLK              | Convert Clock Input                    |

| 22  |     | NC          | No Internal Connection                                     | 46  | l ¦ |                  | · · · · · · · · · · · · · · · · · · ·  |

| 23  |     | NC          | No Internal Connection                                     |     |     | DV <sub>DD</sub> | Digital Supply                         |

| 24  |     | OVR         | Over-Range Indicator                                       | 48  | l l | DV <sub>DD</sub> | Digital Supply                         |

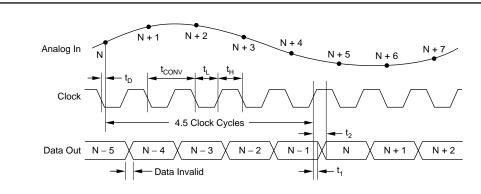

### **TIMING DIAGRAM**

| SYMBOL            | DESCRIPTION                               | MIN  | TYP | MAX  | UNITS |

|-------------------|-------------------------------------------|------|-----|------|-------|

| t <sub>CONV</sub> | Convert Clock Period                      | 15.4 |     | 1000 | ns    |

| t                 | Clock Pulse LOW                           | 6.7  | 7.7 |      | ns    |

| t <sub>H</sub>    | Clock Pulse HIGH                          | 6.7  | 7.7 |      | ns    |

| t <sub>D</sub>    | Aperture Delay                            |      | 3   |      | ns    |

| t <sub>1</sub>    | New Data Delay Time, C <sub>L</sub> = 0pF | 3.9  |     |      | ns    |

| t <sub>2</sub>    | New Data Delay Time, $C_L = 5pF$ max      |      |     | 6.5  | ns    |

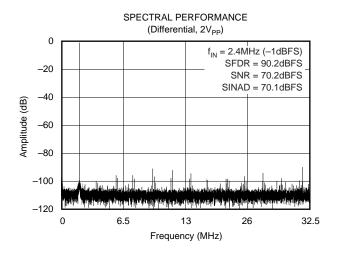

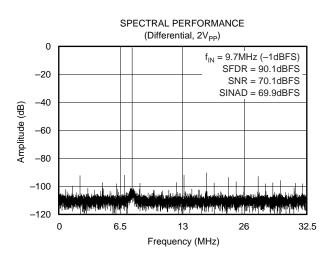

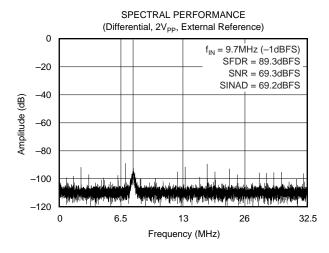

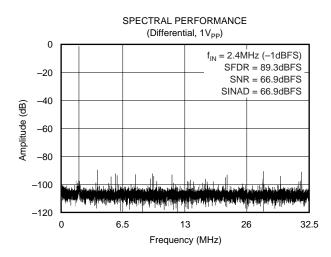

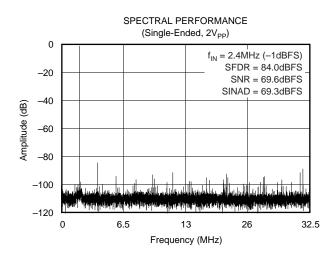

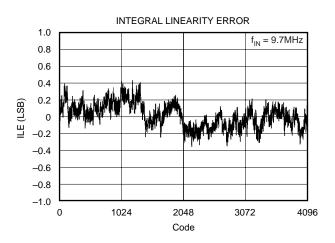

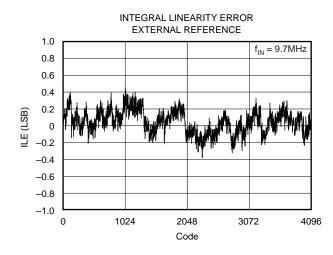

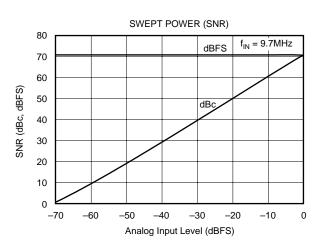

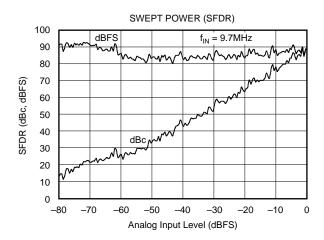

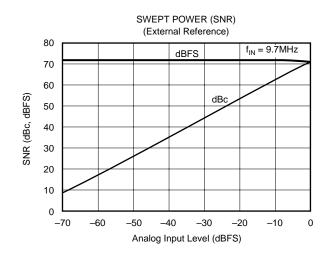

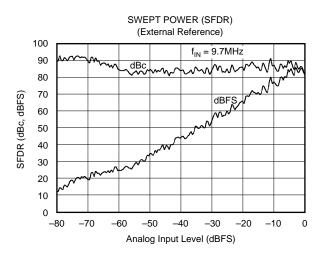

# TYPICAL CHARACTERISTICS: AV<sub>DD</sub> = 3.3V

$T_{MIN} = -40^{\circ}C$ ,  $T_{MAX} = +85^{\circ}C$ , typical values are at  $T_{A} = +25^{\circ}C$ , sampling rate = 65MSPS, 50% clock duty cycle,  $AV_{DD} = 3.3V$ , VDRV = 2.5V, -1dBFS, internal reference voltage, and  $2V_{PP}$  differential input, unless otherwise noted.

# TYPICAL CHARACTERISTICS: AV<sub>DD</sub> = 3.3V (Cont.)

$T_{MIN} = -40^{\circ}C$ ,  $T_{MAX} = +85^{\circ}C$ , typical values are at  $T_{A} = +25^{\circ}C$ , sampling rate = 65MSPS, 50% clock duty cycle,  $AV_{DD} = 3.3V$ , VDRV = 2.5V, -1dBFS, internal reference voltage, and  $2V_{PP}$  differential input, unless otherwise noted.

# TYPICAL CHARACTERISTICS: AV<sub>DD</sub> = 3.3V (Cont.)

$T_{MIN} = -40^{\circ}C$ ,  $T_{MAX} = +85^{\circ}C$ , typical values are at  $T_A = +25^{\circ}C$ , sampling rate = 65MSPS, 50% clock duty cycle,  $AV_{DD} = 3.3V$ , VDRV = 2.5V, -1dBFS, internal reference voltage, and  $2V_{PP}$  differential input, unless otherwise noted.

### APPLICATION INFORMATION

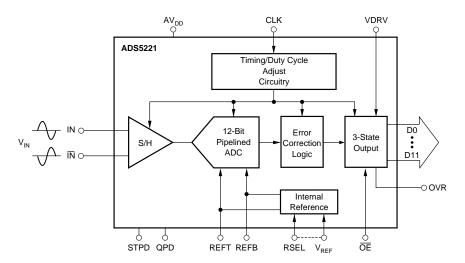

#### THEORY OF OPERATION

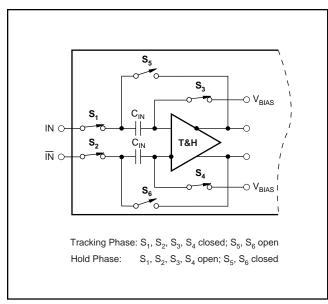

The ADS5221 is a 12-bit, 65MSPS, CMOS ADC designed with a fully differential pipeline architecture. The pipeline consists of three sections: a 3-bit quantizer, seven stages with a 1.5-bit quantizer for each stage, and a 4-bit flash. The output of each pipeline stage is processed and formed into 12-bit data in the digital error correction logic section to ensure good differential linearity of the ADC. The converter includes a high bandwidth track-and-hold amplifier in the input stage as shown in Figure 1. It provides excellent performance for a single-ended input or differential input of IF (Intermediate Frequency) or an under-sampling signal. The falling edge of the input clock initiates the conversion process. Once the signal is captured by the input track-and-hold, the bits are sequentially encoded starting with the Most Significant Bit (MSB). This process results in a data latency of 4.5 clock cycles. The ADS5221 includes a high accuracy internal reference and also allows the use of an external reference. The input full-scale range is up to +2V and is selectable based on the reference voltage setting. For normal operation, both analog inputs (IN, IN) require external common-mode voltage as signal swing center. The output data of ADS5221 are available as a 12-bit parallel word either coded in a Straight Offset Binary or Binary Two's Complement format. The ADS5221 includes an option of a duty cycle stabilizer (DCS) that allows ADS5221 to operate with a non-square wave input clock, such as from a 30% to 70% duty cycle. When the DCS is selected the ADS5221 maintains an internal clock duty cycle at 50% with ±5% tolerance. The ADS5221 has low power dissipation in normal mode and has two power down modes for energy saving. The device operates from a single +3.3V power supply and has a separate digital output driver supply pin.

FIGURE 1. Simplified Circuit of Input Track-and-Hold Amplifier of ADS5221.

#### **ANALOG INPUT**

Depending on the application and the desired level of performance, the analog input of the ADS5221 can be configured in various ways and driven with different circuits. The ADS5221 is particularly well-suited for communication systems that digitize large scale and wideband signals. In any case, the analog interface requirements should be carefully examined before selecting the appropriate circuit configuration. The circuit definition should include considerations on the input frequency band and amplitude, as well as the available power supplies.

#### **INPUT IMPEDANCE**

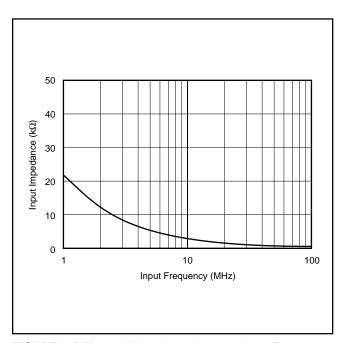

The input impedance of the ADS5221 is capacitive due to the input stray and sampling capacitors. These capacitors effectively result in a dynamic input impedance that is a function of the sampling and input frequency. Figure 2 depicts the differential input impedance of the ADS5221 as a function of the signal input frequency. At certain sampling rates, increasing the signal frequency will decrease the input impedance. This factor needs to be considered when the signal source is designed. For applications that use op amps to drive the ADC, it is recommended that a series resistor be added between the amplifier output and the converter inputs. This will isolate the capacitive input of the converter from the driving source and avoid gain peaking, or instability; furthermore, it will create a 1st-order, low-pass filter (LPF) in conjunction with the specified input capacitance of the ADS5221. The cutoff frequency of this LPF can be further adjusted by adding an external shunt capacitor from each signal input to ground. In any case, the use of the RC network is optional, but optimizing the values to adapt to the specific application is encouraged.

FIGURE 2. Differential Input Impedance vs Input Frequency.

#### INPUT COMMON-MODE VOLTAGE

The ADS5221 operates from a single +3.3V supply, and requires a external common-mode voltage. This allows a symmetrical signal swing while maintaining sufficient headroom to the supply rail. The common-mode voltage can be from an external DC voltage source, for example, an analog +3.3V supply with a simple resister divider, or from the input signal source with DC-coupling. When it is a single-ended input configuration, the common-mode voltage is typically +1.25V. When the input configuration is differential, the common-mode voltage is +1.5V.

#### **INPUT FULL-SCALE RANGE**

The input full-scale range (FSR) of the ADS5221 is selectable from +1V to +2V and any value within this range, by setting the reference select pin RSEL and reference voltage pin  $V_{REF}$  (see Table I). The input FSR (differential) is always twice  $V_{REF}$  (the voltage at the  $V_{REF}$  pin) for all reference modes.

By choosing different signal input ranges, trade-offs can be made between noise and distortion performance. For maximizing SNR, the maximum signal input  $2V_{PP}$  range may be selected. This range may also be selected for low-level (-6dBFS to -40dBFS) but high-frequency multi-tone input. The signal distortion at the output of the device could be sensitive to the input signal with large full-scale. Reducing signal amplitude will improve the distortion performance. The large input signal amplitude of the converter will impose additional design constraints to the op amp due to its headroom requirements when the op amp is from single-supply and DC-coupling.

#### **DIFFERENTIAL INPUTS**

The ADS5221 input structure is designed to accept both a single-end or differential analog signal. Distortion performance, however, can be improved by utilizing the differential input configuration. Differential operation of the ADS5221 requires that an input signal at the inputs (IN,  $\overline{\text{IN}}$ ) has the same amplitude and is 180 degrees out-of-phase. Differential signals offer a number of advantages:

- The signal amplitude is half that required for the singleended operation, and is therefore less demanding to achieve, while maintaining good linearity performance from the signal source.

- The reduced signal swing allows for more headroom of the interface circuitry, and therefore also allows a wider selection of the best suitable driver amplifier.

- · Minimization of even-order harmonics.

- Improved noise immunity based on the common-mode input rejection of the converter.

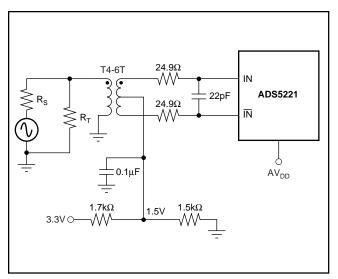

#### ANALOG INPUT DRIVEN BY TRANSFORMER

The ADS5221 can be driven by a transformer, which provides signal AC-coupling and allows a signal conversion from single-ended input to differential output, or from single-ended input to single-ended output. Using a transformer offers a number of advantages. As a passive component, it does not add to the total noise and has better harmonics in wide frequency bands, compared to an op amp driver. By using a step-up transformer, further signal amplification can be realized; as a result, the signal swing from the source can be reduced. For transformer selection, it is important to carefully examine the application requirements and determine the correct model, the desired impedance ratio, and frequency characteristics. Furthermore, the appropriate model must support the targeted distortion level and should not exhibit any core saturation at full-scale voltage levels. A variety of miniature RF transformers from different manufacturers (such as Mini-Circuits, Coilcraft, or Trak) can be selected.

Figure 3 shows a transformer-coupled input configuration of the ADS5221. The ADS5221 receives a differential AC signal from the output of the transformer and common-mode voltage of +1.5V from the center tap. A source termination resistor,  $R_{\rm T}$ , is required, which can be placed at the input or output of the transformer to satisfy the termination requirements of the source impedance,  $R_{\rm S}$ . The circuit also shows the use of an additional RC low-pass filter placed in series with each converter input to attenuate some of the wideband noise. The resistor values are typically in the range of  $10\Omega$  to  $50\Omega$ , and capacitors are in the range of  $10{\rm pF}$  to  $100{\rm pF}$  for individual application requirements.

FIGURE 3. Transformer-Coupled Differential Input Configuration of ADS5221.

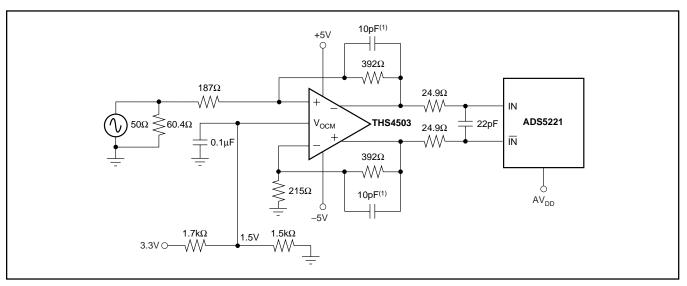

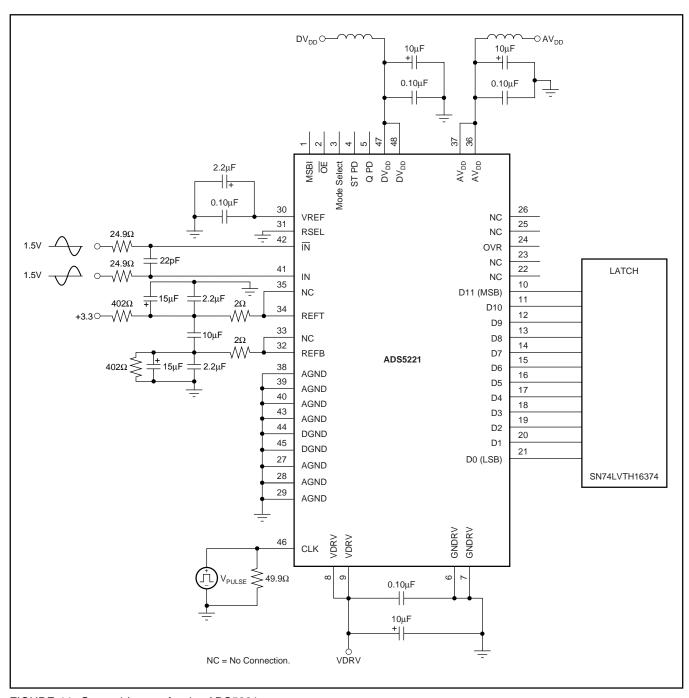

#### ANALOG INPUT DRIVEN BY OP AMPLIFIER

The ADS5221 can be driven by an operational amplifier with DC or AC signal coupling, as shown in Figure 4 and Figure 5. In Figure 4, the THS4503, a differential amplifier, is used to convert a single-ended input to differential output with a gain of 2. The THS4503 provides an output common-mode voltage set by the  $V_{\mbox{\scriptsize OCM}}$  pin, and is DC-coupled to the input of ADS5221. A low-pass filter can be created by adding small capacitors (for example, 10pF) in parallel with the feedback resistors of the THS4503 as needed for some applications. Due to the THS4503 driving a capacitive load, small series resistors in the output ensure stable operation. Further details of this and other functions of the THS4503 may be found in its product datasheet, located on the Texas Instruments web site (www.ti.com). In general, differential amplifiers provide a higher performance driver solution as compared to a single-ended amplifier.

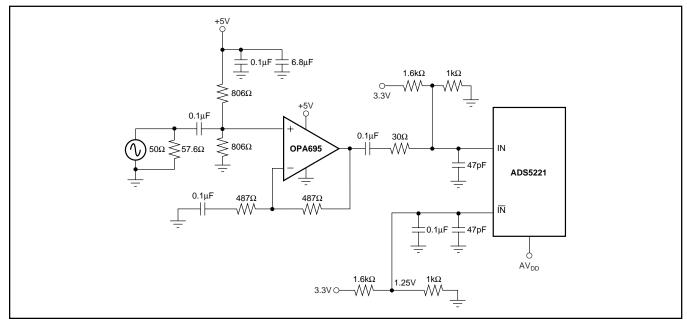

As shown in Figure 5, an AC-coupled, single-ended input configuration is realized with TI's OPA695 for wideband applications. For narrowband applications, the OPA2822 can be used. In Figure 5, the OPA695 is configured at single supply +5V and noninverting operation. The AC gain of the amplifier is 2 and the DC offset of the amplifier is +2.5V, set by the voltage divider from the op amp power supply. The output of the amplifier can provide maximum full-scale voltage range for the ADS5221. The OPA695 is a very high bandwidth, current-feedback op amp that combines 4200V/ μs slew rate and low input voltage noise. It is optimized for high gain operation. Further details of the OPA695 can be found in the OPA695 data sheet. The common-mode voltage at the ADS5221 input is +1.25V, set by a voltage divider from +3.3V power supply. The +3.3V power supply must be decoupled, as shown in Figure 11.

FIGURE 4. Using the THS4503 Differential Amplifier (Gain = 2) to Drive the ADS5221 in a DC-Coupled Configuration.

FIGURE 5. Single-Ended Input of ADS5221 Driven by OPA695 with Gain = 2.

#### **CLOCK INPUT**

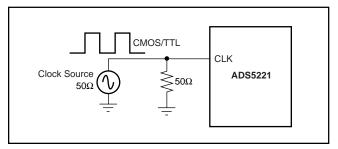

The clock input of the ADS5221 is designed to receive a single-ended pulse clock with CMOS/TTL level and DC-coupling. There is no external common-mode voltage requirement at the clock input pin (see Figure 6). The typical tolerance of the internal clock duty cycle is  $\pm 5\%$  at its nominal value of 50% in order to maintain the high performance of the device.

The ADS5221 contains an optional clock duty cycle adjust (DCA). When the DCA is enabled (Mode Select = high), a wide range of input clock duty cycle can be adjusted internally to 50% ( $\pm$ 5% tolerance) by correcting the non-sampling edge of the clock. In this case, the noise and distortion performance will not be affected by the input clock duty cycle within this range. When the DCA is disabled (Mode Select = low), a clock duty cycle variation greater than  $\pm$ 5% will degrade the dynamic performance of the device. In this case, an input clock duty cycle less than 45% will automatically request a reduction in the sampling rate in order to maintain the track/hold period within the specified values for stable performance. The DCA disabled mode is suitable for non-uniform sampling ADC applications.

FIGURE 6. General Input Clock Interface of ADS5221.

In any case, a very low jitter clock is fundamental to preserving the excellent AC performance of the ADS5221. The device itself is specified for a low jitter, characterizing the outstanding capability of the internal clock and track-and-hold circuitry. Generally, as input frequency increases, clock jitter becomes more critical to maintain a good signal-to-noise ratio. The following equation can be used to calculate the achievable SNR for a given input frequency and clock jitter ( $t_{JA}$  in ps rms):

SNR = 20 log

$$[1/(2 \cdot \pi \cdot f_{IN} \cdot t_{IA})]$$

Here, the  $t_{JA}$  is the rms aperture jitter from all jitter sources, such as clock edge, input signal and the device. The  $f_{IN}$  is input frequency. The crystal oscillator has very low jitter, but if using a clock conditioning circuit (gate, divider, logic lever converter, and so forth), an extra jitter and timing variation must be limited. In addition, the input clock is treated as an analog signal and its power supply should be separated from the power supply of the digital output driver to limit the digital noise.

#### MINIMUM SAMPLING RATE

The pipeline architecture of the ADS5221 uses a switched-capacitor technique in its internal track-and-hold stages. The high sampling speed necessitates the use of very small capacitor values. In order to hold the droop errors low, the capacitors require a minimum refresh rate. To maintain accuracy of the acquired sample charge, the sampling clock on the ADS5221 must not drop below the specified minimum of 1MHz.

#### REFERENCE

ADS5221 provides both internal reference and external reference modes by setting pins RSEL and V<sub>REF</sub> (see Table 1). The input full-scale range (FSR) of ADS5221 is always twice the voltage V<sub>REF</sub> at the V<sub>REF</sub> pin. The REFT and REFB are internally buffered, and drive the ADC core for both the external reference and internal reference modes. The REFT and REFB are designed for external bypass only. The output resistance between the REFT and REFB pins is approximately  $1\Omega$ . When the internal reference mode is selected the voltage at V<sub>REF</sub> is generated by an internal 0.5V bandgap voltage through a V<sub>REF</sub> amplifier, and the V<sub>REF</sub> output can supply 2.5mA source current. When the external reference is selected, the internal V<sub>REF</sub> amplifier is powered down, the external reference voltage is added at the V<sub>REF</sub> pin, and the voltage is input to the internal REFT/REFB amplifier. The voltage at pins REFT, REFB and V<sub>REF</sub>, the full scale range (FSR) voltage at analog input for both external and internal reference modes, and the differential/single-ended input configurations are as follows:

$$V_{REFT} = V_{REF}/2 + 1.5V$$

$V_{REFB} = 1.5V - V_{REF}/2$

$V_{REF} = V_{REFT} - V_{REFB}$

FSR (Differential) = 2 •  $V_{REF}$

| SELECTED MODE    | RSEL PIN<br>CONNECT TO                    | V <sub>REF</sub> PIN (V)                  | INPUT FSR (V)<br>(Differential) | REFT (V)                  | REFB (V)                  |

|------------------|-------------------------------------------|-------------------------------------------|---------------------------------|---------------------------|---------------------------|

| Internal Fixed   | GND to 0.2V                               | 1.0                                       | 2                               | 2                         | 1                         |

| Internal Fixed   | V <sub>REF</sub> Pin                      | 0.5                                       | 1                               | 1.75                      | 1.25                      |

| Internal Program | 0.2V to $V_{REF}$ AV <sub>DD</sub> (3.3V) | 0.5 • (1+R <sub>2</sub> /R <sub>1</sub> ) | 2 • V <sub>REF</sub>            | V <sub>REF</sub> /2 + 1.5 | 1.5 – V <sub>REF</sub> /2 |

| External         |                                           | Ext. 0.5V to 1V                           | 2 • V <sub>REF</sub>            | V <sub>REF</sub> /2 + 1.5 | 1.5 – V <sub>REF</sub> /2 |

TABLE I. Reference Configuration.

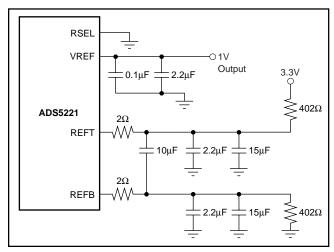

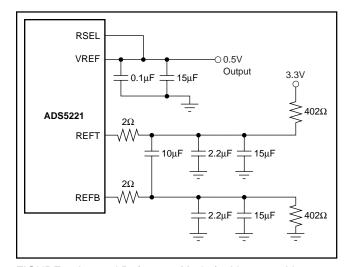

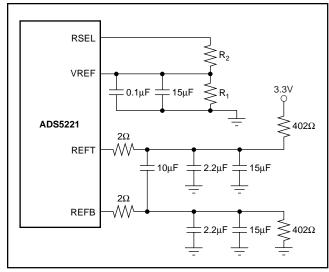

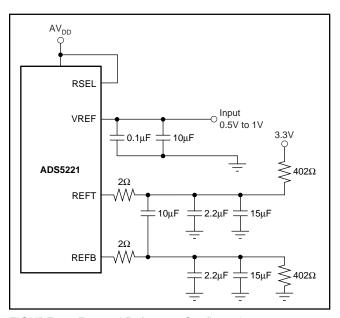

The ADS5221 requires solid bypassing for all reference pins to keep the effects of clock feedthrough to a minimum and to achieve the specified levels of performance. Figure 7 to Figure 10 show the recommended decoupling scheme. All 0.1  $\mu$ F capacitors must be located as close to the pins as possible. In addition, pins REFT,  $V_{REF}$ , and REFB must be decoupled with tantalum surface-mount capacitors (2.2  $\mu$ F, 4.7  $\mu$ F, 10  $\mu$ F or higher).

#### INTERNAL REFERENCE

There are two internal fixed reference modes and one internal programmable reference mode as shown in Table I and Figure 7 through Figure 9. Setting RSEL to ground (or <0.2V) provides an internal reference voltage of +1.0V at  $V_{REF}$  pin, +2V at REFT, and +1V at REFB pin. In this case, the input FSR is +2V peak-to-peak. Connecting RSEL to the  $V_{REF}$  pin provides an internal reference voltage of +0.5V at  $V_{REF}$ , +1.75V at REFT, and +1.25V at REFB. In this case, the input FSR is +1V peak-to-peak. Setting the resister divider as in Figure 9 provides an internal voltage between +0.5V and +1V at  $V_{REF}$ , which is as follows:

$$V_{REF} = 0.5 \cdot (1 + R_2/R_1)$$

In this case, the voltage at REFT and REFB and input FSR is calculated based on Table I.

FIGURE 7. Internal Reference Mode for  $V_{REF} = 1V$ .

FIGURE 8. Internal Reference Mode for  $V_{REF} = 0.5V$ .

FIGURE 9. Internal Reference Mode for  $V_{REF} = 0.5 \cdot (1 + R_2/R_1)$ .

#### **EXTERNAL REFERENCE**

For even more design flexibility, the ADS5221 can be operated with external references. Utilization of an external reference voltage may be considered for applications requiring higher accuracy, improved temperature stability, or flexible full-scale range. Particularly in multi-channel applications, the use of a common external reference offers the benefit of improving gain matching between converters. Setting RSEL to AV<sub>DD</sub> (+3.3V) provides an external reference mode for the ADS5221. In this case, the internal V<sub>REF</sub> amplifier is powered down, and the V<sub>REF</sub> pin requires an external reference voltage between +0.5V to +1V to provide an input FSR voltage of +1V to +2V. The REFT and REFB will appear with the voltage as shown in Table I and input FSR is always twice the voltage at the V<sub>REF</sub> pin. A voltage reference (REF1004 or TPS79225) and a single-supply amplifier (OPA2234 or OPA4227) can be used to generate a precision external reference.

FIGURE 10. External Reference Configuration.

### **DIGITAL OUTPUTS**

#### **DATA OUTPUT FORMAT**

The ADS5221 makes two data output formats available, either the Straight Offset Binary (SOB) code or the Binary Two's Complement (BTC) code. The selection of the output coding is controlled through the MSBI pin. Applying a logic high will enable the BTC coding, whereas a logic low will enable the SOB code. The two code structures are identical with one exception: the MSB is inverted for the BTC format, as shown in Table II. If the input signal exceeds the FSR, the output code will remain at all 1s or all 0s.

| DIFFERENTIAL INPUT                      | STRAIGHT OFFSET<br>BINARY (SOB) | BINARY TWO'S<br>COMPLEMENT<br>(BTC) |

|-----------------------------------------|---------------------------------|-------------------------------------|

| +FS - 1LSB<br>(+FS: VIP = 2V, VIN = 1V) | 1111 1111 1111                  | 0111 1111 1111                      |

| +1/2 FS<br>(VIP = 1.75V, VIN = 1.25V)   | 1100 0000 0000                  | 0100 0000 0000                      |

| Bipolar Zero<br>(VIP = VIN = 1.5V)      | 1000 0000 0000                  | 0000 0000 0000                      |

| -1/2 FS<br>(VIN = 1.75V, VIP = 1.25V)   | 0100 0000 0000                  | 1100 0000 0000                      |

| -FS<br>(VIN = 2V, VIP = 1V)             | 0000 0000 0000                  | 1000 0000 0000                      |

TABLE II. Coding Table for Differential Input Configuration with FSR of 2V.

#### **OUTPUT ENABLE (OE)**

The digital outputs of the ADS5221 can be set to output enable or output high impedance (tri-state) by the  $\overline{\text{OE}}$  pin. For normal operation, this pin must be at a logic low, whereas a logic high disables the outputs or sets the output tri-state.

#### **OUTPUT LOADING**

It is recommended to keep the capacitive loading on the data output lines as low as possible, preferably below 5pF. Higher capacitive loading will cause larger dynamic currents as the digital outputs are changing. These high current surges can feed back to the analog portion of the ADC and adversely affect device performance. If necessary, external buffers or latches (for example, the SN74LVTH16374) close to the converter output pins can be used to minimize capacitive loading. Buffers or latches also provide the added benefit of isolating the ADS5221 from any digital activities on the bus to limit the high-frequency noise.

#### **OVER-RANGE INDICATOR**

The ADS5221 has control functions for the input voltage over full-scale that includes output data code control and overrange indication. The output data code control of over full-scale is shown in Table II. In SOB format, for example, when

the input voltage is (+FS - 1 LSB) or above this value, the ADS5221 outputs all 1s at 12 data bits; when the input voltage is -FS or below this value, the ADS5221 outputs all Os at 12 data bits. When the input voltage is 0 (middle scale) or only the common-mode voltage at the input, the ADS5221 outputs 1 at MSB and 0s at the remaining 11 data bits. Another over-range control function of the ADS5221 is overrange indication, which is output by the OVR pin. The OVR pin is the function of the reference voltage and the output data bits, and has the same pipeline delay as the output data bits. OVR is at logic low if the input voltage is within the FSR, and is at logic high if the input voltage is over full-scale or under full-scale. OVR changes from logic low to high or logic high to low immediately following the change of the output data, when the input voltage changes from normal value to over FS or from over FS to normal value. When the input signal continues under full-scale or over full-scale, OVR stays high.

#### **TIMING**

The ADS5221 samples the analog signal at the rising edge of its input clock, and outputs the digital data at the falling edge of the input clock after a pipeline delay of 4.5 clocks. There is an aperture delay (typically 3ns) between the sampling edge and the actual sampling time. There is also a propagation delay between the rising edge of the clock and the time that data is valid on the data bus (see the timing diagram on page 5). The output data of the ADS5221 are latched data.

# POWER SUPPLIES AND POWER DISSIPATION

#### **ANALOG AND DIGITAL POWER SUPPLY**

The ADS5221 includes power-supply pins of AVDD, DVDD and VDRV. The analog supply AVDD is +3.3V and digital supply DV<sub>DD</sub> is +3.3V. A digital output driver supply, VDRV, can be +2.5V up to +3.3V. AVDD, DVDD and VDRV are not tied together internally. Each of these supply pins must be bypassed separately with at least one 0.1µF ceramic chip capacitor. The analog supply (AVDD) and the digital supply (DV<sub>DD</sub> or VDRV) may be tied together externally with a ferrite bead or inductor between the supply pins. The digital output driver supply, VDRV, of +2.5V is used commonly. It is highly recommended to consider linear supplies instead of switching types. Even with good filtering, switching supplies can radiate noise that could interfere with any high-frequency input signal and cause unwanted modulation products. The supply voltage should stay within the tolerance given in the specification table. A basic application configuration with the power supply decoupling is shown in Figure 11.

FIGURE 11. General Layout for the ADS5221.

#### **POWER DISSIPATION**

In normal operating mode (STPD = low and QPD = low), the typical total power dissipation of the ADS5221 is 285mW. The majority of the power consumption is due to biasing; therefore, this part of the total power dissipation is independent of the applied clock frequency. The digital power dissipation from the output driver is less than 10% of the total power dissipation. This portion of the power consumption is proportional to the sampling rate, digital output load and number of the bits. The current on the VDRV supply is directly related to the capacitive loading of the data output pins; care must be taken to minimize such loading.

#### **POWER DOWN (PD)**

The ADS5221 provides two power-down modes for different application requirements. One is standard power down (STPD); the second is quasi power down (QPD). Setting STPD to logic high (and QPD to logic low or high) will shut down the internal ADC core and power down the reference circuit. In this case the power dissipation is typically 15mW. With  $10\mu F$  external decoupling capacitor at REFT and REFB, it takes about  $800\mu s$  to fully restore normal operation after the normal mode is enabled. Setting QPD to logic high (and STPD to logic low) will shut down the internal ADC core and while the internal reference circuit power remains on. In this

case, power dissipation is typically 70mW. It takes about  $2\mu s$  to fully restore normal operation after the normal mode is enabled. During power-down, data in the converter pipeline will be lost and new valid data will be subject to the specified pipeline delay.

#### LAYOUT AND DECOUPLING

Proper grounding and bypassing, short lead length, and the use of ground planes are particularly important for highfrequency designs. Achieving optimum performance with a fast sampling converter like the ADS5221 requires careful attention to the printed circuit board (PCB) layout in order to minimize the effect of board parasitics and optimize component placement. A multi-layer board usually ensures best results and allows convenient component placement. The ADS5221 must be treated as an analog component, and the AV<sub>DD</sub> pins connected to a clean analog supply. This ensures the most consistent results, because digital supplies often carry a high level of switching noise that could couple into the converter and degrade the performance. The driver supply pins (VDRV) must also be connected to a low-noise supply. Supplies of adjacent digital circuits can carry substantial current transients. The supply voltage must be thoroughly filtered before connecting to the VDRV supply of the converter. All ground connections on the ADS5221 are internally bonded to the metal flag (bottom of package) that forms a large ground plane. All ground pins must directly connect to an analog ground plane that covers the PCB area under the converter. Due to its high sampling frequency, the ADS5221 generates high frequency current transients and noise (clock feedthrough) that are fed back into the supply and reference lines. If not sufficiently bypassed, this adds noise to the conversion process. See Figure 11 for the recommended supply decoupling scheme for the ADS5221. All AV<sub>DD</sub> pins should be bypassed with a combination of 0.1µF ceramic chip capacitors (0805, low ESR) and a 10µF tantalum tank capacitor. A similar approach may be used on the digital

supply pins DV<sub>DD</sub> and driver supply pins, VDRV. In order to minimize the lead and trace inductance, the capacitors must be located as close to the supply pins as possible. They are best placed directly under the package where double-sided component mounting is allowed. In addition, larger bipolar decoupling capacitors (2.2µF to 10µF), effective at lower frequencies, must also be used on the main supply pins. They can be placed on the PCB in close proximity (< 0.5 inches) to the ADC. If the analog inputs to the ADS5221 are driven differentially, it is especially important to optimize towards a highly symmetrical layout. Small trace length differences can create phase shifts compromising a good distortion performance. For this reason, the use of two single op amps rather than one dual amplifier enables a more symmetrical layout and a better match of parasitic capacitances. The pin orientation of the ADS5221 package follows a flow-through design with the analog inputs located on one side of the package, whereas the digital outputs are located on the opposite side of the quad-flat package. This provides a good physical isolation between the analog and digital connections. While designing the layout, it is important to keep the analog signal traces separated from any digital lines to prevent noise coupling onto the analog portion. Try to match trace length for the differential clock signal (if used) to avoid mismatches in propagation delays. Single-ended clock lines must be short and should not cross any other signal traces. Short circuit traces on the digital outputs will minimize capacitive loading. Trace length must be kept short to the receiving gate (< 2 inches) with only one CMOS gate connected to one digital output. If possible, the digital data outputs must be buffered (with the TI SN74LTH16374, for example). Dynamic performance can also be improved with the insertion of series resistors at each data output line. This sets a defined time constant and reduces the slew rate that would otherwise flow as the fast edge rate. The resistor value may be chosen to give a time constant of 15% to 25% of the used data.

## **Revision History**

| DATE | REVISION  | PAGE | SECTION                    | DESCRIPTION                                                             |  |  |

|------|-----------|------|----------------------------|-------------------------------------------------------------------------|--|--|

|      |           | 2    | Electrical Characteristics | Changed Data Latency from 5 to 4.5                                      |  |  |

|      |           | 5    | Timing Diagram             | Changed Clock from 5 to 4.5 clock cycles, and adjusted related symbols. |  |  |

|      |           | 5    | Tilling Diagram            | Changed timing table.                                                   |  |  |

|      |           |      |                            | Changed "eight middle stages" to "seven stages."                        |  |  |

| 5/07 | С         | 9    | Theory of Operation        | Changed "rising edge" to "falling edge."                                |  |  |

|      |           |      |                            | Changed "5 clock cycles" to "4.5 clock cycles."                         |  |  |

|      | 14 Timing |      | Timin a                    | Changed Figure 2. Corrected grid lines and X,Y axes.                    |  |  |

|      |           |      | riming                     | Changed "rising edge" to "falling edge."                                |  |  |

|      |           |      |                            | Changed "5 clocks" to "4.5 clocks."                                     |  |  |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

i.com 28-Jan-2008

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| ADS5221PFBR      | NRND                  | TQFP            | PFB                | 48   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| ADS5221PFBRG4    | NRND                  | TQFP            | PFB                | 48   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| ADS5221PFBT      | NRND                  | TQFP            | PFB                | 48   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| ADS5221PFBTG4    | NRND                  | TQFP            | PFB                | 48   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

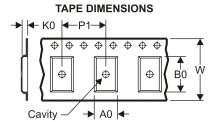

#### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

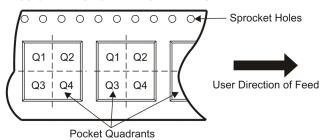

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| ADS5221PFBR | TQFP            | PFB                | 48 | 2500 | 330.0                    | 16.8                     | 9.6     | 9.6     | 1.5     | 12.0       | 16.0      | Q2               |

| ADS5221PFBT | TQFP            | PFB                | 48 | 250  | 177.8                    | 16.4                     | 9.6     | 9.6     | 1.5     | 12.0       | 16.0      | Q2               |

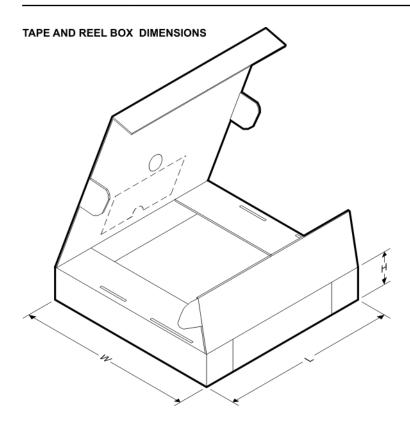

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADS5221PFBR | TQFP         | PFB             | 48   | 2500 | 346.0       | 346.0      | 33.0        |

| ADS5221PFBT | TQFP         | PFB             | 48   | 250  | 190.5       | 212.7      | 31.8        |

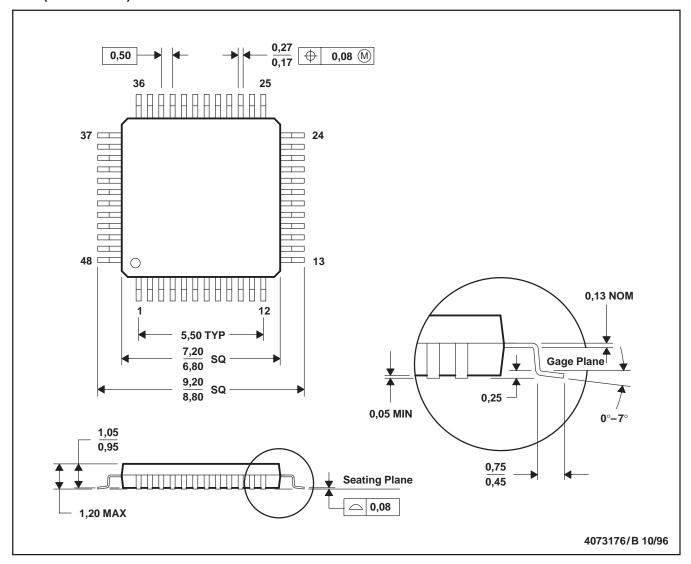

### PFB (S-PQFP-G48)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-026

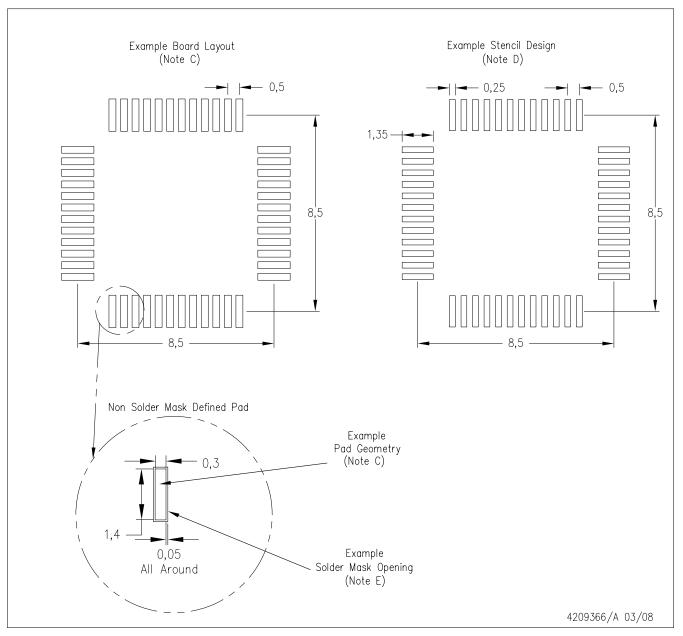

# PFB (S-PQFP-G48)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com microcontroller.ti.com Microcontrollers www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |  |  |  |  |

|--------------------|---------------------------|--|--|--|--|

| Audio              | www.ti.com/audio          |  |  |  |  |

| Automotive         | www.ti.com/automotive     |  |  |  |  |

| Broadband          | www.ti.com/broadband      |  |  |  |  |

| Digital Control    | www.ti.com/digitalcontrol |  |  |  |  |

| Medical            | www.ti.com/medical        |  |  |  |  |

| Military           | www.ti.com/military       |  |  |  |  |

| Optical Networking | www.ti.com/opticalnetwork |  |  |  |  |

| Security           | www.ti.com/security       |  |  |  |  |

| Telephony          | www.ti.com/telephony      |  |  |  |  |

| Video & Imaging    | www.ti.com/video          |  |  |  |  |

| Wireless           | www.ti.com/wireless       |  |  |  |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated