### dsPIC30F601X Rev. A3 Silicon Errata

### dsPIC30F601X (Rev. A3) Silicon Errata

The dsPIC30F601X (Rev. A3) samples you have received have been tested for an operational voltage, VDD, in the range of 4.5 to 5.5 volts. These samples were found to conform to the specifications and functionality described in the following documents:

- DS70030E dsPIC30F Programmer's Reference Manual

- DS70117B dsPIC30F6011, dsPIC30F6012, dsPIC30F6013, dsPIC30F6014 Data Sheet

- DS70119B dsPIC30F6010 Data Sheet

- DS70046B dsPIC30F Family Reference Manual

The exceptions to the specifications in the documents listed above are described in this section. The specific devices for which these exceptions are described are listed below:

- 30F6010

- 30F6011

- 30F6012

- 30F6013

- · 30F6014

The errata in this document apply to all devices marked with year codes and week codes prior to "04" and "06", respectively.

The errata described in this section will be fixed in future revisions of dsPIC30F601X silicon.

### **Silicon Errata Summary**

The following list summarizes the errata described in further detail through the remainder of this document:

1. Run-Time Self Programming (RTSP)

RTSP operations may not be performed on the Program Memory. RTSP operations can however be performed on the on-chip Data EEPROM.

2. Data EEPROM

Data EEPROM is operational below 24 MIPS.

3. Unsigned MAC

The unsigned integer mode for the MAC-type DSP instructions does not function as specified.

4. Y-Space Data Dependency

When an instruction that writes to a location in the address range of Y-data memory is immediately followed by a MAC-type DSP instruction that reads a location also resident in Y-data memory, the operations will not be performed as specified.

5. IPC2 SFR Write Sequence

A specific write sequence for IPC2 (Interrupt Priority Control 2) SFR is required.

6. Catastrophic Overflow Traps

When a catastrophic overflow of any of the accumulators causes an arithmetic (math) error trap, the Overflow status bits need to be cleared to exit the trap handler.

7. Interrupting a REPEAT Loop

When a REPEAT loop is interrupted by two or more interrupts in a nested fashion an Address Error Trap may be caused.

8. 32-bit General Purpose Timers

The 32-bit General-Purpose Timers do not function as specified for prescaler ratios other than 1:1.

9. 12-bit 100 Ksps A/D Converter

The 12-bit A/D converter scans one channel less than that specified when configured to perform channel scanning on MUX A inputs and alternately converting a fixed MUX B input simultaneously.

10. 10-bit A/D Converter - Sequential Sampling

Sampling multiple channels sequentially using any conversion trigger other than the auto-convert feature requires SAMC bits to be non-zero.

11. Data Converter Interface

In Slave mode, the DCI module does not function correctly when data communication is configured to start one serial clock after the frame synchronization pulse.

12. Quadrature Encoder Interface – Index Pulse

The Reset On Index Pulse Mode does not work.

13. Motor Control PWM - Time-base Prescaler

The Motor Control PWM Time base prescaler options – 1:4, 1:16 and 1:64 may produce unexpected results when used to generate center-aligned PWM pulses.

### 14. Motor Control PWM - Output Override

The output override function of the PWM module. controlled by the OVDCON register and the OSYNC (PWMCON2<1>) bit, produces unexpected results in certain cases when the module is used in Complementary mode.

### 15. Power-down Current, IPD

The device exhibits IPD less than 0.1 µA. However, certain workarounds are required to achieve IPD in this range.

The following sections will describe the errata and work around to these errata, where they may apply.

### 1. Module: Program Memory – RTSP

For this revision of silicon, run-time selfprogramming (RTSP) operations should not be performed on the User Program Memory and Configuration Fuse bits. Configuration Fuse bits may be programmed within the MPLAB® IDE using a device programmer, for example, MPLAB ICD 2.

Note that the on-chip Data EEPROM can be self-programmed at run-time.

### Work around

None

### Module: Data EEPROM - Speed

At device throughput greater than 24 MIPS, Table Read instructions (TBLRDL/TBLRDH) and instructions that use Program Space Visibility (PSV) do not function correctly when reading data from Data EEPROM.

### Work around

When reading data from Data EEPROM, the application should perform a clock-switch operation to lower the frequency of the system clock so that the throughput is less than 24 MIPS. This may be easily performed at any time via the Oscillator Postscaler bits, POST (OSCCON<7:6>), that allow the application to divide the system clock down by a factor of 4, 16 or 64.

### 3. Module: CPU - Unsigned MAC

The US (CORCON<12>) bit controls whether MAC-type DSP instructions operate in signed or unsigned mode. The device defaults to a signed mode on power-up (US = 0).

For this revision of silicon, MAC-type DSP instructions do not function as specified in unsigned mode (US = 1). Also, for this revision, the US bit will always read as '0'.

### Work around

Ensure that the US bit is not set by the application. order to perform unsigned integer multiplications, use the MCU Multiply instruction, MUL.UU.

### 4. Module: Y-Space Data Dependency

When an instruction that writes to a location in the address range of Y-data memory (addresses between 0x1800 and 0x27FF) is immediately followed by a MAC-type DSP instruction that reads a location also resident in Y-data memory, the two operations will not be executed as specified. This is demonstrated in Example 1.

### **EXAMPLE 1:**

| MOV                  | #0x090A, W0     | ;Load address > = ;0x900 into W0 |  |

|----------------------|-----------------|----------------------------------|--|

| VOM                  | #0x09B0, W10    | ;Load address >=                 |  |

|                      |                 | ;0x900 into W10                  |  |

| VOM                  | W2, [W0++]      | ;Perform indirect                |  |

|                      |                 | ;write via W0 to                 |  |

|                      |                 | ;address >= 0x900                |  |

| MAC                  | W4*W5, A, [W10] | +=2, W5; Perform                 |  |

|                      |                 | ;read operation                  |  |

|                      |                 | ;using Y-AGU                     |  |

| :Unexpected Results! |                 |                                  |  |

### Work around

#### Work around 1:

Insert a NOP between the two instructions as shown in Example 2.

### **EXAMPLE 2:**

| MOV      | #0x090A, W0    | ;Load address > = ;0x900 into W0 |

|----------|----------------|----------------------------------|

| VOM      | #0x09B0, W10   | ;Load address >=                 |

|          |                | ;0x900 into W10                  |

| MOV      | W2, [W0++]     | ;Perform indirect                |

|          |                | ;write via W0 to                 |

|          |                | ;address >= 0x900                |

| NOP      |                | ;No operation                    |

| MAC      | W4*W5, A, [W10 | ]+=2, W5; Perform                |

|          |                | ;read operation                  |

|          |                | ;using Y-AGU                     |

| :Correct | Results!       |                                  |

### Work around 2:

If Work around #1 is not feasible due to application real-time constraints, the user may take precautions to ensure that a write operation performed on a location in Y-data memory is not immediately followed by a DSP MAC-type instruction that performs a read operation of a location in Y-data memory.

### 5. Module: Interrupt Controller

A specific write sequence for IPC2 (Interrupt Priority Control 2) SFR is required to prevent possible data corruption in the IEC2 (Interrupt Enable Control 2) SFR. Interrupts must be disabled during this IPC2 SFR write sequence.

### Work around

An example of this write sequence is shown in Example 3.

### **EXAMPLE 3:**

```

mov #IPC2, w0 ;Point w0 to IPC2

mov #0x4444, w1 ;Write data to go to IPC2

disi #2 ;Disable interrupts for

;next two cycles

mov w1, IPC2 ;Write the data to IPC2

mov #IPC2, w0 ;Target w1 to keep IPC2

;address on bus

```

When coding in C, the write sequence shown above can be implemented using inline assembly instructions. The equivalent write sequence using the C30 compiler is shown in Example 4.

### **EXAMPLE 4:**

### 6. Module: Interrupt Controller - Traps

Catastrophic Accumulator Overflow Traps are enabled as follows:

- COVTE (INTCON1<8>) = 1

- SATA/SATB (CORCON <7/6>) = 0

A carry generated out of bit 39 in the accumulator causes a catastrophic overflow of the accumulator since the sign-bit has been destroyed. If a Math Error trap handler has been defined, the processor will vector to the Math Error trap handler upon a catastrophic overflow.

If the respective accumulator overflow status bit, OA or OB (SR<15/14>), is not cleared within the trap handler routine prior to exiting the trap handler routine, the processor will immediately re-enter the trap handler routine.

### Work around

If a Math Error Trap occurs due to a catastrophic accumulator overflow, the overflow status flags, OA and/or OB (SR<15/14>), should be cleared within the trap handler routine. Subsequently, the MATHERR (INTCON1<4>) flag bit should be cleared within the trap handler prior to executing the RETFIE instruction.

Since the OA and OB bits are read-only bits, it will be necessary to execute a dummy accumulator-based instruction within the trap service routine in order to clear these status bits. and eventually clear the MATHERR trap flag. This is shown in Example 5.

### **EXAMPLE 5:**

| .globalN   | MathErro: | r   |       |          |  |

|------------|-----------|-----|-------|----------|--|

| MathError: | BTSC      | SR, | #OA   |          |  |

|            | CLR       | Α   |       |          |  |

|            | BTSC      | SR, | #OB   |          |  |

|            | CLR       | В   |       |          |  |

|            | BCLR      | INT | CON1, | #MATHERR |  |

|            | RETFIE    |     |       |          |  |

### 7. Module: Interrupting a REPEAT Loop

When interrupt nesting is enabled (or NSTDIS(INTCON1<15>) bit is '0'), the following sequence of events will lead to an Address Error Trap:

- 1. REPEAT-loop is active

- 2. An interrupt is generated during the execution of the REPEAT-loop.

- The CPU executes the Interrupt Service Routine (ISR) of the source causing the interrupt.

- 4. Within the ISR, when the CPU is executing the first instruction cycle of the 3-cycle RETFIE (Return-from-interrupt) instruction, a second interrupt is generated by a source with a higher interrupt priority.

### Work around

Processing of Interrupt Service Routines should be disabled while the RETFIE instruction is being executed. This may be accomplished in two different ways:

Place a DISI instruction immediately before the RETFIE instruction in all interrupt service routines of interrupt sources that may be interrupted by other higher priority interrupt sources (with priority levels 1 through 6). This is shown in Example 6 in the Timer1 ISR. In this example, a DISI instruction inhibits level 1 through level 6 interrupts for 2 instruction cycles, while the RETFIE instruction is executed.

### **EXAMPLE 6:**

```

__TlInterrupt: ;Timerl ISR

PUSH W0 ;This line optional

.....

BCLR IFSO, #TlIF

POP W0 ;This line optional

DISI #1

RETFIE ;Another interrupt occurs

;here and it is processed

;correctly

```

Immediately prior to executing the RETFIE instruction, increase the CPU priority level by modifying the IPL<2:0> (SR<7:5>) bits to '111' as shown in Example 7. This will disable all interrupts between priority levels 1 through 7.

### **EXAMPLE 7:**

```

T1Interrupt:

;Timer1 ISR

WΩ

PUSH

. . . . . . .

BCLR

IFS0, #T1IF

MOV.B

#0xE0, W0

MOV.B

WREG, SR

POP

WΟ

RETFIE

;Another interrupt occurs

; here and it is processed

;correctly

```

### 8. Module: 32-bit General Purpose Timers

Pairs of 16-bit timers may be combined to form 32-bit timers. For example, Timer2 and Timer3 are combined into a single 32-bit timer. For this release of silicon, when a 32-bit timer is prescaled by ratios other than 1:1, unexpected results may occur.

### Work around

None. The application may only use the 1:1 prescaler for 32-bit timers.

### 9. Module: 12-bit 100 Ksps A/D Converter

Input Channel Scanning allows the A/D converter to acquire and convert signals on a selected set of "MUX A" input pins in sequence. This function is controlled by the CSCNA (ADCON2<11>) bit and the ADCSSL SFR.

The ALTS (ADCON2<0>) bit, when set, allows the A/D converter to alternately acquire and convert a "MUX A" input signal and a "MUX B" input signal in an interleaved fashion.

When both CSCNA and ALTS are set, the A/D module should scan MUX A input pins while alternating with a fixed MUX B input pin. However, for this release of silicon, when both features are enabled simultaneously, the last input pin enabled for channel scanning in the ADCSSL SFR, is not scanned. Thus, the A/D converter converts one channel less than the number specified in the scan sequence. Note that this erratum does not affect devices that have a 10-bit 500 Ksps A/D converter.

### Work around

The user may enable an extra ("dummy") input pin in the channel-scanning sequence. For example, if it is desirable to scan pins AN3, AN4 and AN5 on the set of MUX A inputs while interleaving conversion from AN6 on the MUX B input, the user may configure the A/D converter as follows:

- ADCON2 = 0x041D

- ADCHS = 0x0600

- ADCSSL = 0x8038

For the configuration above, AN15 is the dummy input that will not be scanned. On the A/D interrupt, the A/D buffer will contain conversions from the following pins in sequence:

- ADCBUF0 = AN3

- ADCBUF1 = AN6

- ADCBUF2 = AN4

- ADCBUF3 = AN6

- ADCBUF4 = AN5

- ADCBUF5 = AN6

- ADCBUF6 = AN3

- ADCBUF7 = AN6

## 10. Module: 10-bit A/D Converter – Sequential Samping

Sampling multiple channels sequentially using any conversion trigger source other than the auto-convert feature requires SAMC bits to be non-zero. Thus, if the following conditions are all satisfied, the module may not operate as specified:

- Multiple S/H channels are sampled sequentially

- CHPS(ADCON2<9:8>) is not equal to '00' and SIMSAM(ADCON1<3>) = 0

- Auto-convert option is not chosen as the conversion trigger

- SSRC(ADCON1<7:5>) is not equal to '111'

- SAMC(ADCON3<12:8>) is equal to '00000'

### Work around

Set the value of the SAMC bits to anything other than '00000'. The module will now operate as specified.

### 11. Module: Data Converter Interface – Slave Mode

The Data Converter Interface (DCI) module does not function correctly in Slave mode when the following conditions are true:

- The DCI module is configured to transmit/ receive one serial clock (bit clock) after the frame synchronization pulse, DJST(DCICON1<5>) = 0.

- The frame length chosen is longer than 1 word, COFSG(DCICON2<8:5>) > 0000.

### Work around

The following work around may be applied to enable DCI communication in Slave mode when it is configured to transmit one serial clock after the frame synchronization pulse is received in a multi-word frame:

- 1. Set the DJST bit to '1'.

- Enable an additional time slot immediately following each time slot intended for communication.

- Enable an additional transmit/receive buffer word (modify COFSG bits) or an additional bit per word (modify WS) for each time slot intended for communication.

- 4. Shift the data word by 1 bit to the right and load the transmit buffer word(s), such that the LS Bit of the original data word to be transmitted is loaded into the additionally enabled bit of the transmit buffer register, TXBUFn, or the MS bit of the additionally enabled transmit buffer, TXBUFn+1.

This work around is now demonstrated by an example.

Assume, the application needs the DCI module to act as a Slave transmitting 1 serial clock after the frame synchronization pulse is received. Further, assume that the application needs to transmit 16-bit data word on Time Slot 0 and the communication is over a 256\*Fs channel. In order to reduce interrupt frequency we enable all 4 transmit buffers. The DCI module SFRs should be initialized as follows before being enabled:

DCICON1 = 0x0720, DCICON2 = 0x0DEF DCICON3 = 0x0000, TSCON = RSCON = 0x0003

### **EXAMPLE 8:**

```

BCLR

SR, #C

MOV

My1stTxDataWord, W0

RRC

WO, WO

RRC

W1, W1

MOV

WO, TXBUFO

MOV

W1, TXBUF1

MOV

My2ndTxDataWord, W0

RRC

WO, WO

RRC

W1, W1

MOV

W0, TXBUF2

W1, TXBUF3

MOV

```

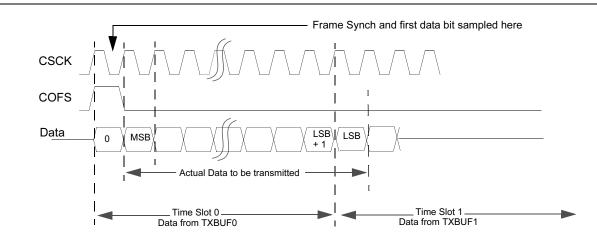

An example of loading the DCI Transmit buffers for the configuration above is shown in Example 8. A timing diagram in Figure 1 illustrates the various signals for this example. A similar rule may be applied to reading the received data from the RXBUFn SFRs.

### FIGURE 1: DCI SLAVE WORK AROUND

- **Note 1:** The Slave mode operation shown in this figure uses the DCI module's operation with DJST = 1, to create a work around for the erratum associated with the DCI module when DJST = 0.

- 2: Note that the actual data intended for transmission on time slot 0 is now straddled across two time slots time slot 0 and time slot 1. The MS bit of time slot 0 is '0'. While the MS bit of time slot 1 is actually the LS bit of the data intended for transmission.

- 3: Data loaded into TXBUF0 contains 15 MS bits of the actual 16-bit data to be transmitted, while the MS bit of TXBUF0 is cleared.

- 4: Not all serial clock pulses are shown in this timing diagram.

## 12. Module: QEI – Reset on Index Pulse Mode

For this release of silicon, the QEI module should not be operated in the Reset on Index Pulse mode.

### Work around

None

## 13. Module: Motor Control PWM – Time-base Prescalers

The input clock to the PWM time-base has prescaler options of 1:1, 1:4, 1:16 or 1:64, selected by the PTCKPS (PTCON<3:2>) control bits. In this release of silicon, the options 1:4, 1:16 and 1:64 may produce unexpected results when used to generate center-aligned PWM pulses.

### Work around

The prescaler should be set to the 1:1 option (i.e., prescaler should be disabled) in this release of silicon when generating center-aligned PWM pulses.

### 14. Module: Motor Control PWM – Output Override

The output override function of the PWM module, controlled by the OVDCON register and the OSYNC (PWMCON2<1>) bit, produces unexpected results on the output pins in certain cases when the module is used in Complementary mode. These cases are shown in Table 1. Future releases of silicon will operate as shown in the "Expected Output" columns in Table 1.

### Work around

None.

TABLE 1: OUTPUT OVERRIDE: EXPECTED VS. OBSERVED OPERATION

| OVDCON | Dead-Time | Expected Output |       | Observed Output |       | Comments                                      |

|--------|-----------|-----------------|-------|-----------------|-------|-----------------------------------------------|

|        | Enabled   | PWM1H           | PWM1L | PWM1H           | PWM1L | Comments                                      |

| 0x0100 | Yes       | Low             | PWM   | Low             | Low   | Output on PWM1L pin is shortened by dead-time |

| 0x0200 | Yes       | PWM             | Low   | Low             | Low   | Output on PWM1H pin is shortened by dead-time |

- Note 1: Other Motor Control PWM SFRs were initialized as follows: PTCON = 0x8002 and PWMCON1 = 0x0011

- 2: For these settings of OVDCON, the OSYNC (PWMCON<1>) bit should be cleared to '0' for correct eration.

- 3: Results are shown here for the PWM1H and PWM1L pins only. Similar results will be observed for any other pair of complementary output pins (PWM2H/L, PWM3H/L and PWM4H/L) and any other chosen duty cycle.

### 15. Module: IPD - Sleep Current

The device exhibits IPD of approximately 100  $\mu$ A.

### Work around

If the application does not use the on-chip A/D converter, it is possible to reduce the IPD to values below 0.1  $\mu$ A. The following additional measures need to be taken in these circumstances:

- In the application hardware, the VREF+/RA10 pin (Pin 24) on the dsPIC30F601x device should be connected to the circuit ground (GND).

- In the application software, the code sequence shown in Example 9 should be executed to bring the device into the power-saving Sleep mode.

### **EXAMPLE 9:**

```

.include "p30f6014.inc"

......

BCLR ADCON1, #ADON ;Required code

MOV #0x2000, W0 ;sequence for

MOV W0, ADCON2 ;low power-down

BCLR PMD1, #ADCMD ;current.

PWRSAV #SLEEP_MODE ;Device enters

;SLEEP mode here

```

### APPENDIX A: REVISION HISTORY

### Revision A (12/2003)

Original version of the document.

### Revision B (2/2004)

Additional silicon errata were added.

Clarifications/Corrections to dsPIC30F Family Reference Manual were removed.

### Revision C (2/2004)

Applicable devices year and week codes were updated.

### Revision D (2/2004)

Document status was changed from "Confidential" to "Advance Information".

### Revision E (4/2004)

Errata #13, "Motor Control PWM: Configuration Fuse Bits", was removed. Added Errata #10.

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2004, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### WORLDWIDE SALES AND SERVICE

### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: 480-792-7627 Web Address: http://www.microchip.com

Atlanta

3780 Mansell Road, Suite 130 Alpharetta, GA 30022 Tel: 770-640-0034 Fax: 770-640-0307

**Boston**

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Kokomo

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334

Tel: 248-538-2250 Fax: 248-538-2260

2767 S. Albright Road Kokomo, IN 46902 Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

San Jose

1300 Terra Bella Avenue Mountain View, CA 94043 Tel: 650-215-1444 Fax: 650-961-0286

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia

Suite 22, 41 Rawson Street Epping 2121, NSW Australia Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Unit 706B Wan Tai Bei Hai Bldg. No. 6 Chaoyangmen Bei Str. Beijing, 100027, China Tel: 86-10-85282100 Fax: 86-10-85282104

China - Chengdu

Rm. 2401-2402. 24th Floor. Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-86766200 Fax: 86-28-86766599

China - Fuzhou

Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521

China - Hong Kong SAR

Unit 901-6, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

China - Shanghai

Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060 China - Shenzhen

Rm. 1812, 18/F, Building A, United Plaza No. 5022 Binhe Road, Futian District

Shenzhen 518033 China Tel: 86-755-82901380 Fax: 86-755-8295-1393 China - Shunde

Room 401, Hongjian Building, No. 2 Fengxiangnan Road, Ronggui Town, Shunde

District, Foshan City, Guangdong 528303, China Tel: 86-757-28395507 Fax: 86-757-28395571

China - Qingdao

Rm. B505A, Fullhope Plaza, No. 12 Hong Kong Central Rd. Qingdao 266071, China

Tel: 86-532-5027355 Fax: 86-532-5027205

India

Divyasree Chambers 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-22290061 Fax: 91-80-22290062

Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea

168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934

Singapore 200 Middle Road #07-02 Prime Centre Singapore, 188980

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan

Kaohsiung Branch 30F - 1 No. 8 Min Chuan 2nd Road Kaohsiung 806, Taiwan Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan

Taiwan Branch 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan

Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### FUROPE

Austria

Durisolstrasse 2 A-4600 Wels Austria

Tel: 43-7242-2244-399

Fax: 43-7242-2244-393

Denmark

Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark

Tel: 45-4420-9895 Fax: 45-4420-9910

France

Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany

Steinheilstrasse 10 D-85737 Ismaning, Germany Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy

Via Quasimodo, 12 20025 Legnano (MI) Milan, Italy Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands P. A. De Biesbosch 14 NL-5152 SC Drunen, Netherlands

Tel: 31-416-690399 Fax: 31-416-690340

**United Kingdom** 505 Eskdale Road

Winnersh Triangle Wokingham

Berkshire, England RG41 5TU Tel: 44-118-921-5869 Fax: 44-118-921-5820

02/17/04