# Advanced Monolithic Systems

# **AMS682**

## INVERTING VOLTAGE DOUBLER

#### **FEATURES**

- 99.9% Voltage Conversion Efficiency

- 92% Power Conversion Efficiency

- Wide Input Voltage Range +2.4V to 5.5V

- 185µA Supply Current

- Available in SO-8 and PDIP Packages

- Only 3 external Capacitors Required

## **APPLICATIONS**

- Portable Handheld Instrumentation

- Cellular Phones

- Panel Meters

- -10V from +5V logic Supply

- -6V from a Single 3V Lithium Cell

- LCD Display Bias Generator

- Operational Amplifiers Power Supplies

#### GENERAL DESCRIPTION

The AMS682 is a CMOS charge pump converter that provides an inverted doubled output from a single positive supply. Requiring only three external capacitors for full circuit implementation the device has an on -board 12kHz (typical) oscillator which provides the clock.

Low output source impedance (typically  $140\Omega$ ), provides output current up to 10mA. The AMS682 features low quiescent current and high efficiency, making it the ideal choice for a wide variety of applications that require a negative voltage derived from a single positive supply. The compact size and minimum external parts count of the AMS682 makes it useful in many medium current, dual voltage analog power supplies.

The AMS682E is operational in the full industrial temperature range of -40°C to 85°C while AMS682C is operating over a 0°C to 70°C temperature range. The AMS682E/AMS682C are available in surface mount 8-Pin SOIC (SO-8) and 8-Pin Plastic DIP (PDIP) packages.

# **ORDERING INFORMATION:**

| PACKAGE TYPE |             | OPERATING         |

|--------------|-------------|-------------------|

| 8 LEAD SOIC  | 8 LEAD PDIP | TEMPERATURE RANGE |

| AMS682ES     | AMS682EP    | -40 to 85° C      |

| AMS682CS     | AMS682CP    | 0 to 70° C        |

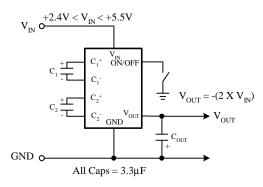

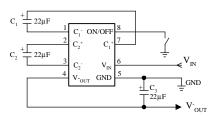

# TYPICAL OPERATING CIRCUIT

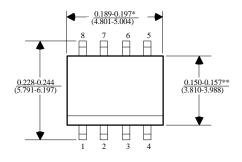

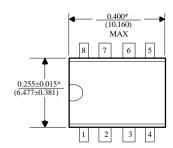

## PIN CONFIGURATIONS

# 8-LEAD DIP/ 8-LEAD SOIC

## **ABSOLUTE MAXIMUM RATINGS**

V<sub>IN</sub> +5.8V Operating Temperature Range

Power Dissipation (T<sub>A</sub> 70°C) Soldering information

Plastic DIP 730mW Lead Temperature (Soldering 10sec) +300°C

SOIC 470mW

# **ELECTRICAL CHARACTERISTICS**

Electrical Characteristics at  $V_{IN}$  =+5V and  $T_A$  = +25°C test circuit figure 1, unless otherwise specified.

| Parameter                          |                  | Conditions                         | M   | AMS682<br>in Typ M | Iax | Units |

|------------------------------------|------------------|------------------------------------|-----|--------------------|-----|-------|

| Supply Voltage Range               | V <sub>IN</sub>  | $R_L=2k\Omega$                     | 2.4 | _                  | 5.5 | V     |

| Supply Current                     | I <sub>IN</sub>  | $R_L = \infty$                     | _   | 185                | 300 | μΑ    |

|                                    |                  | $R_L = \infty$                     | _   | _                  | 400 |       |

| V <sub>OUT</sub> Source Resistance | R <sub>OUT</sub> | $\Gamma_L = 10 \text{mA}$          | _   | 140                | 180 | Ω     |

| Source Resistance                  |                  | $\Gamma_L$ =10mA                   | _   | 170                | 230 |       |

|                                    |                  | $\Gamma_L = 5mA$ , $V_{IN} = 2.8V$ | _   |                    | 320 |       |

| Oscillator Frequency               | F <sub>OSC</sub> |                                    | _   | 12                 |     | kHz   |

| Power Efficiency                   | P <sub>EFF</sub> | $R_L = 2k\Omega$                   | 90  | 92                 | _   | %     |

| Voltage Conversion Efficiency      | $V_{OUT}E_{FF}$  | $V_{OUT}R_L\!\!=\infty$            | 99  | 99.9               | _   | %     |

# PIN DESCRIPTION

| PIN NO |

|--------|

|--------|

| 8-PIN DIP/SOIC | SYMBOL      | DESCRIPTION                                          |                          |

|----------------|-------------|------------------------------------------------------|--------------------------|

| 1              | $C_1$       | Input. Capacitor C <sub>1</sub> negative terminal.   | V <sub>IN</sub><br>(+5V) |

| 2              | $C_2^+$     | Input. Capacitor $C_2$ positive terminal.            | C                        |

| 3              | $C_2^-$     | Input. Capacitor C <sub>2</sub> negative terminal    | GND                      |

| 4              | $V_{OUT}$   | Output. Negative output voltage (-2V <sub>IN</sub> ) | 0—                       |

| 5              | GND         | Input. Device ground.                                | Figur                    |

| 6              | $ m V_{IN}$ | Input. Power supply voltage.                         | 1 igui                   |

| 7              | $C_1^+$     | Input. Capacitor $C_1$ positive terminal.            |                          |

| 8              | ON/OFF      | ON/OFF Oscilator.                                    |                          |

|                |             |                                                      |                          |

Figure 1. AMS682 Test Circuit

#### DETAILED DESCRIPTION

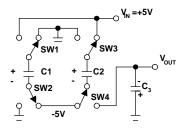

#### Phase 1

$V_{SS}$  charge storage- before this phase of the clock cycle, capacitor  $C_1$  is already charged to +5V.  $C_1^+$  is then switched to ground and the charge in  $C_1^-$  is transferred to  $C_2^-$ .

Since  $C_2^+$  is at +5V, the voltage potential across capacitor  $C_2$  is now -10V.

Figure 2. Charge Pump - Phase 1

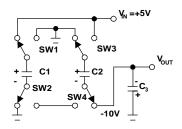

#### Phase 2

$V_{SS}$  transfer- phase two of the clock connects the negative terminal of  $C_2$  to the negative side of reservoir capacitor  $C_3$  and the positive terminal of  $C_2$  to the ground, transferring the generated -10V to  $C_3$ . Simultaneously, the positive side of capacitor  $C_1$  is switched to +5V and the negative side is connected to ground.  $C_2$  is then switched to  $V_{CC}$  and GND and Phase 1 begins again.

Figure 3. Charge Pump - Phase 2

# **MAXIMUM OPERATING LIMITS**

The AMS682 has on-chip zener diodes that clamp VIN to approximately 5.8V, and  $V_{OUT}$  to -11.6V. Exceeding the maximum supply voltage will potentially damage the chip. With an input voltage of 2V to 5.5V the AMS682 will operate over the entire operating temperature range.

#### EFFICIENCY CONSIDERATIONS

Theoretically a charge pump voltage multiplier can approach 100% efficiency under the following conditions:

- The charge pump switches have virtually no offset and are extremely low on resistance.

- Minimal power is consumed by the drive circuitry.

- The Impedances of the reservoir and pump capacitors are negligible.

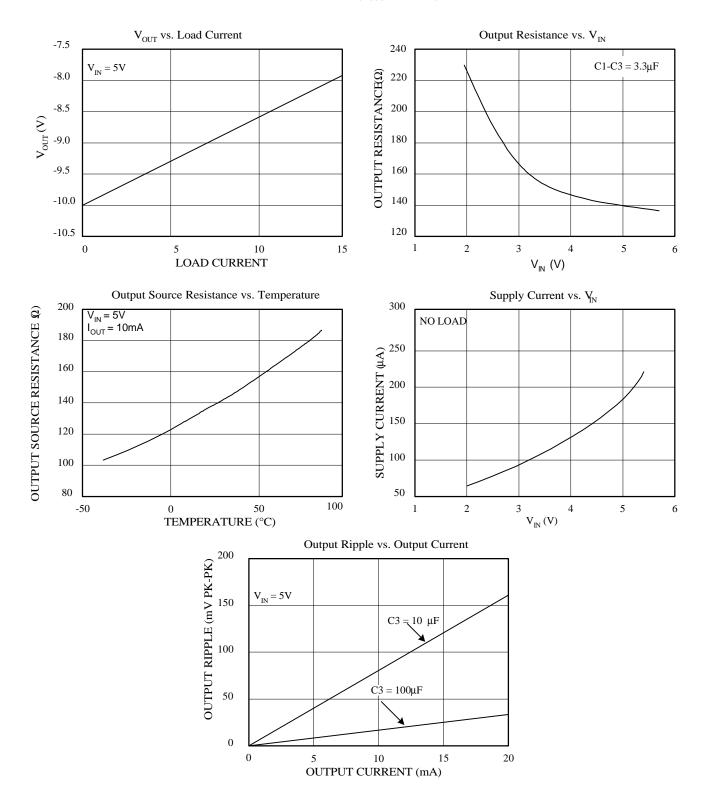

For the AMS682, efficiency is as shown below:

$$\begin{aligned} Voltage \ Efficiency &= V_{OUT} / \left( \text{-}2V_{IN} \right) \\ V_{OUT} &= \text{-}2V_{IN} + V_{DROP} \\ V_{DROP} &= \left( I_{OUT} \right) \left( R_{OUT} \right) \end{aligned}$$

Power Loss  $= I_{OUT} (V_{DROP})$

There will be a substantial voltage difference between  $V_{OUT}$  and  $2V_{IN}$  if the impedances of the pump capacitors  $C_1$  and  $C_2$  are high with respect to their respective output loads.

If the values of the reservoir capacitor  $C_3$  are larger the output ripple will be reduced. The efficiency will be improved if both pump and reservoir capacitors have larger values. ( See "Capacitor Selection" in Application Section.)

# **APPLICATIONS**

## **Negative Doubling Converter**

The AMS682 is most commonly used as a charge pump voltage converter which provides a negative output of two times a positive input voltage (Fig.4)

Figure 4. Inverting Voltage Doubler

## **APPLICATIONS** (Continued)

#### **Capacitor Selection**

The output resistance of the AMS682 is determined in part by the ESR of the capacitors used. An expression for  $R_{OUT}$  is derived as shown below:

$$\begin{split} R_{OUT} &= 2(\ R_{SW1} + R_{SW2} + ESR_{C1} + \ R_{SW3} + R_{SW4} + ESR_{C2}) \\ &+ 2(R_{SW1} + R_{SW2} + ESR_{C1} + \ R_{SW3} + R_{SW4} + ESR_{C2}) \\ &+ 1/\left(f_{PLIMP} \ X \ C1\right) + 1/\left(f_{PLIMP} \ X \ C2\right) + ESR_{C3} \end{split}$$

Assuming all switch resistances are approximately equal:

$$\begin{split} R_{OUT} &= 16~R_{SW} + 4ESR_{C1} + 4ESR_{C2} + ESR_{C3} \\ &+ 1/\left(f_{PUMP}~X~C1\right) + 1/\left(f_{PUMP}~X~C2\right) \end{split}$$

$R_{OUT}$  is typically 140 $\Omega$  at +25°C with VIN =+5V and 3.3 $\mu F$  low ESR capacitors. The fixed term (16RSW) is about 80-90 $\Omega$ . Increasing or decreasing values of C1 and C2 will affect efficiency by changing  $R_{OUT}$ .

Table 1 shows  $R_{OUT}$  for various values of C1 and C2 (assume 0.5 $\Omega$  ESR). C1 must be rated at 6VDC or greater while C2 and C3 must be rated at 12VDC or greater.

Output voltage ripple is affected by C3. Typically the larger the value of C3 the less the ripple for a given load current. The formula for p-p  $V_{\text{RIPPLE}}$  is :

$$V_{RIPPLE} = [1/[2(f_{PUMP} X C3)]+2(ESR_{C3})] (I_{OUT})$$

For a  $10\mu F$  (0.5 $\Omega$  ESR),  $f_{PUMP}=10kHz$  and  $I_{OUT}=10mA$  the peak -to-peak ripple voltage at the output will be less than 60mV. In most applications ( $I_{OUT} \leq 10mA$ ) a  $10\text{-}20\mu F$  capacitor and 1-5 $\mu F$  pump capacitors will be sufficient. Table 2 shows  $V_{RIPPLE}$  for different values of C3 (assume  $1\Omega$  ESR).

Table 1. R<sub>OUT</sub> vs. C1, C2

| C1, C2 (µF) | $\mathbf{R}_{\mathrm{OUT}}(\Omega)$ |

|-------------|-------------------------------------|

| 0.05        | 4085                                |

| 0.10        | 2084                                |

| 0.47        | 510                                 |

| 1.00        | 285                                 |

| 3.30        | 145                                 |

| 5.00        | 125                                 |

| 10.00       | 105                                 |

| 22.00       | 94                                  |

| 100.00      | 87                                  |

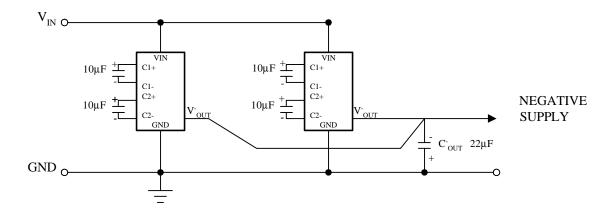

# Paralleling devices

Paralleling multiple AMS682 reduces the output resistance of the converter. The effective output resistance is the output resistance of one device divided by the number of devices. Figure 5 illustrates how each device requires separate pump capacitors  $C_1$  and  $C_2$ , but all can share a single reservoir capacitor.

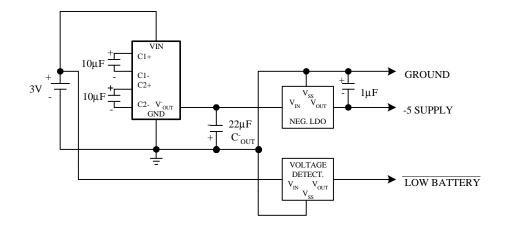

#### -5V Regulated Supply From A Single 3V Battery

Figure 6 shows a -5V power supply using one 3V battery. The AMS682 provides -6V at  $V^{\circ}_{OUT},$  which is regulated to -5V by the negative LDO. The AMS682 input can vary from 3V to 5.5V without affecting regulation significantly. A voltage detector is connected to the battery to detect undervoltage. This unit is set to detect at 2.7V. With higher input voltage, more current can be drawn from the outputs of the AMS682. With 5V at  $V_{\rm IN}$ , 10mA can be drawn from the regulated output. Assuming  $150\Omega$  source resistance for the converter, with  $I_L{=}10{\rm mA},$  the charge pump will drop 1.5V.

Table 2.  $V_{RIPPLE}$  Peak-to-Peak vs. C3 ( $I_{OUT} = 10$ mA)

| Tuble 20 Kiffle 1 can to 1 can (st ce (2001 1 cm)) |                   |  |

|----------------------------------------------------|-------------------|--|

| C3(µF)                                             | $V_{RIPPLE}$ (mV) |  |

| 0.50                                               | 1020              |  |

| 1.00                                               | 520               |  |

| 3.30                                               | 172               |  |

| 5.00                                               | 120               |  |

| 10.00                                              | 70                |  |

| 22.00                                              | 43                |  |

| 100.00                                             | 25                |  |

# APPLICATIONS (Continued)

Figure 5. Paralleling AMS682 for Lower Output Source Resistance

Figure 6. Negative Supply Derived from 3V Battery

# **TYPICAL PERFORMANCE CHARACTERISTICS** ( $F_{OSC} = 12kHz$ )

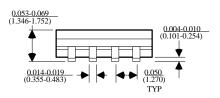

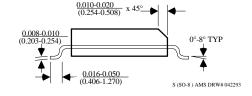

# PACKAGE DIMENSIONS inches (millimeters) unless otherwise noted.

# 8 LEAD SOIC PLASTIC PACKAGE (S)

\*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED  $0.006^\circ$  (0.152mm) PER SIDE

\*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED  $0.010^\circ$  (0.254mm) PER SIDE

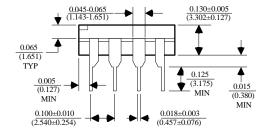

# 8 LEAD PLASTIC DIP PACKAGE (P)

\*DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTUSIONS. MOLD FLASH OR PROTUSIONS SHALL NOT EXCEED  $0.010^\circ\ (0.254\text{mm})$

P (8L PDIP) AMS DRW# 042294