# 16-Channel 12-Bit Voltage-Output DAC

# **Preliminary Technical Data**

## AD5516-1/AD5516-2/AD5516-3\*

#### **FEATURES**

High Integration: 16-channel DAC in 12x12 mm<sup>2</sup> LFBGA **Guaranteed Monotonic**

Low Power, SPI<sup>™</sup>, MICROWIRE<sup>™</sup> and DSP-Compatible

3-Wire Serial Interface Output Impedance  $0.5\Omega$

**Output Voltage Range**

± 2.5 V (AD5516-1)

± 5 V (AD5516-2)

± 10V (AD5516-3)

Asynchronous Reset facility (via RESET pin) Asynchronous Powerdown facility (via PD pin) **Daisy-Chaining Option**

Temperature Range -40°C to +85°C

#### **APPLICATIONS**

Level Setting Instrumentation **Automatic Test Equipment Optical Networks Industrial Control Systems Data Acquisition**

#### **GENERAL DESCRIPTION**

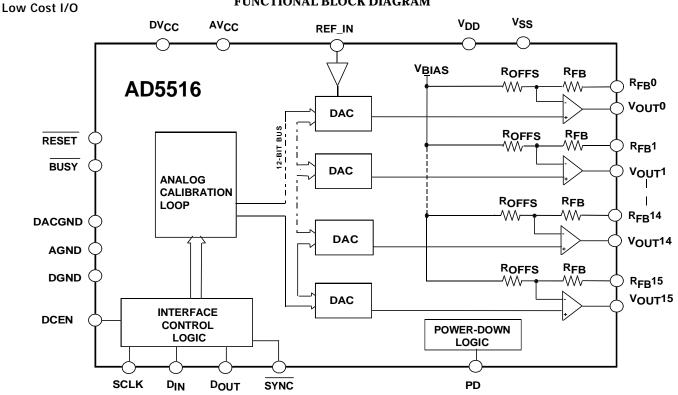

The AD5516 is a 16-channel voltage-output 12-bit DAC. The selected DAC register is written to via the 3-wire serial interface. DAC selection is accomplished via address bits A3-A0. The serial interface operates at clock rates up to 20 MHz and is compatible with standard SPI, MICROWIRE and DSP interface standards. The output voltage range is fixed at ±2.5 V (AD5516-1),  $\pm 5$  V (AD5516-2) and  $\pm 10$  V (AD5516-3). Access to the feedback resistor in each channel is provided via  $R_{FB}0$  to  $R_{BF}15$  pins.

The device is operated with AVcc =  $5 \text{ V} \pm 5\%$ , DVcc = 2.7 Vto 5.25 V,  $V_{SS} = -4.75$  V to -12 V and  $V_{DD} = 4.75$  V to 12 V and requires a stable 2.5 V reference on REF\_IN.

#### PRODUCT HIGHLIGHTS

- 1. 16 12-bit DACs in one package, guaranteed monotonic.

- 2. The AD5516 is available in a 74-lead LFBGA package with a body size of 12mm by 12mm.

#### FUNCTIONAL BLOCK DIAGRAM

\*Protected by U.S. Patent No. 5,969,657; other patents pending

SPI and QSPI are Trademarks of Motorola, Inc.

MICROWIRE is a Trademark of National Semiconductor Corporation.

REV. PrF 2/01

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. World Wide Web Site: http://www.analog.com Tel: 781/329-4700 Fax: 781/326-8703 © Analog Devices, Inc., 2000

# AD5516-1/AD5516-2/AD5516-3 SPECIFICATIONS

$(V_{DD}=4.75\ V\ to\ 12\ V,\ V_{SS}=-4.75\ V\ to\ -12\ V;\ AV_{CC}=4.75\ V\ to\ 5.25\ V;\ DV_{CC}=2.7\ V\ to\ 5.25\ V;\ AGND=DGND=DACGND=0\ V;$  REF\_IN = 2.5 V; All outputs unloaded. All specifications  $T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.)

| Parameter <sup>1</sup>                                      | A Version <sup>2</sup> | Units                  | Conditions/Comments                                    |

|-------------------------------------------------------------|------------------------|------------------------|--------------------------------------------------------|

| DAC DC PERFORMANCE                                          |                        |                        |                                                        |

| Resolution                                                  | 12                     | Bits                   |                                                        |

| Integral Nonlinearity (INL)                                 | ±2                     | LSB max                | Mode1 Operation                                        |

| Differential Nonlinearity (DNL)                             | ±1                     | LSB max                | ±0.5 LSB typ, Monotonic; Mode2                         |

| Bipolar Zero Error                                          | TBD                    | LSB max                | 20.0 LSD typ, Wonotoine, Wodes                         |

| Positive Fullscale Error                                    | TBD                    | LSB max                |                                                        |

| Negative Fullscale Error                                    | TBD                    | LSB max                |                                                        |

| Negative Fullscale Error                                    | TBD                    | LSD IIIax              |                                                        |

| VOLTAGEREFERENCE                                            |                        |                        |                                                        |

| REF_IN                                                      | 0.7                    |                        |                                                        |

| Nominal Input Voltage                                       | 2.5                    | V                      |                                                        |

| Input Voltage Range <sup>3</sup>                            | 2.375/2.625            | V min/max              |                                                        |

| Input Current                                               | ±1                     | μA max                 | < 1 nA typ                                             |

| ANALOG OUTPUTS (V <sub>OUT</sub> 0-15)                      |                        |                        |                                                        |

| Output Temperature Coefficient <sup>3,4</sup>               | 10                     | ppm/°C typ             |                                                        |

| DC Output Impedance <sup>3</sup>                            | 0.5                    | Ω typ                  |                                                        |

| Output Range <sup>5</sup>                                   |                        |                        |                                                        |

| AD5516-1                                                    | ±2.5                   | V typ                  | 100 μA output load                                     |

| AD5516-2                                                    | ±5                     | V typ                  | 100 μA output load                                     |

| AD5516-3                                                    | ±10                    | V typ                  | 100 µA output load                                     |

| Resistive Load <sup>3,6</sup>                               | 5                      | kΩ min                 | par                                                    |

| Capacitive Load <sup>3,6</sup>                              | 100                    | pF max                 |                                                        |

| Short-Circuit Current <sup>3</sup>                          | 10                     | mA typ                 |                                                        |

| DC Power-Supply Rejection Ratio <sup>3</sup>                | -70                    | dB typ                 | $V_{DD} = 10 \text{ V } \pm 5\%$                       |

| DC Fower-Supply Rejection Ratio                             | -70                    | 31                     | 1 22                                                   |

| DC Crosstalk <sup>3</sup>                                   |                        | dB typ                 | $V_{SS} = -10 \text{ V} \pm 5\%$                       |

|                                                             | 120                    | μV max                 |                                                        |

| DIGITAL INPUTS <sup>3</sup>                                 | 10                     |                        | F. A.                                                  |

| Input Current                                               | ±10                    | μA max                 | ±5 μA typ                                              |

| Input Low Voltage                                           | 0.8                    | V max                  | $DV_{CC} = 5 V \pm 5\%$                                |

|                                                             | 0.4                    | V max                  | $DV_{CC} = 3 V \pm 10\%$                               |

| Input High Voltage                                          | 2.4                    | V min                  | $DV_{CC} = 5 V \pm 5\%$                                |

|                                                             | 2.0                    | V min                  | $DV_{CC} = 3 V \pm 10\%$                               |

| Input Hysteresis (SCLK and SYNC)                            | 200                    | mV typ                 |                                                        |

| Input Capacitance                                           | 10                     | pF max                 |                                                        |

| DIGITAL OUTPUTS $(\overline{BUSY}, D_{OUT})^3$              |                        |                        |                                                        |

| Output Low Voltage, $DV_{CC} = 5V$                          | 0.4                    | V max                  | Sinking 200 μA                                         |

| Output High Voltage, $DV_{CC} = 5V$                         | 4.0                    | V min                  | Sourcing 200 µA                                        |

| Output Low Voltage, $DV_{CC} = 3V$                          | 0.4                    | V max                  | Sinking 200 μA                                         |

| Output High Voltage, $DV_{CC} = 3V$                         | 2.4                    | V min                  | Sourcing 200 μA                                        |

| High Impedance Leakage Current (D <sub>OUT</sub> only)      | ±1                     | μA max                 | DCEN = 0                                               |

| High Impedance Output Capacitance (D <sub>OUT</sub> only)   | 15                     | pF typ                 | DCEN = 0                                               |

| Power-Supply Voltages                                       |                        |                        |                                                        |

| V <sub>DD</sub>                                             | +4.75/+12              | V min/max              |                                                        |

|                                                             | -4.75/-12              | V min/max<br>V min/max |                                                        |

| $V_{SS}$                                                    | +4.75/+5.25            | V min/max              |                                                        |

| $egin{array}{l} {\sf AV_{CC}} \\ {\sf DV_{CC}} \end{array}$ |                        |                        |                                                        |

| Power-Supply Currents <sup>7</sup>                          | +2.7/+5.25             | V min/max              |                                                        |

|                                                             | 7.5                    | mA may                 | 5 mA typ. All channels Fullscale                       |

| $I_{ m DD}$                                                 |                        | mA max                 |                                                        |

| $I_{SS}$                                                    | 7.5                    | mA max                 | 5 mA typ. All channels Fullscale                       |

| AI <sub>CC</sub>                                            | 16.5                   | mA max                 | 13 mA typ                                              |

|                                                             | 1.5                    | mA max                 | 1 mA typ                                               |

| DI <sub>CC</sub> Power Dissipation <sup>7</sup>             | 115                    | mW typ                 | $V_{\rm DD} = 5  \text{V},  V_{\rm SS} = -5  \text{V}$ |

#### NOTES:

-2-REV. PrF

<sup>&</sup>lt;sup>1</sup>See Terminology

<sup>&</sup>lt;sup>2</sup>A Version: Industrial temperature range -40°C to +85°C; typical at +25°C. <sup>3</sup>Guaranteed by design and characterization, not production tested.

<sup>&</sup>lt;sup>4</sup>AD780 as reference for the AD5516.

<sup>&</sup>lt;sup>5</sup>Output range is restricted from  $V_{SS}$  + 2 V to  $V_{DD}$  - 2 V <sup>6</sup>Ensure that you do not exceed Tj(max). See Maximum ratings.

<sup>&</sup>lt;sup>7</sup>Outputs Unloaded.

Specifications subject to change without notice

### AD5516-1/AD5516-2/AD5516-3

### **AC Characteristics**

$(V_{DD}=4.75V\ to\ 12V,\ V_{SS}=-4.75V\ to\ -12V;\ AV_{CC}=4.75V\ to\ 5.25V;\ DV_{CC}=2.7V\ to\ 5.25V;\ AGND=DGND=DACGND=0V;\ REF\_IN=2.5\ V;\ All\ outputs\ unloaded.$  All specifications  $T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.)

| Parameter <sup>1,2</sup>                                                                                        | A Version <sup>3</sup> | Units                                              | Conditions/<br>Comments                                               |

|-----------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------|-----------------------------------------------------------------------|

| Output Voltage Settling Time (Mode 1) <sup>4</sup> Output Voltage Settling Time (Mode 2) <sup>4</sup> Slew Rate | 20<br>1<br>0.85        | μs max<br>μs max                                   | 100 pF, 5 k $\Omega$ Load Full Scale change 100 pF, 5 k $\Omega$ Load |

| Digital-to-Analog Glitch Impulse<br>Digital Crosstalk                                                           | 0.83<br>1<br>5         | V/μs typ<br>nV-s typ<br>nV-s typ                   | 1 LSB change around major carry                                       |

| Analog Crosstalk<br>Digital Feedthrough<br>Output Noise Spectral Density @ 1kHz                                 | 1<br>0.2<br>400        | nV-s typ<br>nV-s typ<br>nV/(Hz) <sup>1/2</sup> typ |                                                                       |

NOTES:

Specifications subject to change without notice

Timing Characteristics  $(V_{DD} = 4.75 \text{ V to } 12 \text{ V}, V_{SS} = -4.75 \text{ V to } -12 \text{ V}; \text{ AV}_{CC} = 4.75 \text{ V to } 5.25 \text{ V}; \text{ DV}_{CC} = 2.7 \text{ V to } 5.25 \text{ V}; \text{ DV}_{CC} = 2.7 \text{ V to } 5.25 \text{ V}; \text{ AGND} = DGND = DGCGND} = 0 \text{ V}; \text{ All specifications } T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted.})$

| Parameter <sup>1,2,3</sup> | Limit at $T_{MIN}$ , $T_{MAX}$ (A Version) | Units   | Conditions/Comments                                            |

|----------------------------|--------------------------------------------|---------|----------------------------------------------------------------|

| $f_{\mathrm{UPDATE1}}$     | 50                                         | kHz max | DAC Update Rate (Mode 1)                                       |

| $ m f_{UPDATE2}$           | 900                                        | kHz max | DAC Update Rate (Mode 2)                                       |

| $f_{CLKIN}$                | 20                                         | MHz max | SCLK Frequency                                                 |

| $t_1$                      | 20                                         | ns min  | SCLK High Pulse Width                                          |

| $t_2$                      | 20                                         | ns min  | SCLK Low Pulse Width                                           |

| $t_3$                      | 10                                         | ns min  | SYNC Falling Edge to SCLK Falling Edge Setup Time              |

| $t_4$                      | 5                                          | ns min  | D <sub>IN</sub> Setup Time                                     |

| $t_5$                      | 5                                          | ns min  | D <sub>IN</sub> Hold Time                                      |

| $t_6$                      | 0                                          | ns min  | SCLK Falling Edge to SYNC Rising Edge                          |

| t <sub>7</sub>             | 10                                         | ns min  | Minimum SYNC High Time (Stand-Alone Mode)                      |

| $t_{7MODE2}$               | 400                                        | ns min  | Minimum SYNC High Time (Daisy-Chain Mode)                      |

| $t_{8MODE1}$               | 10                                         | ns min  | BUSY Rising Edge to SYNC Falling Edge                          |

| $t_{9MODE2}$               | 200                                        | ns min  | 18th SCLK Falling Edge to SYNC Falling Edge (Stand-Alone Mode) |

| t <sub>10</sub>            | 10                                         | ns min  | SYNC Rising Edge to SCLK Rising Edge (Daisy-Chain Mode)        |

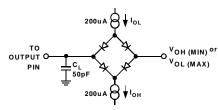

| $t_{11}^{4}$               | 20                                         | ns max  | SCLK Rising Edge to D <sub>OUT</sub> Valid (Daisy-Chain Mode)  |

| t <sub>12</sub>            | 20                                         | ns min  | RESET Pulse Width                                              |

#### NOTES

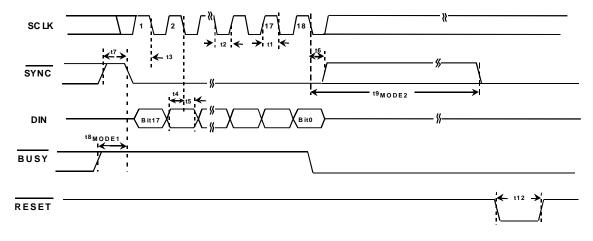

#### SERIAL INTERFACE TIMING DIAGRAMS

Figure 1. Serial Interface Timing Diagram

<sup>&</sup>lt;sup>1</sup>See Terminology

<sup>&</sup>lt;sup>2</sup>Guaranteed by design and characterization, not production tested

<sup>&</sup>lt;sup>3</sup>A version: Industrial temperature range -40°C to +85°C

<sup>&</sup>lt;sup>4</sup>Timed from the end of a write sequence

<sup>&</sup>lt;sup>1</sup>See Timing Diagrams in Figures 1 and 2.

<sup>&</sup>lt;sup>2</sup>Guaranteed by design and characterization, not production tested.

$<sup>^3</sup>$ All input signals are specified with tr = tf = 5ns (10% to 90% of DV<sub>CC</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2

<sup>&</sup>lt;sup>4</sup>This is measured with the load circuit of Figure 3.

### AD5516-1/AD5516-2/AD5516-3

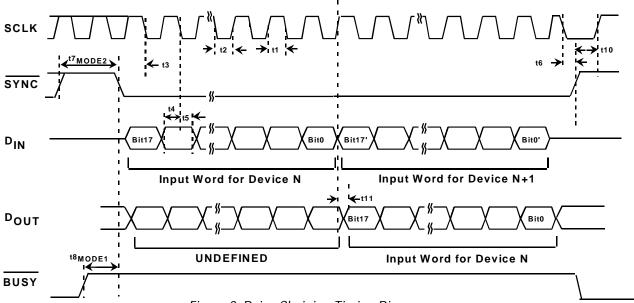

Figure 2. Daisy-Chaining Timing Diagram

Figure 3. Load Circuit for  $D_{OUT}$  Timing Specifications

#### ABSOLUTE MAXIMUM RATINGS\*

| $(T_A = +25^{\circ}C \text{ unless otherwise noted})$ |                         |

|-------------------------------------------------------|-------------------------|

| V <sub>DD</sub> to AGND                               | 0.3 V to +17 V          |

| V <sub>SS</sub> to AGND                               | +0.3 V to -17 V         |

| $AV_{CC}$ to AGND, DACGND                             | 0.3 V to +7 V           |

| DV <sub>CC</sub> to DGND                              | 0.3 V to +7 V           |

| Digital Inputs to DGND0.3                             | V to $DV_{CC} + 0.3 V$  |

| Digital Outputs to DGND0.3                            | V to $DV_{CC} + 0.3 V$  |

| REF_IN to AGND, DACGND                                | 0.3 V to +7 V           |

| $V_{OUT}0\mbox{-}15$ to AGND $V_{SS}\mbox{-}0.5$      | 3 V to $V_{DD} + 0.3 V$ |

| AGND to DGND                                          | 0.3 V to + 0.3 V        |

| Operating Temperature Range                                    |

|----------------------------------------------------------------|

| Industrial40°C to +85°C                                        |

| Storage Temperature Range65°C to +150°C                        |

| Junction Temperature (T <sub>J</sub> max)+150°C                |

| 74-lead LFBGA Package, θ <sub>JA</sub> Thermal Impedance41°C/W |

| Reflow Soldering                                               |

| Peak Temperature220°C                                          |

| Time at Peak Temperature10 sec to 40 sec                       |

| NOTES:                                                         |

<sup>1</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. <sup>2</sup>Transient currents of up to 100mA will not cause SCR latch-up

#### **ORDERING GUIDE**

| Model       | Erretion | Output<br>Voltage Spop | Package       |

|-------------|----------|------------------------|---------------|

| Model       | Function | Voltage Span           | Option        |

| AD5516ABC-1 | 16 DACs  | ±2.5 V                 | 74-lead LFBGA |

| AD5516ABC-2 | 16 DACs  | ±5 V                   | 74-lead LFBGA |

| AD5516ABC-3 | 16 DACs  | ±10 V                  | 74-lead LFBGA |

|             |          |                        |               |

#### CAUTION-

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD5516 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

## AD5516-1/AD5516-2/AD5516-3

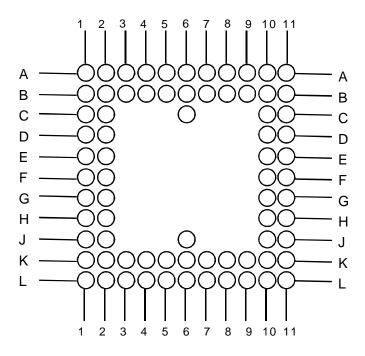

#### PIN CONFIGURATION

#### AD551674-lead LFBGA Ball Configuration

| LFBGA<br>Number | Ball<br>Name | LFBGA<br>Number | Ball<br>Name | LFBGA<br>Number | Ball<br>Name |

|-----------------|--------------|-----------------|--------------|-----------------|--------------|

| A1              | N/C          | C10             | AVCC1        | J10             | RFB12        |

| A2              | N/C          | C11             | N/C          | J11             | RFB11        |

| A3              | RESET        | D1              | RFB0         | K1              | RFB4         |

| A4              | BUSY         | D2              | DACGND       | K2              | VOUT5        |

| A5              | DGND         | D10             | AVCC2        | K3              | RFB5         |

| A6              | DVCC         | D11             | N/C          | K4              | N/C          |

| A7              | DOUT         | E1              | VOUT1        | K5              | VSS2         |

| A8              | DIN          | E2              | N/C          | K6              | VSS1         |

| A9              | SYNC         | E10             | AGND1        | K7              | VOUT10       |

| A10             | N/C          | E11             | PD           | K8              | VOUT9        |

| A11             | N/C          | F1              | VOUT2        | K9              | RFB10        |

| B1              | N/C          | F2              | RFB1         | K10             | RFB9         |

| B2              | N/C          | F10             | AGND2        | K11             | VOUT11       |

| B3              | N/C          | F11             | RFB14        | L1              | N/C          |

| B4              | DCEN         | G1              | RFB2         | L2              | VOUT6        |

| B5              | DGND         | G2              | RFB15        | L3              | RFB6         |

| B6              | DGND         | G10             | VOUT14       | L4              | VOUT7        |

| B7              | N/C          | G11             | RFB13        | L5              | N/C          |

| B8              | N/C          | H1              | VOUT3        | L6              | VDD2         |

| B9              | SCLK         | H2              | VOUT15       | L7              | VDD1         |

| B10             | N/C          | H10             | VOUT13       | L8              | RFB7         |

| B11             | REF_IN       | H11             | VOUT12       | L9              | VOUT8        |

| C1              | VOUT0        | J1              | RFB3         | L10             | RFB8         |

| C2              | DACGND       | J2              | VOUT4        | L11             | N/C          |

| <u>C6</u>       | N/C          | J6              | N/C          |                 |              |

REV. PrF –5–

## AD5516-1/AD5516-2/AD5516-3

#### PIN FUNCTION DESCRIPTION

| Pin                     | Function                                                                                                                                                                                                                                                                    |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND(1-2)               | Analog GND pins.                                                                                                                                                                                                                                                            |

| AV <sub>CC</sub> (1-2)  | Analog supply pins. Voltage range from 4.75 V to 5.25 V.                                                                                                                                                                                                                    |

| V <sub>DD</sub> (1-2)   | V <sub>DD</sub> supply pins. Voltage range from 4.75 V to 12 V.                                                                                                                                                                                                             |

| V <sub>SS</sub> (1-2)   | V <sub>SS</sub> supply pins. Voltage range from -4.75 V to -12 V.                                                                                                                                                                                                           |

| DGND                    | Digital GND pins.                                                                                                                                                                                                                                                           |

| $DV_{CC}$               | Digital supply pin. Voltage range from 2.7 V to 5.25 V.                                                                                                                                                                                                                     |

| DACGND                  | Reference GND supply for all 16 DACs.                                                                                                                                                                                                                                       |

| REF_IN                  | Reference input voltage for all 16 DACs.                                                                                                                                                                                                                                    |

| V <sub>OUT</sub> (0-15) | Analog output voltages from the 16 DAC channels.                                                                                                                                                                                                                            |

| R <sub>FB</sub> (0-15)  | Feedback Resistors. Access to the inverting inputs of the 16 output amplifiers allows remote sensing in force/sense applications. For nominal output voltage range connect each $R_{\rm FB}$ to it's                                                                        |

| SYNC                    | corresponding $V_{OUT}$ .  Active Low Input. This is the Frame Synchronisation signal for the serial interface. While $\overline{SYN}$ is low, data is transferred in on the falling edge of SCLK.                                                                          |

| SCLK                    | Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 20 MHz.                                                                                                                                        |

| $\mathrm{D_{IN}}$       | Serial Data Input. Data must be valid on the falling edge of SCLK.                                                                                                                                                                                                          |

| D <sub>OUT</sub>        | Serial Data Output. $D_{OUT}$ can be used for daisy-chaining a number of devices together or for reading back the data in the shift register for diagnostic purposes. Data is clocked out on $D_{OUT}$ on the rising edge of SCLK and is valid on the falling edge of SCLK. |

| DCEN <sup>1</sup>       | Active High Control Input. This pin is tied high to enable Daisy-Chain Mode.                                                                                                                                                                                                |

| RESET <sup>2</sup>      | Active Low Control Input. This resets all DAC registers to their mid-scale value.                                                                                                                                                                                           |

| PD <sup>1</sup>         | Active High Control Input. All DACs go into power-down mode when this pin is high. The DAC outputs go into a high-impedance state and the power dissipation drops to TBD.                                                                                                   |

| BUSY                    | Active Low Output. This signal tells the user that the analog calibration loop is active. It goes low during conversion. The duration of the pulse on $\overline{BUSY}$ determines the maximum DAC update rate, $f_{UPDATE}$ .                                              |

REV. PrF -6-

<sup>&</sup>lt;sup>1</sup>Internal Pull-down device on this logic input. Therfore it can be left floating and will default to a logic low condition.

<sup>2</sup>Internal Pull-up device on this logic input. Therfore it can be left floating and will default to a logic high condition.

### AD5516-1/AD5516-2/AD5516-3

#### **TERMINOLOGY**

#### **Integral Nonlinearity (INL)**

This is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is expressed in LSBs.

#### **Differential Nonlinearity (DNL)**

Differential Nonlinearity (DNL) is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified DNL of  $\pm 1$  LSB maximum ensures monotonicity.

#### **Bipolar Zero Error**

Bipolar zero error is the deviation of the DAC output from the ideal midscale of 0 V. It is measured with 10...00 loaded to the DAC. It is expressed in LSBs.

#### **Positive Full-Scale Error**

This is the error in the DAC output voltage with all 1s loaded to the DAC. Ideally the DAC output voltage, with all 1s loaded to the DAC registers, should be REF\_IN (AD5516-1), 2 REF\_IN (AD5516-2) and 4 REF\_IN (AD5516-3). It is expressed in LSBs.

#### **Negative Full-Scale Error**

This is the error in the DAC output voltage with all 0s loaded to the DAC. Ideally the DAC output voltage, with all 0s loaded to the DAC registers, should be -REF\_IN (AD5516-1), -2 REF\_IN (AD5516-2) and -4 REF\_IN (AD5516-3). It is expressed in LSBs.

#### **Output Temperature Coefficient**

This is a measure of the change in analog output with changes in temperature. It is expressed in ppm/°C.

#### **DC Power-Supply Rejection Ratio**

DC Power-Supply Rejection Ratio (PSRR) is a measure of the change in analog output for a change in supply voltage ( $V_{\rm DD}$  and  $V_{\rm SS}$ ). It is expressed in dBs.  $V_{\rm DD}$  and  $V_{\rm SS}$  are varied  $\pm$  5%.

#### **DC Crosstalk**

This the DC change in the output level of one DAC at midscale in response to a full-scale code change (all 0s to all 1s and vice versa) and output change of another DAC. It is expressed in  $\mu V$ .

#### **Output Settling Time**

This is the time taken from when the last data bit is clocked into the DAC until the output has settled to within  $\pm$  0.5 LSB of it's final value.

#### **Digital-to-Analog Glitch Impulse**

This is the area of the glitch injected into the analog output when the code in the DAC register changes state. It is specified as the area of the glitch in nV-secs when the digital code is changed by 1 LSB at the major carry transition (011...11 to 100...00 or 100...00 to 011...11).

#### **Digital Crosstalk**

This is the glitch impulse transferred to the output of one DAC at mid-scale while a full-scale code change (all 1s to all 0s and vice versa) is being written to another DAC. It is expressed in nV-secs.

#### **Analog Crosstalk**

This the area of the glitch transferred to the output  $(V_{OUT})$  of one DAC due to a full-scale change in the output  $(V_{OUT})$  of another DAC. The area of the glitch is expressed in nV-secs.

#### **Digital Feeedthrough**

This is a measure of the impulse injected into the analog outputs from the digital control inputs when the part is not being written to, i.e. SYNC is high. It is specified in nV-secs and is measured with a worst-case change on the digital input pins, e.g. from all 0s to all 1s and vice versa.

#### **Output Noise Spectral Density**

This is a measure of internally generated random noise. Random noise is characterized as a spectral density (voltage per root Hertz). It is measured in  $nV/(Hz)^{1/2}$ .

REV. PrF -7-

# Typical Performance Characteristics - AD5516-1/AD5516-2/AD5516-3

| TPC 1. Typical DNL plot                                       | TPC 2. Typical INL plot                  | TPC 3. INL Error and DNL Error vs.<br>Temperature     |

|---------------------------------------------------------------|------------------------------------------|-------------------------------------------------------|

| TPC 4. Bipolar Zero Error and Fullscale Error vs. Temperature | TPC 5. V <sub>OUT</sub> vs. Temperature  | TPC 6. V <sub>OUT</sub> Source and Sink<br>Capability |

| TPC 7. Full-Scale Settling Time                               | TPC 8. Exiting Powerdown to<br>Fullscale | TPC 9. Major Code Transition Glitch<br>Impulse        |

-8- REV. PrF

### AD5516-1/AD5516-2/AD5516-3

#### **FUNCTIONAL DESCRIPTION**

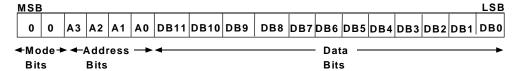

The AD5516 consists of 16 12-bit DACs in a single package. A single reference input pin (REF\_IN) is used to provide a 2.5 V reference for all 16 DACs. To update a DAC's output voltage an 18-bit word is written to the part via the 3-wire serial interface. This 18-bit word consists of 2 mode bits, 4 address bits and 12 data bits as shown in Figure 4. Once the serial write is complete the selected DAC converts the code. The output amplifiers translate the 0 - 2.5 V DAC output range to give a  $\pm 5$  V range at the output pins  $V_{\rm OUT}$ 0 to  $V_{\rm OUT}$ 15.

#### **SERIAL INTERFACE**

DCEN (Daisy-Chain Enable) determines whether the serial interface is in Daisy-Chain Mode or Stand-Alone Mode. In both modes  $\overline{\text{SYNC}}$  is an edge-triggered input that acts as a frame synchronization signal and chip enable. Data can only be transferred into the device while  $\overline{\text{SYNC}}$  is low. To start the serial data  $\overline{\text{transfer}}$ ,  $\overline{\text{SYNC}}$  should be taken low observing the minimum  $\overline{\text{SYNC}}$  falling to SCLK falling edge setup time,  $t_3$ .

#### Stand-Alone Mode (DCEN = 0)

After  $\overline{\text{SYNC}}$  goes low, serial data will be shifted into the device's input shift register on the falling edges of SCLK for 18 clock pulses. After the falling edge of the 18th SCLK pulse, data will automatically be transferred from the input shift register to the addressed DAC.

SYNC must be taken high and low again for further serial data transfer. SYNC may be taken high after the falling edge of the 18th SCLK pulse, observing the minimum SCLK falling edge to SYNC rising edge time, t<sub>6</sub>. If SYNC is taken high before the 18th falling edge of SCLK, the data transfer will be aborted and the addressed DAC will not be updated. See the timing diagram in Figure 1.

#### Daisy-Chain Mode (DCEN = 1)

In Daisy-Chain Mode the internal gating on SCLK is disabled. The SCLK is continuously applied to the input shift register when  $\overline{SYNC}$  is low. If more than 18 clock pulses are applied, the data ripples out of the shift register and appears on the  $D_{OUT}$  line. This data is clocked out on the rising edge of SCLK and is valid on the falling edge. By connecting this line to the  $D_{IN}$  input on the next device in the chain, a multi-device interface is constructed. 18 clock pulses are required for each device in the system. Therefore, the total number of clock cycles must equal 18N where N is the total number of devices in the chain. See the timing diagram in Figure 2.

When the serial transfer to all devices is complete, \$\overline{SYNC}\$ should be taken high. This prevents any further data being clocked into the input shift register. A burst clock containing the exact number of clock cycles may be used and \$\overline{SYNC}\$ taken high some time later. After the rising edge of \$\overline{SYNC}\$, data is automatically transferred from each device's input shift register to the addressed DAC.

Figure 4. Mode1 data format

REV. PrF –9–

## AD5516-1/AD5516-2/AD5516-3

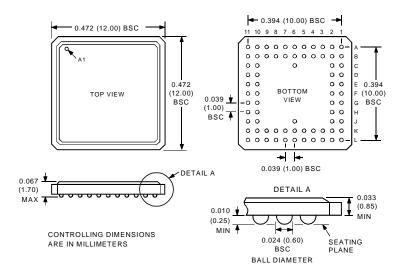

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 74-Lead LFBGA (BC-74)

-10- REV. PrF