S3027

### **FEATURES**

- Complies with ANSI, Bellcore, and ITU-T specifications for jitter tolerance, jitter transfer and jitter generation

- On-chip high frequency PLL with internal loop filter for clock recovery

- Supports clock recovery for OC-12/STM-4 (622.08 Mbit/s) or OC-3/STM-1 (155.52 Mbit/s) NRZ data

- 19.44 MHz reference frequency

- · Lock detect—monitors run length and frequency

- 350mW typical power dissipation

- · Low-jitter PECL interface

- Maintains downstream clock in absence of data inputs

- Micro-power Bipolar technology

- 5V supply

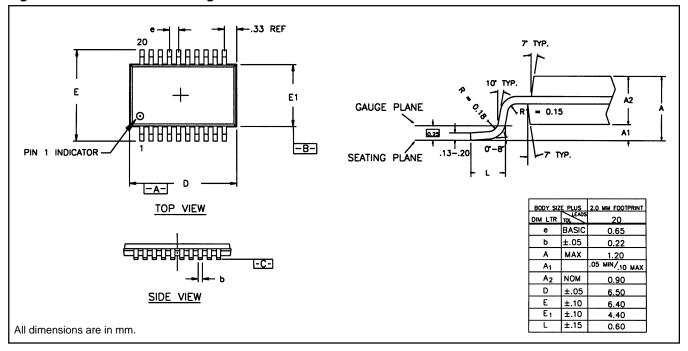

- · Available in a 20 TSSOP package

### **GENERAL DESCRIPTION**

The function of the S3027 clock recovery unit is to derive high speed timing signals for SONET/SDH-based equipment. The S3027 is implemented using AMCC's proven Phase Locked Loop (PLL) technology.

The S3027 receives either an OC-12/STM-4 or OC-3/STM-1 scrambled NRZ signal and recovers the clock from the data. The chip outputs a differential PECL bit clock and retimed data.

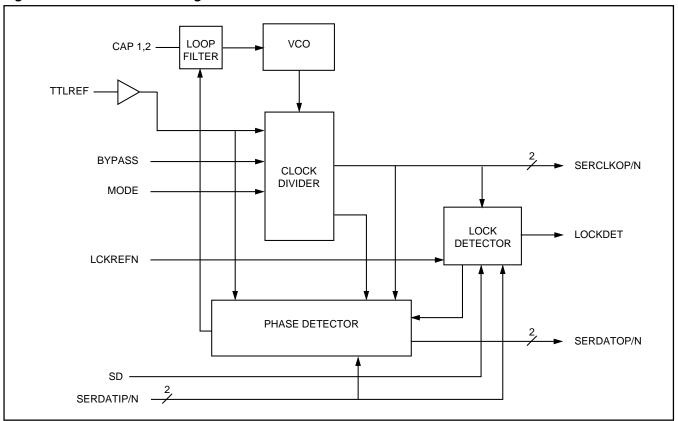

The S3027 utilizes an on-chip PLL which consists of a phase detector, a loop filter, and a voltage controlled oscillator (VCO). The phase detector compares the phase relationship between the VCO output and the serial data input. A loop filter converts the phase detector output into a smooth DC voltage, and the DC voltage is input to the VCO whose frequency is varied by this voltage. A block diagram is shown in Figure 2.

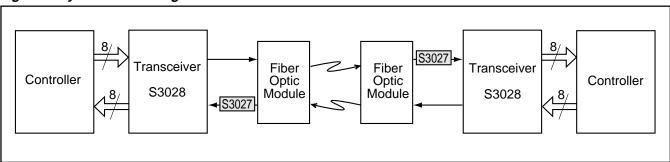

Figure 1. System Block Diagram

Figure 2. Functional Block Diagram

### **OVERVIEW**

The S3027 supports clock recovery for the OC-12/STM-4 or OC-3/STM-1 data rates. Differential serial data is input to the chip at the specified rate and clock recovery is performed on the incoming data stream. An external crystal is required to minimize the PLL lock time and provide a stable output clock source in the absence of serial input data. Retimed data and clock are output from the S3027.

### **CHARACTERISTICS**

#### **Performance**

The S3027 PLL complies with the jitter specifications proposed for SONET/SDH equipment defined by the T1X1.6/91-022 document, when used with differential inputs and outputs as shown in Figure 3.

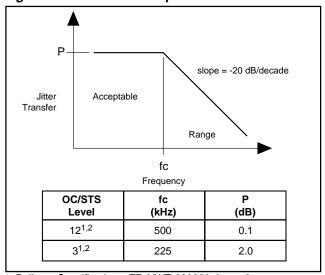

#### **Jitter Transfer**

Jitter transfer functions is defined as the ratio of jitter on the output OC-N/STS-N signal to the jitter applied on the input OC-N/STS-N signal versus frequency. Jitter transfer requirements are shown in Figure 5. The measurement condition is that input sinusoidal jitter up to the mask level in Figure 4 be applied for each of the OC-N/STS-N rates.

### **Input Jitter Tolerance**

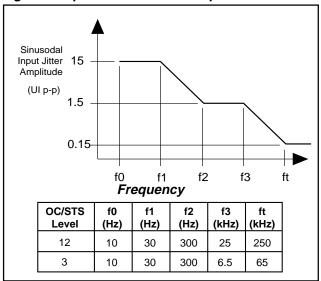

Input jitter tolerance is defined as the peak to peak amplitude of sinusoidal jitter applied on the input signal that causes an equivalent 1 dB optical/electrical power penalty. SONET input jitter tolerance requirements are shown in Figure 4. The measurement condition is the input jitter amplitude which causes an equivalent of 1 dB power penalty.

### Serial Data Output Set-up and Hold Time

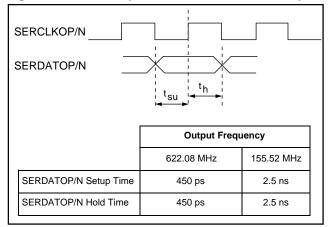

The output set-up and hold times are represented by the waveforms shown in Figure 3.

#### **Jitter Generation**

The jitter of the serial clock and serial data outputs shall not exceed .01 U.I. when a serial data input with less than 14ps (OC-12) or 56ps (OC-3) rms jitter is presented to the serial data inputs.

Figure 3. Clock Output to Data Transition Delay

Figure 4. Input Jitter Tolerance Specification

Figure 5. Jitter Transfer Specification

- Bellcore Specifications: TR-NWT-000253, Issue 2, December 1991.

- 2. CCITT Recommendations: G.958.

# S3027 Pin Assignment and Descriptions

| Pin Name             | Level         | I/O | Pin #    | Description                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|---------------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERDATIP<br>SERDATIN | Diff.<br>PECL | I   | 2 3      | Serial data in. A clock is recovered from transitions on these inputs.                                                                                                                                                                                                                                                                                                         |

| BYPASS               | TTL           | I   | 16       | Bypass enable, active high. Used during production test to bypass the VCO in the PLL. Tie to ground for normal operation.                                                                                                                                                                                                                                                      |

| SD                   | PECL          | I   | 15       | Signal detect, active high. A single-ended 10K PECL input to be driven by the external optical receiver module to indicate a loss of received optical power. When SD is inactive, the PLL will be forced to lock to the TTLREF input and the SERDATOP/N output will be held in the logic low state. When SD is active, data on the SERDATIP/N pins will be processed normally. |

| TTLREF               | TTL           | I   | 7        | Reference clock input used to establish the initial operating frequency of the clock recovery PLL and also used as a standby clock in the absence of data or when LOCKDET is inactive.                                                                                                                                                                                         |

| CAP1<br>CAP2         | _             | I   | 18<br>17 | The loop filter capacitor is connected to these pins. The capacitor value should be 1.0µf ±10% tolerance, X7'R dielectric. 50 V is recommended.                                                                                                                                                                                                                                |

| LCKREFN              | TTL           | I   | 8        | Lock to reference, active low. When active, the serial clock output will be forced to lock to the TTLREF local reference input and the SERDATOP/N output will be held on the logic low state. See Table 1.                                                                                                                                                                     |

| MODE                 | TTL           | I   | 6        | Rate select used to select the bit rate of the device. Set high to select 622.08 Mbit/s. Set low to select 155.52 Mbit/s.                                                                                                                                                                                                                                                      |

| SERDATOP<br>SERDATON | Diff.<br>PECL | 0   | 14<br>13 | Serial data out signal that is the delayed version of the incoming data stream (SERDATI) updated on the falling edge of Serial Clock Out (SERCLKOP).                                                                                                                                                                                                                           |

| SERCLKOP<br>SERCLKON | Diff.<br>PECL | 0   | 12<br>11 | Serial clock out signal that is phase aligned with Serial Data Out (SERDATOP/N). (See Figure 3.)                                                                                                                                                                                                                                                                               |

# S3027 Pin Assignment and Descriptions (Continued)

| Pin Name | Level | I/O | Pin # | Description                                                                                                                                                                                                                                                                                                                 |  |

|----------|-------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LOCKDET  | PECL  | 0   | 5     | Lock detect, active high. When active, this output indicates that the PLL is locked to the serial data inputs and valid clock and data are present at the serial outputs. When inactive, it indicates that the PLL is locked to the local reference clock. The lock detect will go inactive under the following conditions: |  |

|          |       |     |       | 1. If SDN is inactive.                                                                                                                                                                                                                                                                                                      |  |

|          |       |     |       | 2. If the serial data inputs contain insufficient run length (100 to 800 bit times).                                                                                                                                                                                                                                        |  |

|          |       |     |       | 3. If the VCO drifts away from the local reference clock by more than 1000 ppm.                                                                                                                                                                                                                                             |  |

|          |       |     |       | 4. If LCKREFN is active.                                                                                                                                                                                                                                                                                                    |  |

|          |       |     |       | Lock detect will return to the active state if the serial data contains sufficient run length specs (less than 100-800 bit times) and the serial clock is within 250 ppm of the reference clock frequency.                                                                                                                  |  |

| DGND     | GND   | ı   | 9     | Digital Ground (0V)                                                                                                                                                                                                                                                                                                         |  |

| DVCC     | +5V   | _   | 10    | Digital Power Supply (+5V)                                                                                                                                                                                                                                                                                                  |  |

| AGND     | GND   | _   | 4, 19 | Analog Ground (0V)                                                                                                                                                                                                                                                                                                          |  |

| AVCC     | +5V   | _   | 1, 20 | Analog Power Supply (+5V)                                                                                                                                                                                                                                                                                                   |  |

Figure 6. S3027A TSSOP Package

Table 1. Clock and Data Output Control

| SD | LCKREFN | LOCK<br><b>DETECT</b> | SERCLKOP/N | SERDATP/N |

|----|---------|-----------------------|------------|-----------|

| Х  | Χ       | 0                     | Active     | 0         |

| X  | 0       | X                     | Active     | 0         |

| 0  | X       | X                     | Active     | 0         |

| 1  | 1       | 1                     | Active     | Active    |

# Absolute Maximum Ratings

| Parameter                             | Min      | Тур | Max  | Unit |

|---------------------------------------|----------|-----|------|------|

| Case Temperature under Bias           | -55      |     | +125 | °C   |

| Junction Temperature under Bias       | -55      |     | +150 | °C   |

| Storage Temperature                   | -65      |     | +150 | °C   |

| Voltage on VCC with Respect to GND    | -0.5     |     | +7.0 | V    |

| Voltage on any TTL Input Pin          | -0.5     |     | +5.5 | V    |

| Voltage on any PECL Input Pin         | VCC -2.0 |     | VCC  | V    |

| TTL Output Sink Current               |          |     | 20   | mA   |

| TTL Output Source Current             |          |     | 10   | mA   |

| High Speed PECL Output Source Current |          |     | 50   | mA   |

| Static Discharge Voltage              |          | 500 |      | V    |

# **Recommended Operating Conditions**

| Parameter                                   | Min    | Тур | Max  | Unit |

|---------------------------------------------|--------|-----|------|------|

| Ambient Temperature under Bias (industrial) | -40    |     | +85  | °C   |

| Ambient Temperature under Bias (commercial) | 0      |     | +70  | °C   |

| Junction Temperature under Bias             | -10    |     | +130 | °C   |

| Voltage on VCC with Respect to GND          | 4.75   | 5.0 | 5.25 | V    |

| Voltage on Any TTL Input Pin                | 0.0    |     | VCC  | V    |

| Voltage on Any PECL Input Pin               | VCC -2 |     | VCC  | V    |

| PECL Output Source Current (50Ω to Vcc-2V)  |        | 14  | 25   | mA   |

| ICC Supply Current                          |        | 80  | 110  | mA   |

# **Performance Specifications**

| Parameter                                                             | Min  | Тур     | Max  | Units   | Condition                                                                         |

|-----------------------------------------------------------------------|------|---------|------|---------|-----------------------------------------------------------------------------------|

| Nominal VCO<br>Center Frequency                                       |      | 622.08  |      | MHz     |                                                                                   |

| Reference Clock<br>Frequency Tolerance<br>Clock Recovery <sup>1</sup> | -250 |         | +250 | ppm     |                                                                                   |

| OC-12/STS-12                                                          |      |         |      |         |                                                                                   |

| Capture Range                                                         |      | ±500ppm |      |         | With respect to fixed reference frequency                                         |

| Clock Output<br>Duty Cycle                                            | 45   |         | 55   | % of UI | Minimum transition density of 20%                                                 |

| Acquisition Lock Time <sup>1</sup><br>OC-12/STS-12                    |      |         | 16   | μsec    | With device already powered up and valid REFCLK.                                  |

| PECL Output Rise & Fall Times                                         |      |         | 600  | ps      | 10% to 90%, 50 to -2V equivalent load, 5 pf cap                                   |

| SERCLKOP/N<br>Jitter Generation                                       |      | .005    | .01  | U.I.    | With less than 14ps rms jitter on SERDATIP/N data inputs                          |

| OC-12/STS-12 Jitter Tolerance <sup>1</sup>                            | 0.5  |         |      | U.I.    | Sinusoidal input jitter. Amplitude on SERDATIP/N data inputs from 250KHz to 5MHz. |

<sup>1</sup> Guaranteed but not tested.

# TTL Input/Output DC Characteristics1

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5 \text{ V } \pm 5\%)$

| Symbol          | Parameter                     | Test Conditions                                  | Min    | Max   | Unit  |

|-----------------|-------------------------------|--------------------------------------------------|--------|-------|-------|

| $V_{IL}^{1}$    | Input LOW Voltage             | Guaranteed Input LOW Voltage for all inputs      |        | 0.8   | Volts |

| $V_{IH}^1$      | Input HIGH Voltage            | Guaranteed Input HIGH Voltage for all inputs     | 2.0    |       | Volts |

| Ι <sub>ΙL</sub> | Input LOW Current             | $V_{CC} = MAX, V_{IN} = 0.5V$                    | -400.0 |       | uA    |

| Ι <sub>ΙΗ</sub> | Input HIGH Current            | $V_{CC} = MAX, V_{IN} = 2.7V$                    |        | 50.0  | uA    |

| l <sub>l</sub>  | Input HIGH Current at Max VCC | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 5.25V   |        | 1.0   | mA    |

| los             | Output Short Circuit Current  | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 0.5V   | -100.0 | -25.0 | mA    |

| VIK             | Input Clamp Diode Voltage     | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18.0mA | -1.2   |       | Volts |

| V <sub>OL</sub> | TTL Output LOW Voltage        | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 8mA     |        | 0.5   | Volts |

| V <sub>ОН</sub> | TTL Output HIGH Voltage       | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -1.0mA  | 2.4    |       | Volts |

<sup>1.</sup> These input levels provide a zero–noise immunity and should only be tested in a static, noise-free environment.

# **PECL Input/Output DC Characteristics** ( $T_A = -40$ °C to +85°C, $V_{CC} = 5 \text{ V} \pm 5\%$ )

| Symbol          | Parameter            | Min                    | Тур   | Max                    | Unit  | Conditions                                            |

|-----------------|----------------------|------------------------|-------|------------------------|-------|-------------------------------------------------------|

| V <sub>IL</sub> | Input LOW Voltage    | V <sub>CC</sub> -2.000 |       | V <sub>CC</sub> -1.441 | Volts | Guaranteed Input LOW Voltage for single-ended inputs  |

| VIH             | Input HIGH Voltage   | V <sub>CC</sub> -1.225 |       | V <sub>CC</sub> -0.570 | Volts | Guaranteed Input HIGH Voltage for single-ended inputs |

| VIL             | Input LOW Voltage    | V <sub>CC</sub> -2.000 |       | V <sub>CC</sub> -0.700 | Volts | Guaranteed Input LOW Voltage for differential inputs  |

| VIH             | Input HIGH Voltage   | V <sub>CC</sub> -1.750 |       | V <sub>CC</sub> -0.450 | Volts | Guaranteed Input HIGH Voltage for differential inputs |

| V <sub>ID</sub> | Input Diff. Voltage  | 0.250                  | 0.500 | 1.400                  | Volts | Differential Input Voltage                            |

| lН              | Input High Current   | -0.500                 |       | 20.000                 | μΑ    | V <sub>ID</sub> = 500mV                               |

| I <sub>IL</sub> | Input Low Current    | -0.500                 |       | 20.000                 | μΑ    | V <sub>ID</sub> = 500mV                               |

| V <sub>OL</sub> | Output LOW Voltage   | V <sub>CC</sub> -2.000 | ·     | V <sub>CC</sub> -1.500 | Volts | 50 ohm termination to V <sub>CC</sub> -2V             |

| Vон             | Output HIGH Voltage  | V <sub>CC</sub> -1.110 | ·     | V <sub>CC</sub> -0.670 | Volts | 50 ohm termination to V <sub>CC</sub> -2V             |

| V <sub>OD</sub> | Output Diff. Voltage | 0.390                  |       | 1.330                  | Volts | Differential Output Voltage                           |

### Ordering Information

| GRADE                       | PART        | PACKAGE      | GRADE                            |

|-----------------------------|-------------|--------------|----------------------------------|

| S-commercial/<br>Industrial | 3027        | A - 20 TSSOP | 1 – 155 Mbps<br>Blank – 622 Mbps |

|                             |             |              |                                  |

| <u>X</u>                    | XXXX        | <u>X</u> –   | <u>X</u>                         |

| Grade                       | Part number | Package      | Speed Grade                      |

# Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121 Phone: (619) 450-9333 • (800)755-2622 • Fax: (619) 450-9885

### http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

Copyright ® 1998 Applied Micro Circuits Corporation

March 9, 1998