### INTEGRATED CIRCUITS

## DATA SHEET

# P82B96 Dual bi-directional bus buffer

Product specification

2001 Mar 06

IC12 Data Handbook

### **Dual bi-directional bus buffer**

P82B96

### **FEATURES**

- Dual Interface handles both SCL and SDA signals

- Bi-directional data transfer

- Splits I<sup>2</sup>C signal into forward/reverse Tx, Ty, Rx and Ry signals

- Low power supply current.

- Wide supply voltage range (I<sup>2</sup>C logic levels at Sx Sy independent of IC supply voltage).

- Inhibits data transfer (releases bus) if supply fails.

- Supports 100 kHz clock speed on short busses.

### **TYPICAL INTERFACES**

- Provides interface between I<sup>2</sup>C busses operating at different logic levels (e.g., 5V and 3V)

- $\bullet$  Provides interface between I2C and SMB (350  $\mu\text{A})$  bus standard.

- Simple conversion of I<sup>2</sup>C SDA or SCL signals to multi-drop differential bus hardware, e.g., via compatible PCA82C250.

- Interfaces with Opto-couplers to provide Opto isolation between I<sup>2</sup>C bus nodes.

#### DESCRIPTION

The P82B96 is a bipolar IC which creates a non-latching, bi-directional, logic interface between the normal I<sup>2</sup>C bus and a range of other bus configurations. It can interface I<sup>2</sup>C bus logic signals to similar busses having different voltage and current levels.

For example it can interface to the 350  $\mu$ A SMB bus, to 3.3 V logic devices, and to 15 V levels and/or low impedance lines to improve noise immunity on longer bus lengths.

It achieves this interface without any restrictions on the normal I $^2$ C protocols or 100 kHz clock speed. The IC adds minimal loading to the I $^2$ C node, and loadings of the new bus or remote I $^2$ C nodes are not transmitted or transformed to the local node. Restrictions on the number of I $^2$ C devices in a system, or the physical separation between them, are virtually eliminated. Transmitting SDA/SCL signals via balanced transmission lines (twisted pairs) or with galvanic isolation (opto-coupling) is simple because separate directional Tx and Rx signals are provided. The Tx and Rx signals may be directly connected, without causing latching, to provide an alternative bi-directional signal line with I $^2$ C properties.

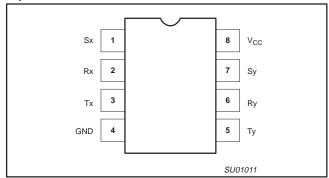

#### PIN CONFIGURATIONS

### 8-pin dual in-line or SO

### **PINNING**

| SYMBOL          | PIN | DESCRIPTION                       |

|-----------------|-----|-----------------------------------|

| Sx              | 1   | I <sup>2</sup> C Bus (SDA or SCL) |

| Rx              | 2   | Receive signal                    |

| Tx              | 3   | Transmit signal                   |

| GND             | 4   | Negative Supply                   |

| Ту              | 5   | Transmit signal                   |

| Ry              | 6   | Receive signal                    |

| Sy              | 7   | I <sup>2</sup> C Bus (SDA or SCL) |

| V <sub>CC</sub> | 8   | Positive supply                   |

### **ORDERING INFORMATION**

| TYPE     |      | PACKAGE                                                   |         |

|----------|------|-----------------------------------------------------------|---------|

| NUMBER   | NAME | DESCRIPTION                                               | VERSION |

| P82B96PN | DIP8 | plastic dual in-line package; 8 leads (300 mil)           | SOT97-1 |

| P82B96TD | SO8  | plastic small outline package; 8 leads; body width 3.9 mm | SOT96-1 |

### Dual bi-directional bus buffer

P82B96

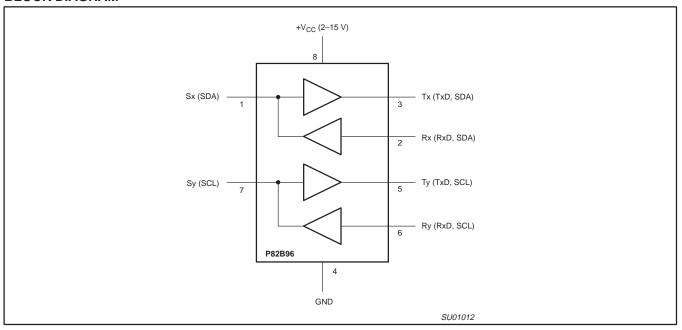

### **BLOCK DIAGRAM**

### **FUNCTIONAL DESCRIPTION**

The P82B96 has two identical buffers allowing buffering of both of the  $I^2C$  (SDA and SCL) signals. Each buffer is made up of two logic signal paths, a forward path from the  $I^2C$  interface pin which drives the buffered bus, and a reverse signal path from the buffered bus input to drive the  $I^2C$  bus interface.

Thus these paths are:

- Sense the voltage state of the I<sup>2</sup>C pin Sx (or Sy) and transmit this state to the pin Tx (Ty resp.), and

- Sense the state of the pin Rx (Ry) and pull the I<sup>2</sup>C pin low whenever Rx (Ry) is low.

The rest of this discussion will address only the "x" side of the buffer: the "y" side is identical.

The  $I^2C$  pin (Sx) is designed to interface with a normal  $I^2C$  bus.

The logic threshold voltage levels on the I<sup>2</sup>C bus are independent of the IC supply  $V_{CC}$  The maximum I<sup>2</sup>C bus supply voltage is 15 V and the guaranteed static sink current is 3 mA.

The logic level of Rx is determined from the power supply voltage  $V_{CC}$  of the chip. Logic LOW is below 42 % of  $V_{CC}$  and logic HIGH is above 58 % of  $V_{CC}$ : with a typical switching threshold of half  $V_{CC}$ .

Tx is an open collector output without ESD protection diodes to  $V_{CC}.$  It may be connected via a pull-up resistor to a supply voltage in excess of  $V_{CC},$  as long as the 15 V rating is not exceeded. It has a larger current sinking capability than a normal  $I^2C$  device, being able to sink a static current of greater than 30 mA, and typical 100 mA dynamic pull-down capability as well.

A logic LOW is only transmitted to Tx when the voltage at the  $I^2C$  pin (Sx) is below 0.6 V. A logic LOW at Rx will cause the  $I^2C$  bus (Sx) to be pulled to a logic LOW level in accordance with  $I^2C$  requirements (max. 1.5 V in 5 V applications) but not low enough to be looped back to the Tx output and cause the buffer to latch low.

The minimum LOW level this chip can achieve on the I<sup>2</sup>C bus by a LOW at Rx is typically 0.8 V.

If the supply voltage  $V_{cc}$  fails then neither the  $I^2C$  nor the Tx output will be held low. Their open collector configuration allows them to be pulled up to the rated maximum of 15 V even without  $V_{CC}$  present. The input configuration on Sx and Rx also present no loading of external signals even when  $V_{CC}$  is not present.

2001 Mar 06

### Dual bi-directional bus buffer

P82B96

### **MAXIMUM RATINGS**

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages with respect to pin GND (pin 4).

| SYMBOL                 | PARAMETER                                         | MIN. | MAX. | UNIT |

|------------------------|---------------------------------------------------|------|------|------|

| V <sub>CC</sub> to GND | Supply voltage range V <sub>CC</sub>              | -0.3 | +18  | V    |

| V <sub>bus</sub>       | Voltage range on I <sup>2</sup> C Bus, SDA or SCL | -0.3 | +18  | V    |

| V <sub>Tx</sub>        | Voltage range on buffered output                  | -0.3 | +18  | V    |

| V <sub>Rx</sub>        | Voltage range on receive input                    | -0.3 | +18  | V    |

| I                      | DC current (any pin)                              |      | 250  | mA   |

| R <sub>tot</sub>       | Power dissipation                                 |      | 300  | mW   |

| T <sub>stg</sub>       | Storage temperature range                         | -55  | +125 | °C   |

| T <sub>amb</sub>       | Operating ambient temperature range               | -40  | +85  | °C   |

### **CHARACTERISTICS**

At  $T_{amb} = 25$  °C; Voltages are specified with respect to GND with  $V_{CC} = 5$  V unless otherwise stated.

| SYMBOL                            | PARAMETER                                                                                                                                  | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Power Supply                      | •                                                                                                                                          | •    |      | •    | •    |

| V <sub>CC</sub>                   | Supply voltage (operating)                                                                                                                 | 2.0  | _    | 15   | V    |

| I <sub>CC</sub>                   | Supply current, busses HIGH                                                                                                                |      | 0.9  | 1.8  | mA   |

| I <sub>CC</sub>                   | Supply current at V <sub>CC</sub> = 15V, busses HIGH                                                                                       |      | 1.1  | 2.5  | mA   |

| I <sub>CC</sub>                   | Additional supply current per Tx or Ty LOW                                                                                                 |      | 1.7  | 3.5  | mA   |

| Bus pull-up (load                 | i) voltages and currents                                                                                                                   | •    | •    | •    | •    |

| $V_{Sx}, V_{Sy}$                  | Maximum input/output voltage level<br>Open collector $I^2C$ bus and $V_{Rx}$ , $V_{Ry}$ = HIGH                                             |      | _    | 15   | V    |

| I <sub>Sx</sub> , I <sub>Sy</sub> | Static output loading on I <sup>2</sup> C bus V <sub>Sx</sub> , V <sub>Sy</sub> = 1.2 V V <sub>Rx</sub> , V <sub>Ry</sub> = LOW            | 0.2  | _    | 3    | mA   |

| I <sub>Sx</sub> , I <sub>Sy</sub> | Dynamic output sink capability on I <sup>2</sup> C bus V <sub>Sx</sub> , V <sub>Sy</sub> > 2 V V <sub>Rx</sub> , V <sub>Ry</sub> = LOW     | 7    | 18   | _    | mA   |

| $I_{Sx}, I_{Sy}$                  | Leakage current on I <sup>2</sup> C bus $V_{Sx}$ , $V_{Sy}$ = 5 V, and $V_{Rx}$ , $V_{Ry}$ = HIGH                                          | _    | _    | 1    | μΑ   |

| I <sub>Sx</sub> , I <sub>Sy</sub> | Leakage current on $I^2C$ bus $V_{Sx}$ , $V_{Sy}$ = 15 V, and $V_{Rx}$ , $V_{Ry}$ = HIGH                                                   | _    | 1    | _    | μΑ   |

| $V_{Tx}, V_{Ty}$                  | Maximum output voltage level Open collector                                                                                                | _    | _    | 15   | V    |

| I <sub>Tx</sub> , I <sub>Ty</sub> | Static output loading on buffered bus $V_{Tx}$ , $V_{Ty}$ = 0.4 V $V_{Sx}$ , $V_{Sy}$ = LOW on I <sup>2</sup> C bus = 0.4V                 | _    | _    | 30   | mA   |

| I <sub>Tx</sub> , I <sub>Ty</sub> | Dynamic output sink capability, buffered bus: $V_{Tx}$ , $V_{Ty} > 1 \text{ V}$ $V_{Sx}$ , $V_{Sy} = \text{LOW on I}^2\text{C}$ bus = 0.4V | 60   | 100  | _    | mA   |

| I <sub>Tx</sub> , I <sub>Ty</sub> | Leakage current on buffered bus $V_{Tx}$ , $V_{Ty} = V_{CC} = 15 \text{ V}$ , and $V_{Sx}$ , $V_{Sy} = \text{HIGH}$                        | _    | 1    | _    | μΑ   |

### Dual bi-directional bus buffer

P82B96

| SYMBOL                                                                                              | PARAMETER                                                                                                                                                                                 | MIN.     | TYP. | MAX.     | UNIT |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|----------|------|

| Input Currents                                                                                      | •                                                                                                                                                                                         |          |      |          | •    |

| I <sub>Sx</sub> , I <sub>Sy</sub>                                                                   | Input current from $I^2C$ bus, bus LOW $V_{Rx}$ , $V_{Ry}$ = HIGH                                                                                                                         | <u> </u> | -1   | _        | μΑ   |

| I <sub>Rx</sub> , I <sub>Ry</sub>                                                                   | Input current from buffered bus, bus LOW $V_{Rx}$ , $V_{Ry} = 0.4 \text{ V}$                                                                                                              | _        | -1   | _        | μΑ   |

| $I_{Rx}$ , $I_{Ry}$                                                                                 | Leakage current on buffered bus input $V_{Rx}$ , $V_{Ry} = V_{CC}$                                                                                                                        | _        | 1    | _        | μΑ   |

| Input Thresholds                                                                                    | •                                                                                                                                                                                         |          | -    |          |      |

| $V_{Sx}, V_{Sy}$                                                                                    | Output logic level LOW, on normal $I^2C$ bus $I_{Sx}$ , $I_{Sy} = 3$ mA                                                                                                                   | 0.8      | 0.9  | 1.0      | V    |

| V <sub>Sx</sub> , V <sub>Sy</sub>                                                                   | Output logic level LOW, on normal $I^2C$ bus $I_{Sx}$ , $I_{Sy} = 0.2$ mA                                                                                                                 | _        | 750  | _        | mV   |

| $V_{Sx}, V_{Sy}$                                                                                    | Input logic level LOW threshold On normal I <sup>2</sup> C bus                                                                                                                            | 600      | 650  | _        | mV   |

| dV <sub>Sx</sub> /dT, dV <sub>Sy</sub> /dT                                                          | Temperature coefficient of thresholds                                                                                                                                                     | 1 –      | -2   | <u> </u> | mV/K |

| $V_{Rx}, V_{Ry}$                                                                                    | Input logic HIGH level Fraction of applied V <sub>CC</sub>                                                                                                                                | 0.58     | _    | _        |      |

| $V_{Rx}$ , $V_{Ry}$                                                                                 | Input threshold Fraction of applied V <sub>CC</sub>                                                                                                                                       | _        | 0.5  | _        |      |

| $V_{Rx}$ , $V_{Ry}$                                                                                 | Input logic LOW level Fraction of applied V <sub>CC</sub>                                                                                                                                 | _        | _    | 0.42     |      |

| Bus Release on Vo                                                                                   | CC Failure                                                                                                                                                                                | •        |      |          |      |

| $V_{Sx}$ , $V_{Sy}$ , $V_{Tx}$ , $V_{Ty}$                                                           | V <sub>CC</sub> voltage at which all busses are guaranteed to be released                                                                                                                 | _        | _    | 1        | V    |

| dV/dT                                                                                               | Temperature coefficient of guaranteed release voltage                                                                                                                                     | _        | -4   | _        | mV/K |

| Buffer response til                                                                                 | me                                                                                                                                                                                        |          |      |          |      |

| T <sub>fall delay</sub><br>V <sub>Sx</sub> to V <sub>Tx</sub><br>V <sub>Sy</sub> to V <sub>Ty</sub> | Buffer time delay on FALLING input between $V_{SX}$ = input switching threshold: and $V_{Tx}$ output falling 50%. $R_{Tx}$ pull up = 160 $\Omega$ , no capacitive load, $V_{CC}$ = 5 $V$  | _        | 100  | _        | ns   |

| T <sub>rise delay</sub><br>V <sub>Sx</sub> to V <sub>Tx</sub><br>V <sub>Sy</sub> to V <sub>Ty</sub> | _                                                                                                                                                                                         | 100      | _    | ns       |      |

| T <sub>fall delay</sub><br>V <sub>Rx</sub> to V <sub>Sx</sub><br>V <sub>Ry</sub> to V <sub>Sy</sub> | Buffer time delay on FALLING input between $V_{Rx}$ = input switching threshold, and $V_{Sx}$ output falling 50%. $R_{Sx}$ pull up = 1600 $\Omega$ , no capacitive load, $V_{CC}$ = 5 $V$ | _        | 300  | _        | ns   |

| T <sub>rise delay</sub><br>V <sub>Rx</sub> to V <sub>Sx</sub> V <sub>Ry</sub> to<br>V <sub>Sy</sub> | Buffer time delay on RISING input between $V_{Rx}$ = input switching threshold, and $V_{Sx}$ output reaching 50%. $R_{Sx}$ pull up = 1600 $\Omega$ , no capacitive load, $V_{CC}$ = 5 $V$ |          | 300  | _        | ns   |

### Dual bi-directional bus buffer

P82B96

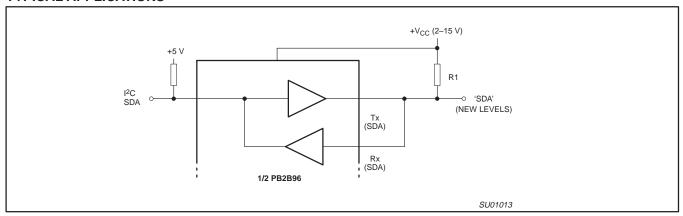

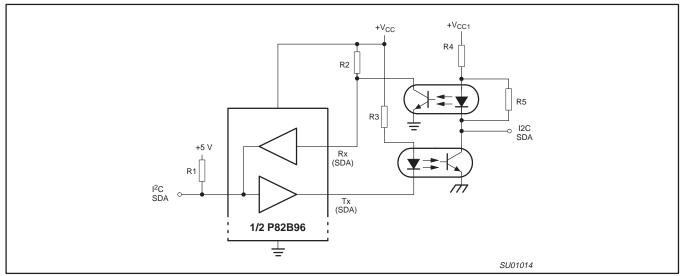

### **TYPICAL APPLICATIONS**

Figure 1. Interfacing an ' $I^2C$ ' type of bus with different logic levels.

Figure 2. Galvanic isolation of I<sup>2</sup>C nodes via opto-couplers

### Dual bi-directional bus buffer

P82B96

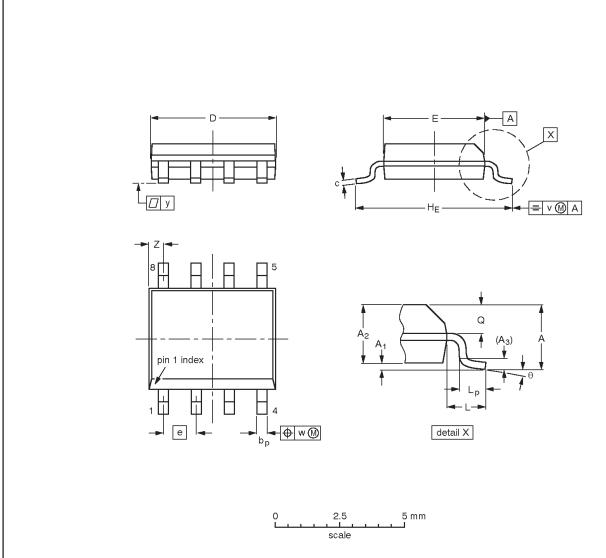

### SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | Α1             | A <sub>2</sub> | A <sub>3</sub> | bр           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е     | HE             | L     | Lp             | Q              | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|-------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27  | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6     | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.050 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 | 0.028<br>0.024 | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |        | REFER  | ENCES | EUROPEAN   | ISSUE DATE                      |

|---------|--------|--------|-------|------------|---------------------------------|

| VERSION | IEC    | JEDEC  | EIAJ  | PROJECTION | 1330E DATE                      |

| SOT96-1 | 076E03 | MS-012 |       | €          | <del>97-05-22</del><br>99-12-27 |

### Dual bi-directional bus buffer

P82B96

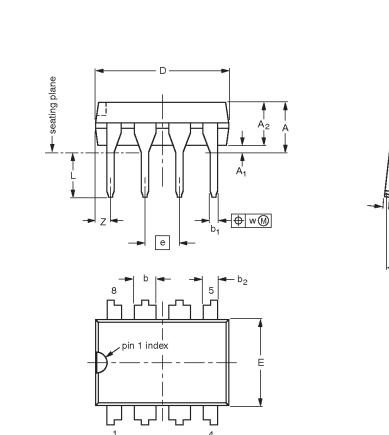

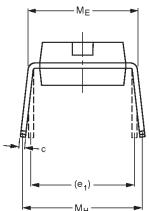

### DIP8: plastic dual in-line package; 8 leads (300 mil)

SOT97-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | b <sub>2</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME           | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|--------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.14   | 0.53<br>0.38   | 1.07<br>0.89   | 0.36<br>0.23   | 9.8<br>9.2       | 6.48<br>6.20     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80 | 10.0<br>8.3  | 0.254 | 1.15                     |

| inches | 0.17      | 0.020                  | 0.13                   | 0.068<br>0.045 | 0.021<br>0.015 | 0.042<br>0.035 | 0.014<br>0.009 | 0.39<br>0.36     | 0.26<br>0.24     | 0.10 | 0.30           | 0.14<br>0.12 | 0.32<br>0.31 | 0.39<br>0.33 | 0.01  | 0.045                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |        | REFEF  | RENCES   | EUROPEAN   | ISSUE DATE                      |

|---------|--------|--------|----------|------------|---------------------------------|

| VERSION | IEC    | JEDEC  | EIAJ     | PROJECTION | 1330E DATE                      |

| SOT97-1 | 050G01 | MO-001 | SC-504-8 |            | <del>95-02-04</del><br>99-12-27 |

2001 Mar 06

### Dual bi-directional bus buffer

P82B96

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                             |

|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                          |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 2001 All rights reserved. Printed in U.S.A.

Date of release: 03-01

Document order number: 9397 750 08122

Let's make things better.

Philips Semiconductors