# 10Gbit/s X2 1310 nm Transponder (TRP10GDP0x03)

#### **Features**

- Compatible with X2 MSA Rev. 2.0b

- Support of IEEE 802.3ae 10GBASE-LR at 10.3125Gbit/s (TRP10GDP0303)

- Compliance to Fibre Channel 1200-SM-LL-L at 10.51875Gbit/s (TRP10GDP0403)

- Transmission distance up to 10 km over SMF

- Low Power Consumption 2.0 W (typ.)

- Case Temperature Range 0°C 70°C

- Laser Class 1 compliant

- SC duplex connector

- Uncooled 1310nm DFB Laser

- Hot pluggable 70-pin connector with XAUI electrical interface

- Management and control via MDIO 2-wire interface

- Complaint with the EU RoHS 6 Environmental requirements

# **General Description and Applications**

The TRP10GDP0x03 is a highly integrated, serial optical transponder module for high-speed, 10Gbit/s data

transmission applications. The module is fully compliant to IEEE 802.3ae standard for Ethernet, making it ideally suited for 10 GbE datacom (rackto-rack, client interconnection) applications.

| Standard       | Description  | Nominal<br>Baud Rate | Unit |

|----------------|--------------|----------------------|------|

| IEEE 802.3ae   | 10 GBASE-LR  | 10.3125              | GBd  |

| 10GFC Rev. 4.0 | 1200-SM-LL-L | 10.5128              | GBd  |

Designed for distances of up to 10km the transponder module comprises a transmitter with a directly modulated uncooled 1310nm DFB laser, a receiver with a PIN photodiode, a XAUI-Attachment Interface, an integrated Coder / Decoder and multiplexer / demultiplexer (SERDES: Serializer / Deserializer). The transponder operates within a wide case temperature range of 0°C to +70°C and offers optimum heat dissipation and excellent electromagnetic shielding which enables high port densities for 10 GbE systems. A 70 pin electrical connector and a duplex SC connector optical interface assure that connectivity is compliant to the X2 and XENPAK MSA.

### **CONTENT:**

| ABSOLUTE MAXIMUM RATINGS                                                              |     |

|---------------------------------------------------------------------------------------|-----|

| RECOMMENDED OPERATING CONDITIONS                                                      | . : |

| ELECTRICAL CHARACTERISTICS                                                            |     |

| XAUI - InterfaceXAUI Input CharacteristicsXAUI Output Characteristics                 |     |

| OPTICAL INTERFACE                                                                     | . ( |

| Recommended Operating Conditions Transmitter Characteristics Receiver Characteristics | . ( |

| MDIO INTERFACE                                                                        | , , |

| DC Characteristics                                                                    |     |

| ELECTRO STATIC DISCHARGE (ESD)                                                        | , 8 |

| THERMAL MANAGEMENT                                                                    |     |

| CARD-EDGE-CONNECTOR-PINNING AND LAYOUT                                                | , 9 |

| ELECTRICAL PIN DEFINITION – PINS 01 TO 40 OF 70                                       |     |

| EYE SAFETY                                                                            |     |

| MECHANICAL DRAWING                                                                    |     |

| ORDER INFORMATION                                                                     | _4  |

# **Absolute Maximum Ratings**

| Rating                            | Conditions/Remark              | Symbol                | Min  | Max  | Units |

|-----------------------------------|--------------------------------|-----------------------|------|------|-------|

| Storage Ambient Temperature       | non condensing                 | $artheta_{stg}$       | -40  | +85  | °C    |

| Powered Case Temperature          | non condensing                 | $artheta_{	extsf{c}}$ | -10  | +75  | °C    |

| Adaptable Power Supply (APS)      | Voltage @ Pin APS Sense        | V <sub>APSsense</sub> | -0.3 | 1.5  | V     |

| Supply Voltage 3.3V Rail          |                                | V <sub>CC3</sub>      | -0.3 | 4.0  | V     |

| Supply Voltage 5V Rail            |                                | V <sub>CC5</sub>      | -0.5 | 7.0  | V     |

| Input Voltage Low Speed Signals   | RESET, TxOn/Off, PRTADR40      | Vı                    | -0.5 | 3.3  | V     |

| Clamp Currents Low Speed Signals  | RESET, TxOn/Off, PRTADR40 V<0V | I <sub>IK</sub>       | -50  |      | mA    |

| LASI Voltage                      |                                | $V_{Q}$               | -0.5 | 3.3  | V     |

| LASI Sink Current                 | Continuous Sink Current        | I <sub>QL</sub>       |      | 20   | mA    |

| XAUI Input Level                  |                                | V <sub>IXAUI</sub>    | -0.4 | 2.3  | V     |

| Differential XAUI Input Amplitude |                                | V <sub>IDXAUI</sub>   |      | 1000 | mV    |

| Optical Receiver Input Power      | Average Receiver Input Power   | P <sub>Rx</sub>       |      | +1.5 | dBm   |

| Static Discharge Voltage          | MIL STD 883 Method 3015.1      |                       |      | 500  | V     |

Any stress beyond the maximum ratings can result in permanent damage. The device specifications are guaranteed only under the recommended operating conditions.

# **Recommended Operating Conditions**

| Parameter                            | Conditions / Remark             | Symbol                | Min   | Тур  | Max   | Units |

|--------------------------------------|---------------------------------|-----------------------|-------|------|-------|-------|

| Operating Case Temperature Range     |                                 | $\vartheta_{Case}$    | 0     |      | +70   | °C    |

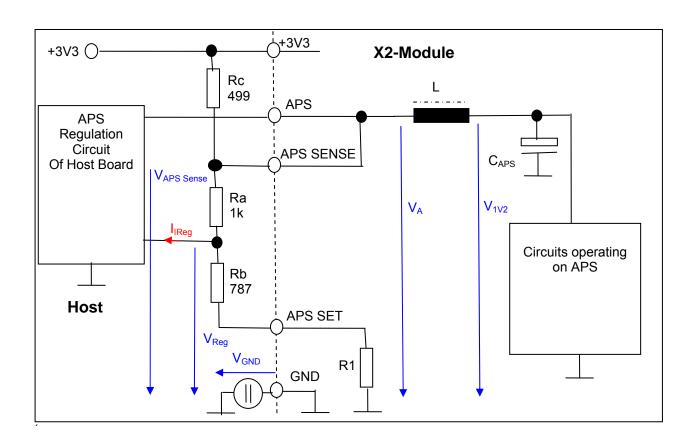

| APS Feedback Voltage <sup>1)2)</sup> | Ra=1kΩ ±0,1%, Rb=787Ω±0,1%      | V <sub>Feedback</sub> | 770   | 800  | 815   | mV    |

|                                      | Ra=1kΩ ±1%, Rb=787Ω±1%          | V <sub>Feedback</sub> | 785   |      | 812   | mV    |

| APS Sense Voltage <sup>1)2)</sup>    | Just for informational purposes | V <sub>APSsense</sub> | 1.164 | 1.21 | 1.265 | V     |

| Power Supply Voltage @ 3.3V          |                                 | V <sub>CC3</sub>      | 3.135 | 3.3  | 3.465 | V     |

| Power Supply Voltage @ 5.0V          |                                 | V <sub>CC5</sub>      | 4.75  | 5.00 | 5.25  | V     |

<sup>1)</sup> The device is supposed to operate in the APS control environment described and specified in the XENPAK-MSA (page 22 to 24 of Revision 3.0). In this environment the APS-Sense Voltage requirements will be automatically satisfied if APS-Feedback Voltage is within its recommended range. The operating APS-Sense Voltage is for informational purposes and is subject to be changed without further notice.

2) A more detailed description on the APS control circuit can also be found on page 3.

# **Functional Block Diagram of APS Regulation**

# **Electrical Characteristics**

| Parameter             | Conditions                             | Symbol              | Min  | Тур | Max | Units |

|-----------------------|----------------------------------------|---------------------|------|-----|-----|-------|

| 5V Supply Current     | P <sub>Rx</sub> = 0 <u>0.5</u> 1.125mW | I <sub>VCC5</sub>   | 0.38 | 0.7 | 3.5 | mA    |

| 3.3V Supply Current   | RESET=H, TxOn/Off = H                  | I <sub>VCC3</sub>   | 310  | 360 | 576 | mA    |

| APS Supply Current    | V <sub>Feedback</sub> = 785800812mV    | I <sub>VCCAPS</sub> | 550  | 650 | 755 | mA    |

| APS-Input Capacitance |                                        | C <sub>APS</sub>    | 127  | 158 | 200 | μF    |

### **XAUI - Interface**

### **XAUI Input Characteristics**

| Parameter                           | Conditions                  | Symbol            | Min  | Тур    | Max   | Units      |

|-------------------------------------|-----------------------------|-------------------|------|--------|-------|------------|

| Data Rate                           | 10GBASE-LR module           |                   |      | 3.125  |       | GBd        |

|                                     | 1200-SM-LL-L module         |                   |      | 3.1875 |       | GBd        |

|                                     | Relative Tolerance          |                   | -100 |        | +100  | ppm        |

| Differential Input Voltage Swing    | 8B/10B Coded Input Signal   | $V_{\text{ID}}$   | 175  |        | 2,000 | $mV_{P-P}$ |

| Differential Return Loss            | 100MHz – 2.5GHz             | SDD11             | 10   |        |       | dB         |

| Common Mode Return Loss             | 100MHz – 2.5GHz             | SCC11             | 6    |        |       | dB         |

| Total Peak-to-Peak Jitter Tolerance | Sinusoidal Jitter @ 0 20MHz | T <sub>jRDS</sub> | 0.32 |        |       | UI         |

| Differential Input Impedance        |                             | R <sub>IND</sub>  | 80   | 100    | 120   | Ω          |

Note: XAUI-input-Lanes are ac-inputs.

### **XAUI Output Characteristics**

| Parameter                         | Conditions                     | Symbol   | Min  | Тур    | Max   | Units      |

|-----------------------------------|--------------------------------|----------|------|--------|-------|------------|

| XAUI Data Rate                    | 10GBASE-LR module              |          |      | 3.125  |       | GBd        |

|                                   | 1200-SM-LL-L module            |          |      | 3.1875 |       | GBd        |

|                                   | XAUI Data Rate Tolerance       |          | -100 |        | +100  | ppm        |

| Differential Output Voltage Swing | $R_{LOAD} = 100\Omega \pm 5\%$ |          | 800  |        | 1,600 | $mV_{P-P}$ |

| Differential Output Impedance     |                                | $R_{QD}$ | 80   | 100    | 120   | Ω          |

| Differential Transition Time      | 20% - 80%                      |          | 50   |        | 130   | ps         |

| Total Output Jitter               |                                |          |      |        | 0.17  | UI         |

| Total Deterministic Output Jitter |                                |          |      |        | 0.08  | UI         |

Note: XAUI-output-Lanes are ac-outputs.

# **Optical Interface**

#### **Recommended Operating Conditions**

| Parameter             | Remark                              | Symbol               | Min   | Тур      | Max             | Units     |

|-----------------------|-------------------------------------|----------------------|-------|----------|-----------------|-----------|

| Operating Range       | Single Mode Fiber                   | I <sub>OP</sub>      | 2     |          | 10,000          | m         |

| Input Data Rate       | 10GBASE-LR module                   | DR <sub>o</sub>      |       | 10.3125  |                 | Gbd       |

|                       | 1200-SM-LL-L module                 |                      |       | 10.51875 |                 | GBd       |

|                       | relative tolerance                  | $\Delta DR/DR_{typ}$ | -100  |          | +100            | ppm       |

| Receiver Input Signal | Center Wavelength                   | λc                   | 1,260 | 1,310    | 1,360           | nm        |

|                       | Average Input Power                 | P <sub>IN</sub>      | -11   |          | 0.5             | dBm       |

|                       | Input Signal Amplitude <sup>1</sup> | P <sub>INP</sub>     | 22.5  |          | P <sub>IN</sub> | $\mu W_p$ |

Amplitude means difference from average power to either eye opening boundary.

#### **Transmitter Characteristics**

if not otherwise mentioned under recommended operating conditions and standard compliant single mode fiber

| in not otherwise mentioned under recommended operating conditions and standard compilant single mode liber. |                                  |                      |       |          |       |       |

|-------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------|-------|----------|-------|-------|

| Characteristic                                                                                              | Conditions                       | Symbol               | Min   | Тур      | Max   | Units |

| Data Rate                                                                                                   | 10GBASE-LR module                | DR                   |       | 10.3125  |       | Gbps  |

|                                                                                                             | 1200-SM-LL-L module              |                      |       | 10.51875 |       | Gbps  |

|                                                                                                             | relative tolerance to nominal DR | $\Delta DR/DR_{typ}$ | -100  |          | 100   | ppm   |

| Nominal Wavelength                                                                                          |                                  | $\lambda_{TRP}$      | 1,260 | 1,310    | 1,355 | nm    |

| Side Mode Suppression Ratio                                                                                 |                                  | SMSR                 | 30    |          |       | dB    |

| Optical Output Power                                                                                        |                                  | P <sub>out</sub>     | -6    |          | 0.5   | dBm   |

| Extinction Ratio                                                                                            | EOL                              | ER                   | 3.5   | 8        |       | dB    |

| Optical Modulation Amplitude                                                                                |                                  | OMA                  | 500   |          |       | μW    |

| Transmitter Penalty                                                                                         | Bessel-Thompson Filter           | TP                   |       |          | 3     | dB    |

| Overshoot                                                                                                   | Bessel-Thompson Filter           | OS                   |       |          | 40    | %     |

#### **Receiver Characteristics**

if not otherwise mentioned under recommended operating conditions and standard compliant single mode fiber.

| Parameter                     | Conditions                                      | Symbol                | Min  | Тур      | Мах   | Units |

|-------------------------------|-------------------------------------------------|-----------------------|------|----------|-------|-------|

| Data Rate                     | 10GBASE-LR module                               | DR                    |      | 10.3125  |       | Gbps  |

|                               | 1200-SM-LL-L module                             |                       |      | 10.51875 |       | Gbps  |

|                               | relative tolerance to nominal DR                | ΔDR/DR <sub>typ</sub> | -100 |          | 100   | ppm   |

| Receiver Sensitivity          | OMA, BER 10 <sup>-12</sup> @ 2 <sup>31</sup> -1 | P <sub>INpp</sub>     |      |          | -12.6 | dBm   |

| Stressed Receiver Sensitivity | OMA                                             | P <sub>INpp</sub>     |      |          | -10.3 | dBm   |

| Saturation Input Power        |                                                 | P <sub>SAT</sub>      | 0.5  |          |       | dBm   |

Note: <sup>1)</sup>with ideal transmitter

Note: The specified characteristics are met within the recommended range of operating conditions and under the default settings of output power and modulation amplitude. Changing the settings of the optical output power will affect the dynamic behavior of the output signal. Unless otherwise noted, typical data is quoted at nominal voltages and +25°C ambient temperature.

# **MDIO** Interface

#### **DC Characteristics**

if not otherwise mentioned under the recommended operating conditions.

| Characteristic         | Condition                                                     | Symbol             | Minimum | Maximum | Unit |

|------------------------|---------------------------------------------------------------|--------------------|---------|---------|------|

| Input high voltage     |                                                               | V <sub>IH</sub>    | 0.84    | 1.5     | V    |

| Input low voltage      |                                                               | V <sub>IL</sub>    | -0.3    | 0.36    | V    |

| MDIO Input current     | MMD Driver in tri-state                                       | I <sub>IMDIO</sub> | -10     | 8       | μΑ   |

| MDC Input current      |                                                               | I <sub>IMDC</sub>  | -5      | 5       | μΑ   |

| Output low voltage     | I <sub>OL</sub> = 100μA                                       | $V_{QL}$           | -0.3    |         | V    |

|                        | I <sub>OL</sub> = 4mA                                         | $V_{QL}$           |         | 0.2     | V    |

| Output high voltage    | $R_{PULL-Up} = 357\Omega \pm 1\%$<br>$V_{PULL-Up} = 1.141.5V$ | $V_{QH}$           | 1.136   | 1.5     | V    |

| Output low current     | V <sub>I</sub> = 0.2V                                         | $I_{QL}$           | +4      |         | mA   |

| MDIO Input capacitance | V <sub>I</sub> = 01.5V                                        | C <sub>in</sub>    |         | 10      | pF   |

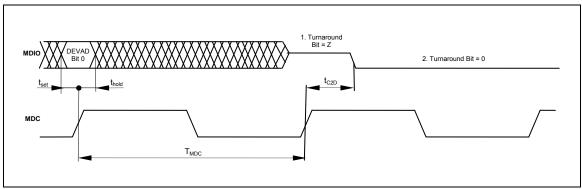

#### **AC Characteristics**

if not otherwise mentioned under the recommended operating conditions. Furthermore its recommended that clock period time  $T_{\text{MDC}}$  is not less than 310ns and the sum of input currents of loads on the bus does not exceed 256µA at high and at low not below -320µA.

| Characteristic     | Condition                                                | Symbol            | Minimum | Maximum | Unit |

|--------------------|----------------------------------------------------------|-------------------|---------|---------|------|

| Set Up Time        |                                                          | t <sub>set</sub>  |         | 10      | ns   |

| Hold Time          |                                                          | t <sub>hold</sub> |         | 10      | ns   |

| Clock to Data Time | R <sub>PULL-Up</sub> = 357Ω ±1%, C <sub>BUS</sub> ≤470pF | t <sub>C2D</sub>  | 0       | 300     | ns   |

Example Timing Diagram: Turnover Timing at Read Cycle

# **Electro Static Discharge (ESD)**

The maximum electrostatic charge based on a human body model and the conditions as outlined below is:

| Parameter                | Conditions                | Symbol | Min | Тур | Max | Units |

|--------------------------|---------------------------|--------|-----|-----|-----|-------|

| Static Discharge Voltage | MIL STD 883 Method 3015.1 |        |     | 500 | ٧   |       |

# **Thermal Management**

omission.

The transponder is designed for an operation within a case temperature range between 0 to  $+70^{\circ}$ C at an altitude of < 3km. The built in heatsink provides an optimized thermal performance. The user needs to guarantee per system design not to exceed this temperature range. It has to be considered that in case of usage of multiple modules on a single hostboard that there is a temperature rise among the modules hosted side by side (see figure below). Airflow direction and air speed needs to be choosen accordingly. For further information it is referred to the MSA document.

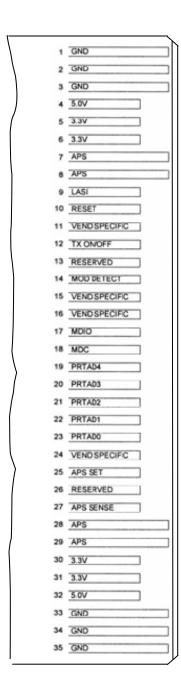

# **Card-Edge-Connector-Pinning and Layout**

| 70 | GND       |

|----|-----------|

| 69 | GND       |

| 68 | RESERVED  |

|    | RESERVED  |

| 66 | GND       |

| 65 | TX LANE3- |

| 64 | TX LANE3+ |

| 63 | GND       |

| 62 | TX LANE2- |

| 61 | TX LANE2+ |

| 60 | GND       |

| 59 | TX LANE1- |

| 58 | TX LANE1+ |

| 57 | GND       |

| 56 | TX LANEO- |

| 55 | TX LANE0+ |

| 54 | GND       |

| 53 | GND       |

| 52 | GND       |

| 51 | RX LANE3- |

| 50 | RX LANE3+ |

| 49 | GND       |

| 48 | RX LANE2- |

| 47 | RX LANE2+ |

| 45 | GND       |

| 45 | RX LANE1- |

| 44 | RX LANE1+ |

| 43 | GND       |

| 42 | RX LANEO- |

| 41 | RX LANE0+ |

| 40 | GND       |

| 39 | RESERVED  |

|    | RESERVED  |

| 37 | GND       |

|    |           |

Top view -Top side

Top view-Bottom row (as seen through PCB)

36 GND

# Electrical Pin Definition - Pins 01 to 40 of 70

| Symbol       | Logic                                | PIN                                                                                               | Name / Description                                                                                                                                                                                                | Note |

|--------------|--------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.3V         |                                      | 5, 6, 30, 31                                                                                      | Power Supply of Optical Receiver and Transmitter and Control Circuits                                                                                                                                             | 2    |

| 5.0V         |                                      | 4, 32                                                                                             | Power Supply of Optical Receiver Frontend                                                                                                                                                                         | 2    |

| APS          |                                      | 7, 8, 28, 29                                                                                      | Adaptive Power Supply, Supply of PHY XS and PCS Layer Devices                                                                                                                                                     | 2    |

| APS SENSE    |                                      | 27                                                                                                | APS Sense Output for APS Control Circuit                                                                                                                                                                          |      |

| APS SET      |                                      | 25                                                                                                | Feedback Input for APS, Input of APS Setting Resistor                                                                                                                                                             |      |

| GND          |                                      | 1, 2, 3, 33,<br>34, 35, 36,<br>37, 40, 43,<br>46, 49, 52,<br>53, 54, 57,<br>60, 63, 66,<br>69, 70 | Common Electrical Ground                                                                                                                                                                                          | 1    |

| LASI         | 1.2V<br>CMOS<br>Open Drain<br>Output | 9                                                                                                 | Link Alarm Status Interrupt, low active, Open Drain Output Supposed to operate with $10 \mathrm{K}\Omega$ - $22 \mathrm{K}\Omega$ pull upon host. Logic High: Normal Operation Logic Low: Link Alarm is indicated |      |

| MDC          |                                      | 18                                                                                                | Management Clock Input                                                                                                                                                                                            | 3    |

| MDIO         |                                      | 17                                                                                                | Management Data IO                                                                                                                                                                                                | 3    |

| MOD DETECT   |                                      | 14                                                                                                | 1kΩ to Ground for APS Circuit Environment                                                                                                                                                                         |      |

| PRTADO       | 1.2V<br>CMOS<br>Input                | 23                                                                                                | Port Address Bit 0 (Low = 0), internally pulled up by $18k\Omega$                                                                                                                                                 |      |

| PRTAD1       | 1.2V<br>CMOS<br>Input                | 22                                                                                                | Port Address Bit 1 (Low = 0), internally pulled up by $18k\Omega$                                                                                                                                                 |      |

| PRTAD2       | 1.2V<br>CMOS<br>Input                | 21                                                                                                | Port Address Bit 2 (Low = 0), internally pulled up by $18k\Omega$                                                                                                                                                 |      |

| PRTAD3       | 1.2V<br>CMOS<br>Input                | 20                                                                                                | Port Address Bit 3 (Low = 0), internally pulled up by $18k\Omega$                                                                                                                                                 |      |

| PRTAD4       | 1.2V<br>CMOS<br>Input                | 19                                                                                                | Port Address Bit 4 (Low = 0), internally pulled up by $18k\Omega$                                                                                                                                                 |      |

| RESERVED     |                                      | 13, 38, 39,<br>67, 68                                                                             | Reserved by MSA, internally not connected                                                                                                                                                                         |      |

| RESERVED     |                                      | 26                                                                                                | Reserved for Avalanche Photodiode use, internally not connected                                                                                                                                                   | 5    |

| RESET        | 1.2V<br>CMOS<br>Input                | 10                                                                                                | Low active Reset Input 10KΩ pull-up on Transceiver Logic high = Normal Operation Logic Low = Reset asserted                                                                                                       |      |

| TX ON/OFF    | 1.2V<br>CMOS<br>Input                | 12                                                                                                | High active Transmitter Enable Input 10KΩ pull-up on Transceiver Logic high = Transmitter active (normal Operation) And Register Bit 1.9.0 set to low as well Logic Low = shut down of Transmitter                |      |

| VENDSPECIFIC |                                      | 11, 15, 16, 24                                                                                    | Vendor Specific Pin,. for proper operation leave unconnected                                                                                                                                                      | 5    |

### Electrical Pin Definition - Pins 41 to 70 of 70

| Symbol    | Logic | PIN | Name / Description         | Note |

|-----------|-------|-----|----------------------------|------|

| RX LANE0+ |       | 41  | Module XAUI Output Lane 0+ | 4    |

| RX LANE0- |       | 42  | Module XAUI Output Lane 0- | 4    |

| RXLANE1+  |       | 44  | Module XAUI Output Lane 1+ | 4    |

| RXLANE1-  |       | 45  | Module XAUI Output Lane 1- | 4    |

| RX LANE2+ |       | 47  | Module XAUI Output Lane 2+ | 4    |

| RX LANE2- |       | 48  | Module XAUI Output Lane 2- | 4    |

| RX LANE3+ |       | 50  | Module XAUI Output Lane 3+ | 4    |

| RX LANE3- |       | 51  | Module XAUI Output Lane 3- | 4    |

| TX LANE0+ |       | 55  | Module XAUI Input Lane 0+  | 4    |

| TX LANE0- |       | 56  | Module XAUI Input Lane 0-  | 4    |

| TXLANE1 + |       | 58  | Module XAUI Input Lane 1+  | 4    |

| TXLANE1-  |       | 59  | Module XAUI Input Lane 1-  | 4    |

| TX LANE2+ |       | 61  | Module XAUI Input Lane 2+  | 4    |

| TX LANE2- |       | 62  | Module XAUI Input Lane 2-  | 4    |

| TX LANE3+ |       | 64  | Module XAUI Input Lane 3+  | 4    |

| TX LANE3- |       | 65  | Module XAUI Input Lane 3-  | 4    |

- 1) Ground connections are common for TX and RX.

- Each connector contact is rated at 0.5A.

- 2) 3) MDIO and MDC timing must comply with IEEE 802.3ae clause 45.3.

- XAUI output characteristics comply with IEEE 802.3ae clause 47.

- Transceivers will be MSA compliant when no signals are present on the vendor specific pins

# **Eye Safety**

This laser based multimode transceiver is a Class 1 product. It complies with IEC 60825-1: 2007 and FDA performance standards for laser products (21 CFR 1040.10 and 1040.11) except for deviations pursuant to Laser Notice 50, dated June 24, 2007.

#### **CLASS 1 LASER PRODUCT**

Caution: use of controls or adjustments or performance of procedures other than those specified herein may result in hazardous radiation.

Note: All adjustments have been made at the factory prior to shipment of the devices. No maintenance or alteration to the device is required. Tampering with or modifying the performance of the device will result in voided product warranty. Failure to adhere to the above restrictions could result in a modification that is considered an act of "manufacturing", and will require, under law, recertification of the modified product with the U.S. Food and Drug Administration (ref. 21 CFR 1040.10 (i)).

#### **Laser Emission Data**

| Wavelength                                                                      | 1310 nm            |

|---------------------------------------------------------------------------------|--------------------|

| Maximum total output power (as defined by IEC: 7 mm aperture at 70 mm distance) | 15.6 mW / 11.9 dBm |

| Beam divergence (full angle) / NA (half angle)                                  | 11° / 0.1 rad      |

## **Required Labeling**

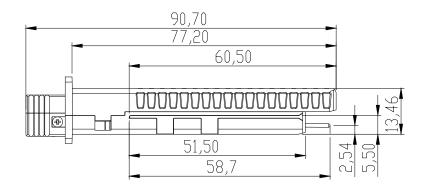

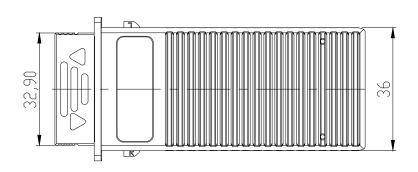

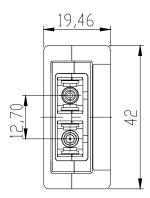

# **Mechanical Drawing**

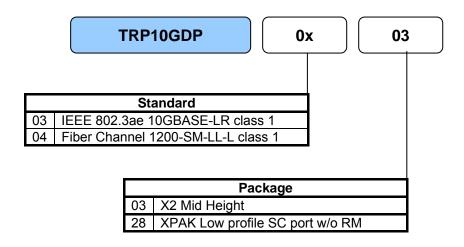

# **Order Information**

For further information please contact us at <a href="mailto:info@mergeoptics.com">info@mergeoptics.com</a> or visit our website www.mergeoptics.com.