# SM3E ULTRA MINIATURE STRATUM 3E MODULE

2111 Comprehensive Drive Aurora, Illinois 60505 Phone: 630-851-4722 Fax: 630-851-5040 www.conwin.com

## **Application**

The SM3E Timing Module is a complete system clock module for Stratum 3E timing applications and conforms to GR-1244-CORE (Issue 2), GR-253-CORE (Issue 3) and ITU-T G.812 (Option 3). Applications include shared port adapters, data digital cross connects, ADM's, DSLAM's, multiservice platforms, switches and routers in TDM, SDH and SONET environments.

The SM3E Timing Module guarantees full Stratum 3E compliance with a minimum of effort and cost in the smallest complete package available.

## **Features**

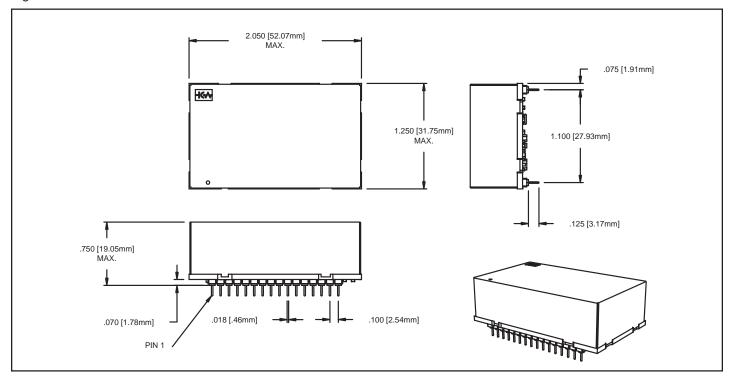

- Small Package Size,

2.05 x 1.25 x 0.75 inches

- Eight Auto Select Input References,

8 kHz - 77.76 MHz

- Phase Buildout

- Hitless Reference Switching

- Better than 1ppb initial Hold Over offset

- Frequency Qualification and Loss of Reference detection for each input

- Master/Slave Operation with Phase Adjustment

- Manual/Autonomous Operation

- Bi-Directional SPI Port Control and Status Reporting

- Three CMOS Frequency Outputs - Output1 from 1.544 - 77.76MHz, M/ S\_Out@8KHz, BITS @2.048 MHz or 1.544 MHz

- 3.3V operation

| Bulletin  | TM054     |

|-----------|-----------|

| Page      | 1 of 36   |

| Revision  | 02        |

| Date      | 07 Nov 08 |

| Issued By | ENG       |

## **General Description**

The SM3E timing module provides a clock output that meets or exceeds Stratum 3E specifications given in GR-1244-CORE (Issue 2), GR-253-CORE (Issue 3) and ITU-T G.812 (option 3). The SM3E features eight reference inputs. Each input will auto-detect the following reference frequencies: 8 kHz, 1.544 MHz, 2.048 MHz, 12.96 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz and 77.76 MHz.

The SM3E timing module can be configured during production to produce an output up to 77.76MHz. This output is derived from an onboard VCXO and must be specified when ordering. The second output is a BITS output selectable for either 1.544 or 2.048 MHz. The master/slave output is 8KHz. The user communicates with the SM3E module through a SPI port. The user controls the SM3E operation by writing to the appropriate registers. The user can also enable or disable SPI operation through a SPI Enable pin.

The SM3E offers a wide range of options for the system designer. The bandwidth is SPI Port-selectable from 0.00084 Hz to 1.6 Hz. 0.0016 Hz is the recommended operational bandwidth for Stratum 3E applications. The 8 kHz output has an adjustable pulse width. The pull-in range is also adjustable to establish the desired reference frequency rejection limits. A Free Run frequency calibration value can be written to the module to provide a high degree of accuracy in the free run mode. The reference frequency for any given reference input is automatically detected. A wealth of status information is available through the SPI Port registers. The user also has a choice between autonomous or full manual control operation.

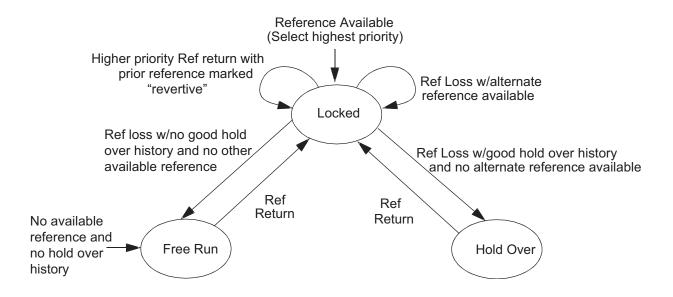

In manual mode, the user controls the module operating modes Free Run, Hold Over or locked to a specific reference. If the chosen reference is unavailable or disqualified the module automatically enters Hold Over.

In autonomous control mode, operational mode selection occurs automatically based on reference priority and qualification status. When the active reference becomes disqualified, the module will switch to another qualified reference. If none is available, it will switch to Hold Over. In the revertive mode the module will seek to acquire the highest priority qualified reference. In the non-revertive mode the module will not return to the previous reference even after it is re-qualified unless there are no other qualified references.

Switching between references is hitless. Likewise, the output frequency slew rate is minimized during any change of operating mode, including entry into and return from Free Run or Hold Over to protect traffic from transient-induced bit errors.

Reference Status information and the operating mode information is accessed through status registers. The module will set the Interrupt pin (SPI\_INT) low to indicate a status change.

Free Run operation guarantees an output within 4.6ppm of nominal frequency and Hold Over operation guarantees the output frequency will not change by more than 0.012ppm during the first 24 hours. Frequency accuracy is based on a precision oven to provide the stabilty required for Stratum 3E compliance.

The SM3E can be programmed to startup in any mode or bandwidth. The module may even be programmed to operate in a fully autonomous mode with no further configuration required.

The module operates on  $3.3V \pm 5\%$  with a typical power drain of less than 3W at turn on, dropping to approximately 1W @ room temperature after warming up. The module operates over the 0° to 70° C commercial temperature range.

Phase buildout can be enabled or disabled by means of the SPI port.

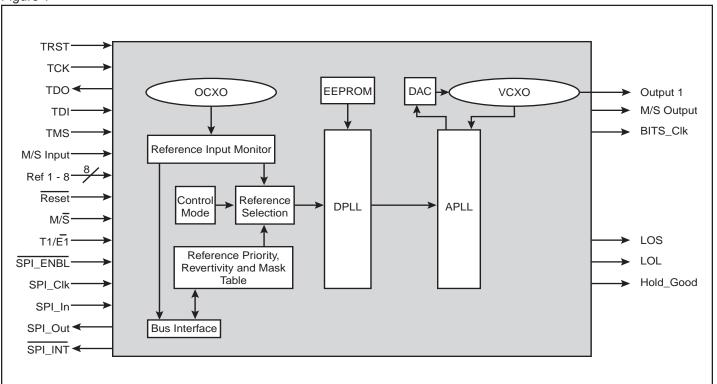

## **Functional Block Diagram**

Figure 1

Data Sheet #: TM054 Page 2 of 36 Rev: 02 Date: 11/07/08

# **Specifications for Ultra Miniature Stratum 3E**

## Table 1

| Parameter                                       | Specification                                               |  |  |

|-------------------------------------------------|-------------------------------------------------------------|--|--|

| Voltage                                         | 3.3V ± 5%                                                   |  |  |

| Power                                           | 3W Maximum during start up, 1.5W Typical @ room temperature |  |  |

| Reference Frequency 1 - 8                       | 8 kHz - 77.76 MHz (Determined by customer's application)    |  |  |

| CMOS Output Frequency #1<br>M/S_Out<br>BITS_CIk | 8 kHz - 77.76 MHz<br>8 kHz<br>1.544/2.048 MHz (Selectable)  |  |  |

| Master/Slave I/O                                | 8 kHz                                                       |  |  |

| Input Reference Pulse Width                     | 10 ns Min @ 8 kHz, 5 ns Min @ >8 kHz                        |  |  |

| Free Run Accuracy                               | 4.6 ppm                                                     |  |  |

| Hold Over Accuracy                              | 0.001 ppm                                                   |  |  |

| Hold Over Stability                             | 0.012 ppm for the first 24 hours                            |  |  |

| Dimensions                                      | 2.05 x 1.25 x 0.75 inches (52.07 x 31.75 x 19.05 mm)        |  |  |

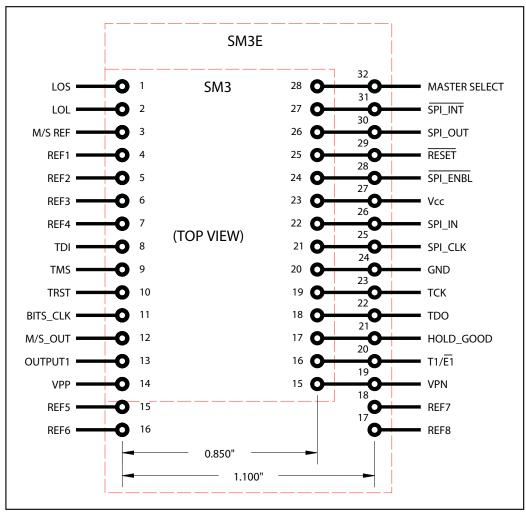

# **Pin Description**

## Table 2

| Pin# | 1/0 | Pin Name      | Pin Description                                                                                |

|------|-----|---------------|------------------------------------------------------------------------------------------------|

| 1    | 0   | LOS           | Alarm output - Loss of Active Reference Signal                                                 |

| 2    | 0   | LOL           | Alarm Output - Loss of Lock                                                                    |

| 3    |     | M/S REF       | Master/Slave 8 kHz reference input                                                             |

| 4    | I   | REF1          | Reference Input 1 – 8 kHz to 77.76 MHz auto detected                                           |

| 5    |     | REF2          | Reference Input 2 – 8 kHz to 77.76 MHz auto detected                                           |

| 6    | I   | REF3          | Reference Input 3 – 8 kHz to 77.76 MHz auto detected                                           |

| 7    |     | REF4          | Reference Input 4 – 8 kHz to 77.76 MHz auto detected                                           |

| 8    |     | TDI           | JTAG TDI pin                                                                                   |

| 9    |     | TMS           | JTAG TMS pin                                                                                   |

| 10   |     | TRST          | JTAG TRST pin                                                                                  |

| 11   | 0   | BITS_CLK      | 1.544 or 2.048 MHz output selected by pin 14                                                   |

| 12   | 0   | M/S_OUT       | Master/Slave 8 kHz output                                                                      |

| 13   | 0   | OUTPUT1       | Synchronous Primary Output                                                                     |

| 14   |     | VPP           | Positive Programming Supply Pin. During normal operation, It is recommended to float this pin. |

| 15   |     | REF5          | Reference Input 5 – 8 kHz to 77.76 MHz auto detected                                           |

| 16   |     | REF6          | Reference Input 6 – 8 kHz to 77.76 MHz auto detected                                           |

| 17   |     | REF8          | Reference Input 8 – 8 kHz to 77.76 MHz auto detected                                           |

| 18   |     | REF7          | Reference Input 7 – 8 kHz to 77.76 MHz auto detected                                           |

| 19   |     | VPN           | Negative Programming Supply Pin. During normal operation, It is recommended to float this pin. |

| 20   | _   | T1/E1         | BITS_CLK select input – 1=1.544 MHz, 0=2.048 MHz                                               |

| 21   | 0   | HOLD_GOOD     | Holdover Good Output Flag – 1=Holdover Available                                               |

| 22   |     | TDO           | JTAG TDO pin                                                                                   |

| 23   |     | TCK           | JTAG TCK pin                                                                                   |

| 24   |     | GND           | Module Ground                                                                                  |

| 25   |     | SPI_CLK       | SPI Port Clock input                                                                           |

| 26   | I   | SPI_IN        | SPI Port Data input                                                                            |

| 27   |     |               | 3.3 Vdc VCC Supply Input                                                                       |

| 28   | ı   | SPI_ENBL      | SPI Port Enable input – Active Low                                                             |

| 29   | I   | RESET         | Module Reset – Active Low                                                                      |

| 30   | 0   | SPI_OUT       | SPI Port Data Output                                                                           |

| 31   | 0   | SPI_INT       | SPI Port Interrupt Output                                                                      |

| 32   | I   | MASTER SELECT | Master/Slave select input – 1=Master, 0=Slave                                                  |

Data Sheet #: TM054 Page 3 of 36 Rev: 02 Date: 11/07/08

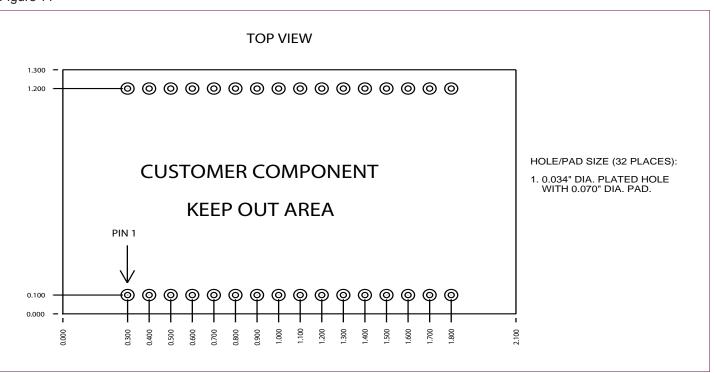

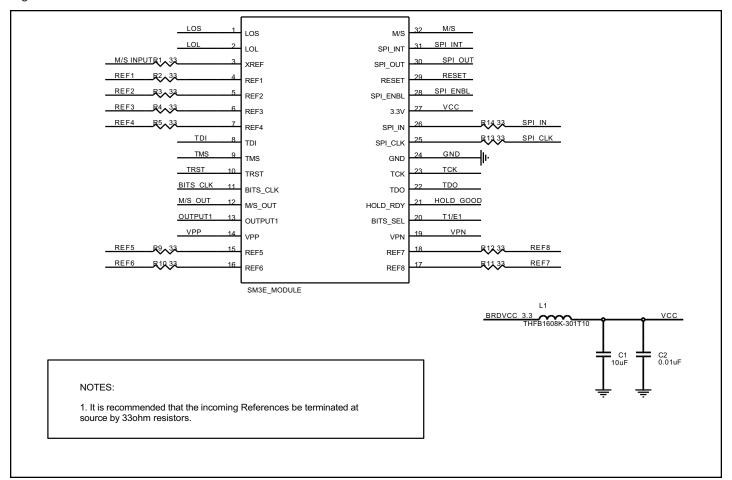

# **Pin Diagram**

Figure 2

|                                                                                         |                                                                                                                                                                                                   | SM3E       |    |                                                                                                                          |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|--------------------------------------------------------------------------------------------------------------------------|

| LOS LOL M/S REF REF1 REF2 REF3 REF4 TDI TMS TRST BITS_CLK M/S_OUT OUTPUT1 VPP REF5 REF6 | <ul> <li>1</li> <li>2</li> <li>3</li> <li>4</li> <li>5</li> <li>6</li> <li>7</li> <li>8</li> <li>9</li> <li>10</li> <li>11</li> <li>12</li> <li>13</li> <li>14</li> <li>15</li> <li>16</li> </ul> | (TOP VIEW) | 32 | MASTER SELECT  SPI_INT  SPI_OUT  RESET  SPI_ENBL  Vcc  SPI_IN  SPI_CLK  GND  TCK  TDO  HOLD_GOOD  T1/E1  VPN  REF7  REF8 |

# **Register Map**

Table 3

| Address | Reg Name           | Description                                                                                                                          |     |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0x00    | Chip_ID_Low        | Low byte of chip ID                                                                                                                  | R   |

| 0x01    | Chip_ID_High       | High byte of chip ID                                                                                                                 | R   |

| 0x02    | Chip_Revision      | Chip revision number                                                                                                                 | R   |

| 0x03    | Bandwidth_PBO      | Bandwidth & Phase Build-Out option                                                                                                   | R/W |

| 0x04    | Ctl_Mode           | Manual or automatic selection of Op_Mode,BITS clock output frequency indication, and frame/multi-frame sync pulse width mode control |     |

| 0x05    | Op_Mode            | Master Free Run, Locked, or Hold Over mode, or Slave mode                                                                            |     |

| 0x06    | Max_Pullin_Range   | Maximum pull-in range in 0.1 ppm units                                                                                               |     |

| 0x07    | M/S Input_Activity | Cross Reference activity                                                                                                             |     |

| 80x0    | Ref_Activity       | Activities of 8 reference inputs                                                                                                     |     |

| 0x09    | Ref_Pullin_Sts     | In or out of pull-in range of 8 reference inputs                                                                                     | R   |

| 0x0a    | Ref_Qualified      | Qualification of 8 reference inputs                                                                                                  | R   |

| 0x0b    | Ref_Mask           | Availability mask for 8 reference inputs                                                                                             | R/W |

Data Sheet #: TM054 Page 4 of 36 Rev: 02 Date: 11/07/08

# Register Map Continued Table 3

| 0x0c | Ref_Available     | Availability of 8 reference inputs                                                             | R   |

|------|-------------------|------------------------------------------------------------------------------------------------|-----|

| 0x0d | Ref_Rev_Delay     | Reference reversion delay time, 0 - 255 minutes                                                | R/W |

| 0x0e | Phase_Offset      | Phase offset between M/S REF & M/S Output (for the Slave in M/S operation) in 250ps resolution | R/W |

| 0x0f | Calibration       | Local oscillator digital calibration in 0.05 ppm resolution                                    | R/W |

| 0x10 | Fr_Pulse_Width    | Frame sync pulse width                                                                         | R/W |

| 0x11 | DPLL_Status       | Digital Phase Locked Loop status                                                               | R   |

| 0x12 | Intr_Event        | Interrupt events                                                                               | R   |

| 0x13 | Intr_Enable       | Enable individual interrupt events                                                             | R/W |

| 0x14 | Ref1_Frq_Offset   | Ref1 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x15 | Ref2_Frq_Offset   | Ref2 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x16 | Ref3_Frq_Offset   | Ref3 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x17 | Ref4_Frq_Offset   | Ref4 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x18 | Ref5_Frq_Offset   | Ref5 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x19 | Ref6_Frq_Offset   | Ref6 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x1a | Ref7_Frq_Offset   | Ref7 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x1b | Ref8_Frq_Offset   | Ref8 frequency offset in 0.2 ppm resolution                                                    | R   |

| 0x1c | Ref1_Frq_Priority | Ref1 frequency and priority                                                                    | R/W |

| 0x1d | Ref2_Frq_Priority | Ref2 frequency and priority                                                                    | R/W |

| 0x1e | Ref3_Frq_Priority | Ref3 frequency and priority                                                                    | R/W |

| 0x1f | Ref4_Frq_Priority | Ref4 frequency and priority                                                                    | R/W |

| 0x20 | Ref5_Frq_Priority | Ref5 frequency and priority                                                                    | R/W |

| 0x21 | Ref6_Frq_Priority | Ref6 frequency and priority                                                                    | R/W |

| 0x22 | Ref7_Frq_Priority | Ref7 frequency and priority                                                                    | R/W |

| 0x23 | Ref8_Frq_Priority | Ref8 frequency and priority                                                                    | R/W |

| 0x24 | FreeRun Priority  | Control and Priority for designation of Free Run as a reference                                | R/W |

| 0x25 | History_Policy    | Sets policy for Hold Over history accumulation                                                 | R/W |

| 0x26 | History_CMD       | Save, restore and flush comands for Hold Over history                                          | R/W |

| 0x27 | HoldOver_Time     | Indicates the time since entering Hold Over state                                              | R   |

| 0x30 | Cfgdata           | Configuration data write register                                                              | R/W |

| 0x31 | Cfgctr_Lo         | Configuration data write counter, low byte                                                     | R   |

| 0x32 | Cfgctr_Hi         | Configuration data write counter, high byte                                                    | R   |

| 0x33 | Chksum            | Configuration data checksum pass/fail indicator                                                | R   |

| 0x35 | EE_Wrt_Mode       | Disables/Enables writing to the external EEPROM                                                | R/W |

| 0x37 | EE_Cmd            | Read/Write command & ready indication register for ext. EEPROM access                          | R/W |

| 0x38 | EE_Page_Num       | Page number for external EEPROM access                                                         | R/W |

| 0x39 | EE_FIFO_Port      | Read/Write data for external EEPROM access                                                     | R/W |

## **Detailed Description**

The SM3E utilizes up to 8 external references, each from 8 kHz to 77.76 MHz, may be equipped and monitored for signal presence and frequency offset. Additionally, a cross-couple 8 kHz reference input is provided for master/slave operation. Reference selection may be manual or automatic, according to pre-programmed priorities. All reference switches are performed in a hitless manner, and frequency ramp controls ensure smooth output signal transitions. When references are switched, the device provides a controllable phase build-out to minimize phase transitions in the output clocks.

Three output signals are provided, the first up to 77.76 MHz, the second fixed at 8 kHz for use as a frame sync signal as well as a cross-couple reference for master/slave operation. In slave mode, the output phase may be adjusted from -32 to +31.75nS relative to the master, to accommodate downstream system needs, such as different clock distribution path lengths. The third output is a BITS clock, selectable as either 1.544 MHz or 2.048 MHz.

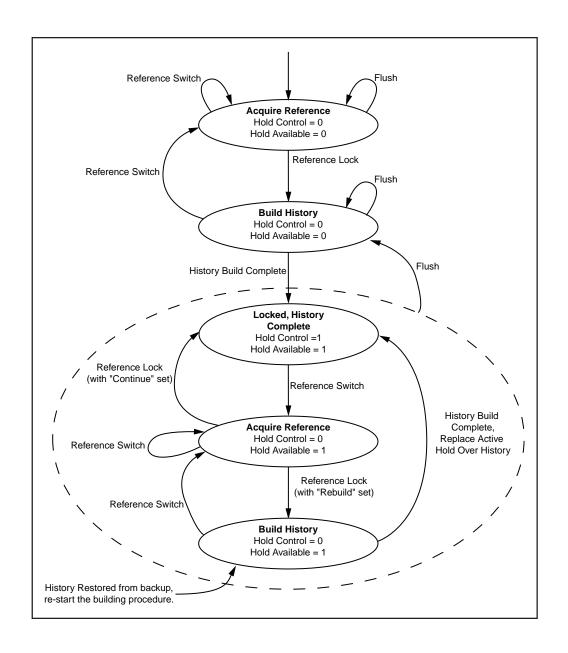

Device operation may be in Free Run, locked, or Hold Over modes. In Free Run, the clock outputs are simply determined by the Free Run frequency and accuracy of the calibrated internal clock. In locked mode, the chip phase locks to the selected input reference. While locked, a frequency history is accumulated. In Hold Over mode, the chip outputs are generated according to this history.

The Digital Phase Locked Loop provides critical filtering and frequency/phase control functions that meet or exceed all requirements in critical jitter and accuracy performance parameters. Filter bandwidth may be configured to suit applications requirements.

Control functions are provided via standard SPI bus register interface. Register access provides visibility into a variety of registered information as well as providing extensive programmable control capability.

#### Operating Modes: The SM3E Operates in Either Free Run, Locked, or Hold Over Mode:

Free Run – In Free Run mode, Output 1, M/S\_Out, and BITS\_CIk, the output clocks, are determined directly from and have the accuracy of the calibrated free running internal clock. Reference inputs continue to be monitored for signal presence and frequency offset, but are not used to synchronize the outputs.

**Locked** – The **Output 1**, **M/S\_Out**, and **BITS\_CIk**, outputs are phase locked to and track the selected input reference. Upon entering the Locked mode, the device begins an acquisition process that includes reference qualification and frequency slew rate limiting, if needed. Once satisfactory lock is achieved, the "Locked" bit is set in the DPLL\_Status register, and a compilation of the frequency history of the selected reference is started. When a usable Hold Over history has been established, the **Hold\_Good** pin is set, and the "Hold Over Available" bit is set in the **DPLL\_Status** register.

Phase comparison and phase lock loop filtering operations in the SM3E are completely digital. As a result, device and loop behavior are entirely predictable, repeatable, and extremely accurate. Carefully designed and proven algorithms and techniques ensure completely hitless reference switches, operational mode changes, and master/slave switches.

Basic loop bandwidth is programmable from 0.84 mHz to 1.6 Hertz, giving the user a wide range of control over the system response.

When a new reference is acquired, maximum frequency slew limits ensure smooth frequency changes. Once lock is achieved, (<700 seconds for Stratum 3E), the "Locked" bit is set. If the SM3E is unable to maintain lock, Loss of Lock (LOL) is asserted. All transitions between locked, Hold Over and Free Run modes are performed with minimal phase events and smooth frequency and phase transitions.

Reference phase hits or phase differences encountered when switching references (or when entering locked mode) are nulled out with an automatic phase build-out function. Phase build-out is performed with a residual phase error of less than 1 nS, and can optionally be disabled for hits on the selected reference, as required for Stratum 3E.

Hold Over — Upon entering Hold Over mode, the Output 1, M/S\_Out, and BITS\_CIk, outputs are determined from the Hold Over history established for the last selected reference. Output frequency is determined by a weighted average of the Hold Over history, and accuracy is determined by the internal clock. Hold Over mode may be entered manually or automatically. Automatic entry into Hold Over mode occurs when operating in the automatic mode, the reference is lost, and no other valid reference exists. The transfer into and out of Hold Over mode is designed to be smooth and free of transients. The frequency slew is also limited to a maximum of ±2 ppm/sec.

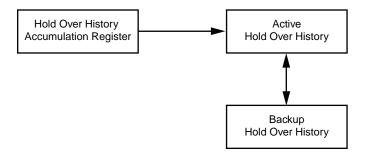

The history accumulation algorithm uses a first order frequency difference filtering algorithm. Typical holdover accumulation takes about 15 minutes. When a usable holdover history has been established, the **Hold\_Good** pin is set, and the "Holdover Available" bit is set in the **DPLL Status** register. The holdover history continues to be updated after "Holdover Available" is declared.

The algorithm accumulates the holdover history only when it has locked on either an external reference in Master operation or the **M/S Ref** clock in Slave operation, starting 15 minutes after power up. Tracking will be suspended automatically when switching to a new reference and in Free Run or Hold Over mode. A set of registers allows the application to control a holdover history maintenance policy, enabling either a re-build or continuance of the history when a reference switch occurs.

Data Sheet #: TM054 Page 6 of 36 Rev: 02 Date: 11/07/08

## **Detailed Description continued**

Furthermore, under register access control, a backup holdover history register is provided. It may be loaded from the active holdover history or restored to the active holdover history. The active holdover history may also be flushed.

Holdover mode may be entered at any time. If there is no holdover history available, the prior output frequency will be maintained. When in holdover, the application may read (via register access) the time since holdover was enterred.

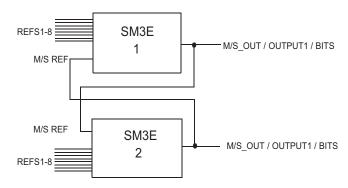

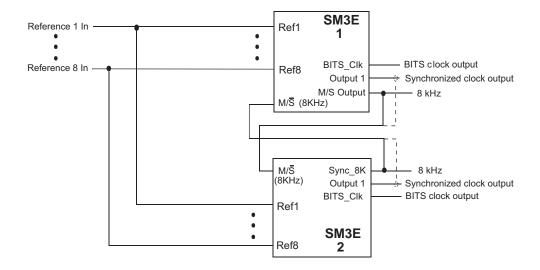

#### Master/Slave Operation

Pairs of SM3E devices may be operated in a master/slave configuration for redundant timing source applications. A typical configuration is shown below.:

# **Master / Slave Configuration**

Figure 3

The M/S Output or the Output 1 of each device may be cross-connected to the other device's M/S Ref input. The device auto-detects the frequency on the M/S Ref input. Master or slave state of a device is determined by the M/S pin. Thus, master/slave state is always manually controlled by the application. The master synchronizes to the selected input reference, while the slave synchronizes to the M/S Ref input. (Note that 8kHz frame phase alignment is maintained across a master/slave pair of devices only if M/S Output is used as the cross couple signal.)

The unit operating in slave mode locks on and phase-aligns to the cross-reference clock (M/S Output or Output 1) from the unit in master mode. The phase skew between the input cross-reference and the output clock for the slave unit is typically less than ±1ns (under ±3ns in dynamic situations, including reference jitter and wander).

Perfect phase alignment of the two Output 1 output clocks would require no delay on the cross-reference clock connection. To accommodate path length delays, the SM3E provides a programmable phase skew feature. The slave's Output 1 or M/S Output may be phase shifted -32nS to +31.75nS relative to M/S Input according to the contents of the MS\_Phase\_Offset register to compensate for the path length of the M/S Output or Output 1 to M/S Input connection. This offset may therefore be programmed to exactly compensate for the actual path length delay associated with the particular application's cross-reference traces. The offset may further be adjusted to accommodate any output clock distribution path delay differences. Thus, master/slave switches with the SM3 devices may be accomplished with near-zero phase hits.

The first time a unit becomes a slave, such as immediately after power-up, its output clock phase starts out arbitrary, and will quickly phase-align to the cross-reference from the master unit. The phase skew will be eliminated (or converged to the programmed phase offset) step by step. The whole pull-in-and-lock process will complete in about 60 seconds. There is no frequency slew protection in slave mode. In slave mode, the unit's mission is to lock to and follow the master.

Once a pair of units has been operating in aligned master/slave mode, and a master/slave switch occurs, the unit that becomes master will maintain its output clock phase and frequency while a phase build-out (to the current output clock phase) is performed on its selected reference input. Therefore, as master mode operation commences, there will be no phase or frequency hits on the clock output.

Likewise, the unit that becomes the slave will maintain its output clock frequency and phase for 1 msec before starting to follow the cross-reference, protecting the downstream clock users during the switch. Assuming the phase offset is programmed for the actual propagation delay of this cross-reference path, there will again be no phase hits on the output clock of the unit that has transitioned from master to slave.

Data Sheet #: TM054 Page 7 of 36 Rev: 02 Date: 11/07/08

## **Detailed Description continued**

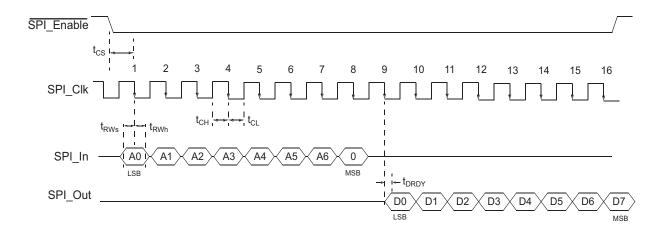

#### **Serial Communication**

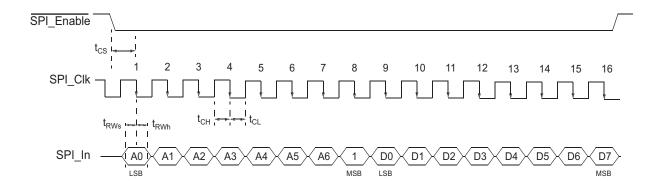

The user can control the operation of the SM3E module through the SPI port. Timing diagrams are shown below. When SPI\_ENABLE is high, SPI\_OUT is in a Tri-state mode.

# Serial Interface Timing, Read Access Figure 4

# Serial Interface Timing, Write Access Figure 5

Data Sheet #: TM054 Page 8 of 36 Rev: 02 Date: 11/07/08

## **Serial Interface Timing**

#### Table 4

| Symbol                 | Parameter                          | Minimum     | Nominal | Maximum | Units | Notes |

|------------------------|------------------------------------|-------------|---------|---------|-------|-------|

| t <sub>cs</sub>        | SPI_Enable low to SPI_CLK low      | 15          | -       | -       | ns    |       |

| <b>t</b> <sub>CH</sub> | SPI_CLK high time                  | 25          | -       | -       | ns    |       |

| t <sub>CL</sub>        | SPI_CLK low time                   | 25          | -       | -       | ns    |       |

| t <sub>RWs</sub>       | Read/Write setup time              | 15          | -       | -       | ns    |       |

| t <sub>RWh</sub>       | Read/Write hold time               | 15          | -       | -       | ns    |       |

| t <sub>DRDY</sub>      | Data ready                         | -           | -       | 25      | ns    |       |

| t <sub>HLD</sub>       | Data Hold                          | 15          | -       | -       | ns    |       |

| t <sub>CSTRI</sub>     | Chip Select to data tri-state      | 5           | -       | -       | ns    |       |

| t <sub>CSMIN</sub>     | Minimum delay between successive a | accesses300 | -       | -       | ns    |       |

Note: The SPI port should not be accessed until 1200ms after reset has transitioned from low to a high state.

#### **Reference Input Quality Monitoring**

Each reference input is monitored for signal presence and frequency offset. Signal presence for the **Ref1-8** inputs is indicated in the **Ref\_Activity** register and signal presence for the **M/S REF** is indicated in bit 0 of the **M/S REF\_Activity** register. The frequency offset between the **Ref1-8** inputs and the calibrated local oscillator is available in the **Ref\_Frq\_Offset** registers (8). Register **Ref\_Pullin\_Sts** indicates, for each of the **Ref1-8** inputs, if the reference is within the maximum pull-in range. The maximum pull-in range is indicated in register **Max\_Pullin\_Range**, and may be set in 0.1ppm increments. Typically, it would be set according to the values specified by the standards (GR-1244) appropriate for the particular stratum of operation.

The Ref\_Qualified register contains the "anded" condition of the Ref\_Activity and Ref\_Pullin\_Sts registers for each of the Ref1-8 inputs, qualified for 10 seconds. When a reference signal has been present for > 10 seconds and is within the pull-in range, it's bit is set.

The **Ref\_Available** register contains the "anded" condition of the **Ref\_Qualified** register and the **Ref\_Mask** register, and therefore represents the availability of a reference for selection when automatic reference and operational mode selection is enabled.

#### Reference Input Selection, Frequencies, and Mode Selection

One of eight reference input signals (**Ref 1-8**) are selected for synchronization in Master mode (as below in the **Op\_Mode** register description. 0x05). **Ref 1-8** may each be 8 kHz, 1.544 MHz, 2.048 MHz, 12.96 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz or 77.76 MHz.

Reference frequencies are auto-detected and the detected frequency can be read from the **Ref\_Frq\_Priority** registers (See **Register Descriptions and Operation** section).

Active reference and operational mode selection may be manual or automatic, as determined by bit 1 in the **Ctl\_Mode** register. In manual mode, register writes to **Op\_Mode** select the reference and mode. The reset default is manual mode.

The M/S REF input for slave operation is frequency auto-detected and may be 8kHz, 1.544MHz, 2.048MHz, 12.96MHz, 19.44MHz, 25.92MHz, 38.88MHz, 51.84MHz or 77.76MHz. Signal presence and frequency for the M/S REF input is indicated in bits 0-3 of the **M/S REF Activity** register.

In automatic mode, the reference is selected according to the priorities written to the eight Ref\_Frq\_Priority registers. Individual references may be masked for use/non-use according to the Ref\_Mask register. A reference may only be selected if it is "available" - that is, it is qualified, as indicated in the Ref\_Qualified register, and is not masked (See Reference Input Quality Monitoring and Register Descriptions and Operation sections).

Furthermore, Bit 3 of each **Ref\_Frq\_Priority** register will determine if that reference is revertive or non-revertive. When a reference fails, the next highest priority "available" (signal present, non-masked, and acceptable frequency offset) reference will be selected. When a reference returns, it will be switched to only if it is of higher priority and the current active reference is marked "Revertive". Additionally, the reversion is delayed according to the value written to the **Ref\_Rev\_Delay** register (From 0 to 255 minutes).

Data Sheet #: TM054 Page 9 of 36 Rev: 02 Date: 11/07/08

## **Detailed Description continued**

The automatic reference selection is shown in the following state diagram:

#### **Automatic Reference Selection** Figure 6 Stay Locked on Ref m time for t= Ref Rev Delay Ref\_Rev\_Delay Ref n returns, Ref n returns. time expired Ref m marked Ref m marked "revertive" "non-revertive" Select & Loss of Ref n Locked Lock on on Ref n Select new reference: Ref m Next highest priority. Qualified (within max. pull-in range, signal present > 10 sec.),

Non-masked

The operational mode is according to the following state diagram:

No available reference and no Hold Over history Ref loss w/no good Hold Over history and no other available reference

# Automatic Operational Mode Selection Figure 7

Data Sheet #: TM054 Page 10 of 36 Rev: 02 Date: 11/07/08

## **Detailed Description continued**

#### **Output Signals and Frequency**

**Output 1** is the primary chip output, and in locked mode is synchronized to the selected reference. **Output 1** may be any of the following frequencies: 12.96 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz or 77.76 MHz.

M/S\_Out is an 8 kHz output available as a frame reference or synchronization signal for cross-coupled pairs of SM3E devices operated in master/slave mode. In master mode, M/S\_Out is synchronized to the selected reference. In slave mode, M/S\_Out is in phase with the M/S REF offset by the value written to the Phase\_offset register (+31.75 to -32nS, with .25nS resolution). M/S\_Out may be a 50% duty cycle signal, or variable high-going pulse width, as determined by the Ctl\_Mode and Fr\_Pulse\_Width registers. In variable pulse width mode, the width may be from 1 to 15 multiples of the Output 1 cycle time. See Register Descriptions and Operation section.

BITS\_Clk is the BITS clock output at either 1.544 MHz or 2.048 MHz. It is selected by the T1/E1 input and its state may be read in bit

BITS\_CIk is the BITS clock output at either 1.544 MHz or 2.048 MHz. It is selected by the T1/E1 input and its state may be read in bit 3 of the Ctl\_Mode register. When T1/E1 = 1, the BITS frequency is 1.544 MHz, and when T1/E1 = 0, the BITS frequency is 2.048 MHz.

#### Interrupts

The SM3E module supports eight different interrupts and appears in INTR\_EVENT (0x12) register. Each interrupt can be individually enabled or disabled via the INTR\_ENABLE (0x13) register. Each bit enables or disables the corresponding interrupt from asserting the SPI\_INT pin. Interrupt events still appear in the INTR\_EVENT (0x12) register independent of their enable state. All interrupts are cleared once INTR\_EVENT (0x12) register is read. The interrupts are:

- Any reference changing from available to not available

- Any reference changing from not available to available

- M/S REF changing from activity to no activity

- M/S REF changing from no activity to activity

- DPLL Mode status change

- Reference switch in automatic reference selection mode

- Loss of Signal

- Loss of Lock

#### Interrupts and Reference Change in Autonomous Mode

Interrupts can be used to determine the cause of a reference change in autonomous mode. Let us assume that the module is currently locked to REF1. The module switches to REF2 and SPI\_INT pin is asserted. The user reads the INTR\_EVENT (0x12) register.

If the module is operating in autonomous non-revertive mode, the cause can be determined from bits 4, 5, 6 and 7. Bit 5 is set to indicate Active reference change. If Bit 6 is set then the cause of the reference change is Loss of Active Reference. If Bit 7 is set then the cause of the reference change is a Loss of Lock alarm on the active reference.

If the module is operating in autonomous revertive mode, the cause can be determined from bits 1, 4,5, 6 and 7. Bit 5 is set to indicate Active reference change. If Bit 6 is set then the cause of the reference change is Loss of Active Reference. If Bit 7 is set then the cause of the reference change is a Loss of Lock alarm on the active reference. If Bit 1 is set then the cause of the reference change is the availability of a higher priority reference.

<u>Note</u>: The DPLL Mode Status Change bit (Bit 4) is also set to indicate a change in **DPLL\_STATUS (0x11)** register, during an interrupt caused by a reference change. The data in **DPLL\_STATUS (0x11)** register however is not useful in determining the cause of a reference change. This is because bits 0-2 of this register always reflects the status of the current active reference and hence cannot be used to determine the status of the last active reference.

#### **Interrupts in Manual Mode**

In manual operating mode, when the active reference fails due to a Loss of Signal or Loss of Lock alarm, an interrupt is generated. For example, in case of a Loss of Signal, bits4 and 6 of INTR\_EVENT (0x12) register would be set to indicate Loss of Signal and DPLL Mode Status Change. The user may choose to read the DPLL\_STATUS (0x11) register, though in manual mode bit6 of INTR\_EVENT (0x12) register is a mirror of bit0 of DPLL\_STATUS (0x11) register. This holds true for a Loss of Lock alarm, where bit7 of INTR\_EVENT (0x12) register is a mirror of bit1 of DPLL\_STATUS (0x11) register.

## **Internal Clock Calibration**

The internal clock may be calibrated by writing a frequency offset v.s. nominal frequency into the Calibration register. This calibration is used by the synchronization software to create a frequency corrected from the actual internal clock output by the value written to the Calibration register. See register descriptions.

Data Sheet #: TM054 Page 11 of 36 Rev: 02 Date: 11/07/08

## **Register Descriptions and Operation**

Chip\_ID\_low, 0x00 (R)

| 1= = / (/                  |               |  |

|----------------------------|---------------|--|

|                            | Bit 7 ~ Bit 0 |  |

| Low byte of chip ID: 0x11  |               |  |

|                            |               |  |

| Chip_ID_High, 0x01 (R)     |               |  |

|                            | Bit 7 ~ Bit 0 |  |

| High byte of chip ID: 0x30 |               |  |

| Chip_Revision, 0x02 (R)    |               |  |

|                            | Bit 7 ~ Bit 0 |  |

## Bandwidth\_PBO, 0x03 (R/W)

Chip revision number: 0x02

| Bit 7 ~ Bit 5 | Bit 4                                                   | Bit 3 ~ Bit 0                                                                                                                                                                                     |

|---------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved      | Phase Build-out Option: 1: Enable 0: Disable Default: 1 | Bandwidth Selection in Hz: 0000: 0.00084 0001: 0.0016 0010: 0.0032 0011: 0.0063 0100: 0.012 0101: 0.025 0110: 0.049 0111: 0.098 (Reset Default) 1000: 0.20 1001: 0.39 1010: 0.78 1011 - 1111: 1.6 |

BITS 3 - 0 select the phase lock loop bandwidth in Hertz. The reset default is 0.098 Hz. Bit 4 enables or disables phase build-out for active reference phase hits. Phase build-out operation requires register access operation of the device.

#### Ctl\_Mode, 0x04 (R/W)

| Bit 7 ~ Bit 6 | Bit 5      | Bit 4                                                                                      | Bit 3                                                                             | Bit 2                                                                     | Bit 1                                                         | Bit 0    |

|---------------|------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------|----------|

| Reserved      | Default: 0 | M/S Output Pulse width control: 0: 50% 1: Controlled by FR_Pulse_Width register Default: 0 | BITS Clock<br>Output<br>Frequency:<br>1: 1.544 MHz<br>0: 2.048 MHz<br>(read only) | HM Ref:<br>0: Register control<br>of op mode/ref<br>(Will always<br>be 0) | Active Reference Selection: 1: Manual 0: Automatic Default: 1 | Reserved |

When bit 1 is reset (automatic reference and mode selection), Bits 3 - 0 of the **Op\_Mode** register become read-only. The power-up default for Bit 1 = 1 for manual reference selection and default for Bit 4 = 0 for 50% duty cycle on **M/S Output.**

When the device is in slave mode, it will lock to the **M/S REF**, independent of the values written to BITS 3 - 0 of the **Op\_mode** register. The operational mode and reference selection written to Bits 3 - 0 while in slave mode will, however, take effect when the device is made the master.

When bit 1 of the **Ctl\_Mode** register is reset (automatic reference and mode selection) and the device is in master mode, BITS 3 - 0 of the **Op\_Mode** register become read-only.

Data Sheet #: TM054 Page 12 of 36 Rev: 02 Date: 11/07/08

## Op\_Mode, 0x05 (R/W)

| Bit 7 ~ Bit 5 | Bit 4                                               | Bit 3 ~ Bit 0                                                                                                                                                                                                               |

|---------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved      | Master or Slave Mode 1: Master 0: Slave (Read Only) | Free Run, Locked, or Hold Over: 0000: Free Run mode 0001: Locked on Ref1 0010: Locked on Ref2 0011: Locked on Ref3 0100: Locked on Ref4 0101: Locked on Ref5 0110: Locked on Ref6 0111: Locked on Ref7 1000: Locked on Ref8 |

#### Max\_Pullin\_Range, 0x06 (R/W)

Bit 7 ~ Bit 0

Maximum pull-in range in 0.1 ppm unit

This register should be set according to the values specified by the standards (GR-1244) appropriate for the particular stratum of operation. The power-up default value is 10 ppm. (= 4.6ppm aging + 4.6 ppm pullin + margin).

## M/S REF\_Activity, 0x07 (R)

| Bit 7 ~ Bit 4 | Bit 3 ~ Bit 0                                                                                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved      | Cross reference activity 0000: No signal 0001: 8kHz 0100: 12.96MHz 0101: 19.44MHz 0110: 25.92MHz 0111: 38.88MHz 1000: 51.84MHz 1001: 77.76MHz 1010-1111: Reserved |

Indicates signal presence and auto-detected frequency for the M/S REF input.

## Ref\_Activity, 0x08 (R)

| Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| ref8 activity | ref7 activity | ref6 activity | ref5 activity | ref4 activity | ref3 activity | ref2 activity | ref1 activity |

| 1: on         |

| 0: off        |

Each bit indicates the presence of a signal for that reference.

Data Sheet #: TM054 Page 13 of 36 Rev: 02 Date: 11/07/08

## Ref\_Pullin\_Sts, 0x09 (R)

| Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| ref8 sts     | ref7 sts     | ref6 sts     | ref5 sts     | ref4 sts     | ref3 sts     | ref2 sts     | ref1 sts     |

| 1: in range  |

| 0: out range |

Each bit indicates if the reference is within the frequency range specified by the value in the Max Pullin register.

#### Ref\_Qualified, 0x0a (R)

| Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| ref8 qual:    | ref7 qual:    | ref6 qual:    | ref5 qual:    | ref4 qual:    | ref3 qual:    | ref2 qual:    | ref1 qual:    |

| 1: avail.     |

| 0: not avail. |

This register contains the "anded" condition of the **Ref\_Activity** and **Ref\_Pullin\_Sts** registers for each of the **Ref1-8** inputs, qualified for 10 seconds. When a reference signal has been present for > 10 seconds and is within the pull-in range, its bit is set.

#### Ref\_Mask, 0x0b (R/W)

| Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| ref8 mask:    | ref7 mask:    | ref6 mask:    | ref5 mask:    | ref4 mask:    | ref3 mask:    | ref2 mask:    | ref1 mask:    |

| 1: avail.     |

| 0: not avail. |

| Default: 0    |

Individual references may be marked as "available" or "not available" for selection in the automatic reference selection mode (bit 1 = 0 in the **Ctl\_Mode** register). The reset default value is 0, "not available". In manual reference selection, either hardware or register controlled, the reference masks have no effect, but do remain valid and are applied upon a transition to automatic mode.

#### Ref\_Available, 0x0c (R)

| Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0       |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-------------|

| ref8 avail:   | ref7 avail:   | ref6 avail:   | ref5 avail:   | ref4 avail:   | ref3 avail:   | ref2 avail:   | ref1 avail: |

| 1: avail.     | 1: avail.   |

| 0: not avail. | 0: not      |

This register contains the "anded" condition of the Ref Qualified and Ref Mask registers.

## Ref\_Rev\_Delay, 0x0d (R/W)

Bit 7 ~ Bit 0

Reference reversion delay time, 0 - 255 minutes. default = 0000 0101, 5 minutes

In automatic reference selection mode, when a reference fails and later returns, it must be available for the time specified in the Ref\_Rev\_Delay register before it can be switched back to as the active reference (if the new reference was marked as "revertive").

Data Sheet #: TM054 Page 14 of 36 Rev: 02 Date: 11/07/08

#### Phase\_Offset, 0x0e (R/W)

Bit 7 ~ Bit 0

The 2's complement value of phase offset between Master Output module and Slave Output module, ranges from -32 nS to +31.75 nS

Positive Value: Master Output rising edge leads Slave Output Negative Value: Master Output rising edge lags Slave Output

In slave mode, the slave's outputs may be phase shifted -32nS to +31.75nS in .25nS increments, relative to **M/S** according to the contents of the **Phase\_Offset** register, to compensate for the path length of the **M/S** to **M/S** connection.

If a phase offset is used, then the two SM3E devices would typically be written to the appropriate phase offset values for the respective path lengths of each Master to Slave connection, to ensure that the same relative output signal phases will persist through master/slave switches.

#### Calibration, 0x0f (R/W)

Bit 7 ~ Bit 0

2's complement value of local oscillator digital calibration in 0.05 ppm resolution

To digitally calibrate the free running clock synthesized from the internal clock, this register is written with a value corresponding to the known frequency offset of the oscillator from the nominal center frequency.

#### Fr\_Pulse\_Width, 0x10 (R/W)

| Bit 7 ~ Bit4 | Bit 3 ~ Bit 0                                                                  |

|--------------|--------------------------------------------------------------------------------|

| Reserved     | Pulse width for M/S clock output, 1-15 multiples of the Sync_Clk clock period. |

BITS 4 and 5 of the **Ctl\_Mode** register determine if the **M/S** 8 kHz output is 50% duty cycle or pulsed (high going) outputs. When they are pulsed, the **Fr\_Pulse\_Width** register determines the width. Width is the register value multiple of the **Sync\_Clk** clock period. Valid values are 1 - 15.

Reset default is 0001. Writing to 0000 maps to 0001.

## DPLL\_Status, 0x11 (R)

| Bit 7 ~Bit 5 | Bit 4                                              | Bit 3                                                | Bit 2                                | Bit 1                                           | Bit 0                                                                                 |

|--------------|----------------------------------------------------|------------------------------------------------------|--------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------|

| Reserved     | Hold Over Build Complete 1: Complete 0: Incomplete | Hold Over<br>Available<br>1: Avail.<br>0: Not avail. | Locked<br>1: Locked<br>0: Not locked | Loss of Lock 1: Loss of Lock 0: No loss of lock | Loss of Signal  1: No activity on active reference 0: Active reference signal present |

Bit 0 indicates the presence of a signal on the selected reference.

Bit 1 indicates a loss of lock (LOL). Loss of lock will be asserted if lock is not achieved within the specified time for the stratum level of operation, or lock is lost after being established previously. LOL will not be asserted for automatic reference switches.

Bit 2 indicates successful phase lock. It will typically be set in <700 seconds for Stratum 3E with a good reference. It will indicate "not locked" if lock is lost.

Bit 3 indicates if a Hold Over history is available.

Bit 4 indicates when a new Hold Over history has been successfully built and transferred to the active Hold Over history. See **Detailed Description** section under **Interrupts and Reference Change in Autonomous Mode** and **Interrupts in Manual Mode**

Data Sheet #: TM054 Page 15 of 36 Rev: 02 Date: 11/07/08

## Intr\_Event, 0x12 (R)

| Bit 7           | Bit 6             | Bit 5                   | Bit 4                         | Bit 3                                                | Bit 2                                                | Bit 1                                                                | Bit 0                                                       |

|-----------------|-------------------|-------------------------|-------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|

| Loss of<br>Lock | Loss of<br>Signal | Active reference change | DPLL Mode<br>status<br>change | M/S Ref<br>Change from<br>no activity to<br>activity | M/S Ref<br>Change from<br>activity to no<br>activity | Any refer-<br>erence change<br>from not<br>available to<br>available | Any refererence change from available able to not available |

Interrupt state = 1. When an enabled interrupt occurs, the SPI\_INT pin is asserted, active low. All interrupts are cleared and the SPI\_INT pin pulled high when the register is read. Reset default is 0. See Detailed Description section under Interrupts and Reference Change in Autonomous Mode and Interrupts in Manual Mode

#### Intr\_Enable, 0x13 (R/W)

| Bit 7                      | Bit 6                                                              | Bit 5                                                     | Bit 4                                                     | Bit 3                                                     | Bit 2                                                     | Bit 1                                                                   | Bit 0                                                     |

|----------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|

| rupt event 7:<br>1: Enable | Enable Interrupt event 6:<br>1: Enable<br>0: Disable<br>Default: 0 | Enable Interrupt event 5: 1: Enable 0: Disable Default: 0 | Enable Interrupt event 4: 1: Enable 0: Disable Default: 0 | Enable Interrupt event 3: 1: Enable 0: Disable Default: 0 | Enable Interrupt event 2: 1: Enable 0: Disable Default: 0 | Enable Inter-<br>rupt event 1:<br>1: Enable<br>0: Disable<br>Default: 0 | Enable Interrupt event 0: 1: Enable 0: Disable Default: 0 |

Enables or disables the corresponding interrupts from asserting the **SPI\_INT** pin. Interrupt events still appear in the **Intr\_Event** register independent of their "enable" state. Reset default is interrupts disabled.

#### Ref(1-8)\_Frq\_Offset, $0x14 \sim 0x1b$ (R)

Bit 7 ~ Bit 0

2's complement value of frequency offset between reference and calibrated local oscillator, 0.2ppm resolution

These registers indicate the frequency offset, in 0.2ppm resolution, between each reference and the local calibrated oscillator. 0x14 - 0x1b correspond to **Ref1 - Ref8**.

#### Ref(1-8)\_Frq\_Priority, $0x1c \sim 0x23$ (R/W)

| Bit 7 ~ Bit 4                                                                                                                                                                        | Bit 3                                                               | Bit 2 ~ Bit 0                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------|

| Frequency 0000: None 0001: 8 kHz 0010: 1.544 MHz 0011: 2.048 MHz 0100: 12.96 MHz 0101: 19.44 MHz 0110: 25.92 MHz 0111: 38.88 MHz 1000: 51.84 MHz 1001: 77.76 MHz 1010-1111: Reserved | Revertivity 1: revertive 0: non-revertive Default: 0, non revertive | Priority 0: highest 7: lowest Default: 0 |

BITS 2 - 0 indicate the priority of each reference for use in automatic reference selection mode (bit 1 of the **Ctl\_Mode** register =0). In manual reference selection mode (bit 1 of the **Ctl\_Mode** register = 1), these BITS are read-only and will contain either the reset default or values written when last in automatic reference selection mode. For equal priority values, lower reference numbers have higher priority.

Bit 3 specifies if the reference is revertive or non-revertive in automatic reference selection mode. When a reference fails, the next highest priority "available" (signal present, non-masked, and acceptable frequency offset) reference will be selected. When a reference returns, it will be switched to only if it is of higher priority and the current active reference is marked "Revertive".

BITS 7 - 4 indicate the auto-detected frequency for each reference. Invalid frequencies may result in erroneous device operation. If there is no activity on a reference, bits 7-4will be = 0000. Bits 7-4 are read only. 0x1c - 0x23 correspond to **Ref1 - Ref8**.

Data Sheet #: TM054 Page 16 of 36 Rev: 02 Date: 11/07/08

## FreeRun\_Priority, 0x24 (R/W)

| Bit 7 - Bit 5 | Bit 4                                                       | Bit 3                                                     | Bit 2 - Bit 0                                     |

|---------------|-------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------|

| Reserved      | Enable/<br>Disable<br>1: Enable<br>0: Disable<br>Default: 0 | Revertivity 1: Enable 0: Disable Default: 0 non-revertive | Priority<br>0: Highest<br>7: Lowest<br>Default: 0 |

Free Run may be treated like a reference. When it is enabled, Free Run will be entered when all references of higher priority are lost or masked. If or when a higher priority reference returns, it is switched to if Free Run is set as "revertive". When disabled, Free Run will be entered only if manually selected or all references fail without an available Hold Over history. For equal priority value, Free Run will be treated as lower priority.

History\_Policy, 0x25 (R/W)

| Bit 7 - Bit 1 | Bit 0                                                                    |

|---------------|--------------------------------------------------------------------------|

| Reserved      | Reference Switch Hold Over<br>Hisory Policy<br>0: Rebuild<br>1: Continue |

Bit 0 determines if Hold Over is retained or rebuilt when a reference switch occurs. See **Application Notes**, **Holdover History Accumulation and Management section**.

#### History\_Cmd, 0x26 (R/W)

| Bit 7 - Bit 2 | Bit 1-0                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved      | Hold Over Histroy Commands 01: Save active history to backup history 10: Restore active history from backup 11: Flush the active history and accumulation register 00: No command |

Bits 0-1 are written to save a holdover history to the backup history, restore the active holdover history from the backup, or flush the active history. The default value of the register is 00. The last command is latched and may be read by the application. A flush does not affect the backup history. See **Application Notes**, **Holdover History Accumulation and Management section**.

#### HoldOver\_Time, 0x27 (R)

| Bit 7 - Bit 0 |  |

|---------------|--|

Indicates the time since entering the Hold Over state. from 0-255, one bit per hour. Zero in non-Hold Over state and stops at 255.

#### Cfqdata, 0x30 (R/W)

| Bit 7 - Bit 0                      |

|------------------------------------|

| Configuration data write register. |

Configuration data is written to this register. Internal use only.

#### Cfgctr\_Lo, 0x31 (R)

| o.go==, o ()                               |               |  |

|--------------------------------------------|---------------|--|

|                                            | Bit 7 - Bit 0 |  |

| Configuration data write counter low byte. |               |  |

Low order byte of configuration data write counter. Internal use only.

Data Sheet #: TM054 Page 17 of 36 Rev: 02 Date: 11/07/08

Cfgctr\_Hi, 0x32 (R)

Bit 7 - Bit 0

Configuration data write counter high byte.

High order byte of configuration data write counter. Internal use only.

## Chksum, 0x33 (R/W)

| Bit 7 - Bit 1 | Bit 0                                                           |

|---------------|-----------------------------------------------------------------|

| Reserved      | Configuration Data Checksum pass/fail indicator 0: Fail 1: Pass |

Checksum verification register for configuration data. Internal use only.

## EE\_Mode, 0x36 (R/W)

| Bit 7 - Bit 1 | Bit 0                                    |

|---------------|------------------------------------------|

| Reserved      | EEPROM Write Enable 0: Disable 1: Enable |

EEPROM write enable register.

## EE\_Cmd, 0x37 (R/W)

| Bit 7                                                         | Bit 6 - Bit 2 | Bit 1 - Bit 0                                                                           |

|---------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------|

| EEPROM read/write<br>ready bit:<br>0 = Not Ready<br>1 = Ready | Reserved      | EEPROM read/write command bits:  00 = Reset FIFO  01 = Write Command  10 = Read Command |

EEPROM read/write command register.

## EE\_Page\_Num, 0x38 (R/W)

Bit 7 - Bit 0

EEPROM read/write page number, 0x00 to 0x9f (0 - 159)

EEPROM read/write page number register. EEPROM consist of 160 pages.

#### EE\_FIFO\_Port, 0x39 (R/W)

Bit 7 - Bit 0

EEPROM read/write FIFO data.

EEPROM read/write FIFO port register. EEPROM data is written to/read from this location.

Data Sheet #: TM054 Page 18 of 36 Rev: 02 Date: 11/07/08

## **Performance Specifications**

#### **Performance Definitions**

**Jitter and Wander** – Jitter and wander are defined respectively as "the short-term and long-term variations of the significant instants of a digital signal from their ideal positions in time". They are therefore the phase or position in time modulations of a digital signal relative to their ideal positions. These phase modulations can in turn be characterized in terms of their amplitude and frequency. Jitter is defined as those phase variations at rates above 10Hz, and wander as those variations at rates below 10Hz.

**Fractional frequency offset and drift** – The fractional frequency offset of a clock is the ratio of the frequency error (from the nominal or desired frequency) to the desired frequency. It is typically expressed as (n parts in 10<sup>x</sup>), or (n x 10-<sup>x</sup>). Drift is the measure of a clock's frequency offset over time. It is expressed the same way as offset.

**Time Interval Error (TIE)** – TIE is a measure of wander and is defined as the variation in the time delay of a given signal relative to an ideal signal over a particular time period. It is typically measured in ns. TIE is set to zero at the start of a measurement, and thus represents the phase change since the beginning of the measurement.

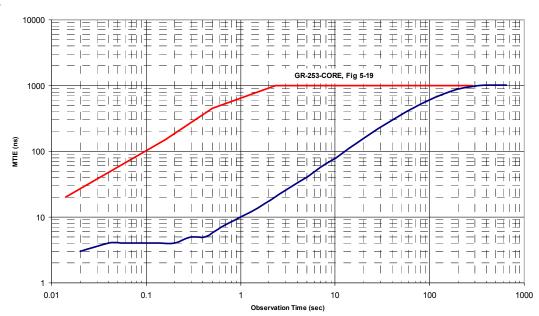

Maximum Time Interval Error (MTIE) — MTIE is a measurement of wander that finds the peak-to-peak variations in the time delay of a signal for a given window of time, called the observation interval (*t*). Therefore it is the largest peak-to-peak TIE in any observation interval of length *t* within the entire measurement window of TIE data. MTIE is therefore a useful measure of phase transients, maximum wander and frequency offsets. MTIE increases monotonically with increasing observation interval.

**Time Deviation (TDEV)** – TDEV is a measurement of wander that characterizes the spectral content of phase noise. TDEV(t is the RMS of filtered TIE, where the bandpass filter is centered on a frequency of 0.42/t.

#### **SM3E Performance**

**Input Jitter Tolerance** – Input jitter tolerance is the amount of jitter at its input a clock can tolerate before generating an indication of improper operation. GR-1244 and ITU-813 requirements specify jitter amplitude v.s. jitter frequency for jitter tolerance. The SM3E device provides jitter tolerance that meets the specified requirements.

**Input Wander Tolerance** – Input wander tolerance is the amount of wander at its input a clock can tolerate before generating an indication of improper operation. GR-1244 and ITU-813 requirements specify input wander TDEV v.s. integration time as shown below.

| Integration Time, (seconds) | TDEV (ns)             |  |

|-----------------------------|-----------------------|--|

| $0.05 \le \tau < 10$        | 100                   |  |

| 10 < τ < 1000               | 31.6 x $	au$ $^{0.5}$ |  |

| 1000 ≤ <i>τ</i>             | N/A                   |  |

The SM3E device provides wander tolerance that meets these requirements.

Phase Transient Tolerance – GR-1244 specifies maximum reference input phase transients that a clock system must tolerate without generating an indication of improper operation. The phase transient tolerance is specified in MTIE(nS) v.s. observation time from .001 to 100 seconds, as shown below.

| Observation time S (Seconds) | MTIE (ns)      |  |

|------------------------------|----------------|--|

| 0.001326 ≤S < 0.0164         | 61,000 x S     |  |

| 0.0164 < S < 1.97            | 925 + 4600 x S |  |

| 1.97 ≤S                      | 10,000         |  |

The SM3E will tolerate all reference input transients within the GR-1244 specification.

Free-run Frequency Accuracy – The ability of a clock to produce a frequency as close as possible to the nominal frequency in the absence of a reference.

Hold Over Frequency Stability – A measure of a clock's performance while in Hold Over mode over 24 hours, subjected to the specified temperature variations.

Data Sheet #: TM054 Page 19 of 36 Rev: 02 Date: 11/07/08

## **Performance Specifications continued**

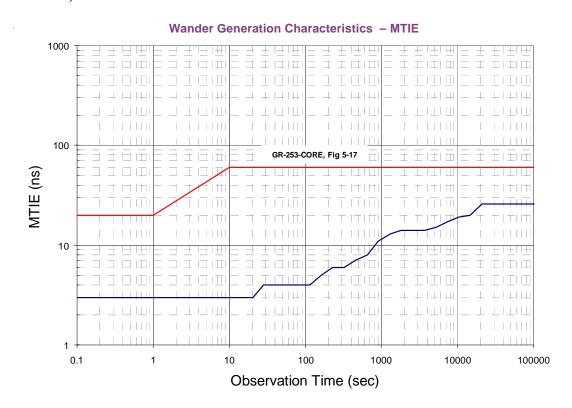

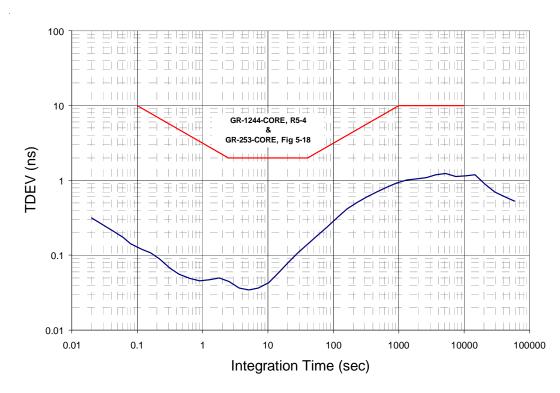

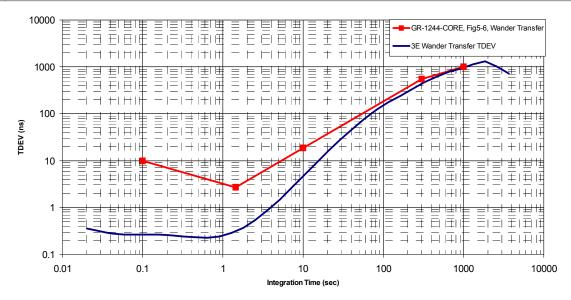

**Wander Generation** – Wander generation is the process whereby wander appears at the output of a clock in the absence of input wander. The SM3EG wander generation characteristics, MTIE and TDEV, are shown below, along with the requirements masks (bandwidth = 0.0016 Hz):

#### Wander Generation Characteristics - TDEV

Data Sheet #: TM054 Page 20 of 36 Rev: 02 Date: 11/07/08

## **Performance Specifications continued**

**Wander Transfer** – Wander transfer is the degree to which input wander is attenuated (or amplified) from input to output of a clock. The GR-1244 requirements for wander transfer limits are shown below.

| Integration time, τ (seconds) | Stratum 3ETDEV (nanoseconds) |  |

|-------------------------------|------------------------------|--|

| τ < 0.05                      | N/A                          |  |

| $0.05 \le \tau < 0.1$         | N/A                          |  |

| 0.1 ≤τ < 1.44                 | 3.16 x τ <sup>-0.5</sup>     |  |

| 1.44 ≤τ < 10                  | 1.86 x τ                     |  |

| 10 ≤τ < 300                   | 1.86 x τ                     |  |

| 300 ≤τ ≤1000                  | 32.2 x τ <sup>0.5</sup>      |  |

| 1000 < τ                      | N/A                          |  |

The SM3E, when configured for the appropriate Stratum 3E bandwidth frequency, meets the Stratum 3E requirements,

Jitter Generation – Jitter generation is the process whereby jitter appears at the output of a clock in the absence of input jitter.

The device jitter generation performance is as shown below:

| Jitter                       | 19.44 MHz                        | 77.76 MHz                         |  |

|------------------------------|----------------------------------|-----------------------------------|--|

| Broadband<br>(10 Hz - 2 MHz) | 8 ps Typical                     | 8 ps Typical                      |  |

| SONET Band                   | (12 kHz -2MHz)<br>1.5 ps Typical | (12 kHz -20MHz)<br>0.8 ps Typical |  |

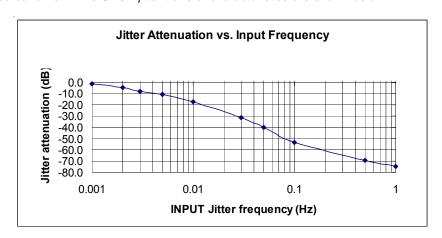

**Jitter Transfer** – Jitter transfer is the degree to which input jitter is attenuated (or amplified) from input to output of a clock. It is a function of the selected bandwidth. The SM3E jitter transfer characteristics are shown below:

Data Sheet #: TM054 Page 21 of 36 Rev: 02 Date: 11/07/08

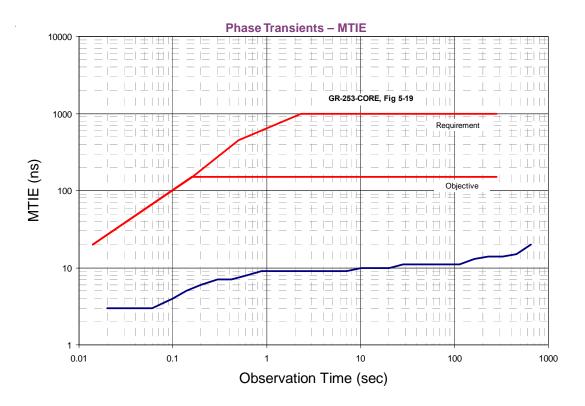

**Phase Transients** – A phase transient is an unusual step or change in the phase-time of a signal over a relatively short time period. This may be due to switching between equipment, reference switching, diagnostics, entry or exit to/from Hold Over, or input reference transients. The SM3EG performance for reference switches is shown below:

Data Sheet #: TM054 Page 22 of 36 Rev: 02 Date: 11/07/08

## **Performance Specifications continued**

Capture range and Lock range – Capture range and lock range are the maximum frequency errors on the reference input within which the phase locked loop is able to achieve lock and hold lock, respectively. The SM3E Stratum 3E performance is shown below:

| Characteristic | SM3E     | Requirement |

|----------------|----------|-------------|

| Capture range  | ± 15 ppm | ± 4.6 ppm   |

| Lock in range  | ± 15 ppm | N/A         |

This is the minimum capability, and guarantees the ability to capture and lock with a reference that is offset the maximum allowed in one direction in the presence of an OCXO that is offset the maximum in the opposite direction (4.6 ppm + 4.6 ppm = 9.2 ppm).

Master/Slave Skew, Reference switch settling time, and Phase Build-Out resolution – Master/Slave Skew, Reference switch settling time, and Phase Build-Out resolution performance are shown below:

| Characteristic                 | SM3E                                                 | Requirement                                               |

|--------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| Master/Slave phase skew        | < 2 nS                                               | N/A                                                       |

| Reference switch settling time | Stratum 3E: < 700 sec. up to 20 ppm frequency offset | Stratum 3E: < 700 sec. up to +/- 4.6 ppm frequency offset |

| Phase Build-Out resolution     | 1 nS                                                 | < 50 nS                                                   |

Data Sheet #: TM054 Page 23 of 36 Rev: 02 Date: 11/07/08

#### **SM3E** Initialization:

#### Power-up:

- 1. If possible, always start up in master mode. After the module is powered up, hold the reset pin low for 10ms. Wait 1200ms and read the contents of register 0x33. If it reads1 then the module came up properly. If it reads 0 then reset the module and reread register 0x33 after 1200ms. The contents of 0x33 must read 1 before continuing.

- 2. Remain in the default free-run mode for 10 seconds then read the value of bit 1 of register 0x11 or pin 2, the LOL alarm output. If the LOL alarm is set, the reset pin must be pulled low as in 1 above. In the free-run mode the LOL alarm should never be set. This indicates the module is in an invalid state. If there is no LOL alarm in free-run the module is ready.

#### Operation:

On power up or after a reset all the registers are loaded with their default values. The default values of some important registers are given below assuming the SM34 module operates as a Master

| Address(Hex) | Register Name         | Value(Binary MSB first) | Notes                                                     |

|--------------|-----------------------|-------------------------|-----------------------------------------------------------|

| 0x03         | Bandwidth_PBO         | 00000111                | Bandwidth = 0.098Hz                                       |

| 0x04         | Ctl_Mode              | 0000r010                | r - Read Only                                             |

| 0x05         | Op_Mode               | 00010000                | Indicates Free run mode                                   |

| 0x06         | Max_Pullin_Range      | 01100100                |                                                           |

| 0x0b         | Ref_Mask              | 0000000                 |                                                           |

| 0x0d         | Ref_Rev_Delay         | 00000101                |                                                           |

| 0x0e         | Phase_Offset          | 00000000                |                                                           |

| 0x0f         | Calibration           | 00000000                |                                                           |

| 0x11         | DPLL_Status           | 0000000                 | Indicates No Active Reference                             |

| 0x13         | Intr_Enable           | 00000000                | Indicates Interrupts are disabled                         |

| 0x1c-0x23    | Ref(1-8)_Frq_Priority | xxxx0000                | Frequencies are auto detected                             |

| 0x33         | Chksum                | xxxxxxx1                | Bit0 should be high to indicate that data has been loaded |

|              |                       |                         | correctly from the EEPROM.                                |

- I. The unit starts up in Free Run and operates in Manual mode. Here are the steps that need to be taken to lock the unit to a reference in Manual mode.

- 1. Apply signal to the reference inputs.

- 2. Set the appropriate pull in range by writing to address 0x06.

- 3. A value of 0001xxxx, depending on which (Ref 1-8) reference to lock to, should be written to address 0x05.

- 4. Enable Reference mask for appropriate references by writing a 1 to the reference bit in address 0x0b.

- 5. Enable all Interrupts by writing 11111111 to address 0x13.

- II. To lock the unit to a reference in autonomous (automatic) mode after power up or reset, the following steps should be taken. You can also switch from Manual to Autonomous mode directly. When doing so, please ensure that the appropriate references are available by checking REF\_AVAILABLE register (address: 0x0c).

- 1. Clear bit1 of CTL\_MODE register (address: 0x04). This puts the module in autonomous mode.

- 2. Apply signal to the reference inputs

- 3. Set the appropriate pull in range by writing to address 0x06

- 4. The default bandwidth of 0.098 Hz is appropriate for Stratum 3 operation.

- 5. Enable Reference mask for appropriate references by writing a 1 to the reference bit in address 0x0b.

- 6. Set priority and revertivity for the input references by writing to the appropriate Ref\_Frq\_Priority registers (bits 3-0).

- 7. Enable all Interrupts by writing 11111111 to address 0x13.

- 8. Set the unit to operate in autonomous mode by clearing bit1 of address 0x04

#### III. Slave Mode Operation:

- 1. As a Slave, the module operates in Autonomous mode.

- 2. The Bandwidth is set, by default, to 1.6Hz (Bandwidth\_PBO register (Address 0x03): 00001011).

- 3. Note that bit 4 of the OP\_MODE register (Address 0x05) is cleared.

- 4. The values in Bits 3-0 of this register have no effect on the operation of the Slave module.