# TACHYON Fibre Channel Interface Controller

# Technical Data

## **Features**

- Supports 1063, 531, and 266 Mbaud Link Speeds

- Supports Fibre Channel Class 1, 2, and 3 Services

- Supports Fibre Channel Arbitrated Loop (FC-AL), Point-to-Point, and Fabric (Crosspoint-Switched) Topologies

- Compliant with the Fibre Channel Physical and Signaling Interface (FC-PH)

- Complies to Fibre Channel System Initiative (FCSI) Profiles

- Provides Complete Support of Both Networking and Mass Storage Connections

- Supports up to 2-Kbyte Frame Payload Size for All Classes of Service

- Manages Sequence Segmentation and Reassembly in the Hardware

- Supports up to 16,384 Concurrent SCSI I/O Transactions

- Provides FCP Assists for SCSI Initiators and Targets

- Processes Inbound and Outbound Data Simultaneously Due to Full Duplex Internal Architecture

- Interfaces Directly to Industry and ANSI Standard 10-bit and 20-bit FC-0 Physical Link Modules

- Supports Open Broadcast Replicate Transmission and Reception of FC-AL

- Supports Reception of Fabric-Addressed Frames for a Fibre Channel Services Server on FC-AL

- 3.3 V Power Supply

# **Applications**

- Mass Storage System I/O Channel

- Computer System I/O Channel

- High Speed Peripheral Interface

- Fibre Channel I/O for Network Switches and Hubs

## **HPFC-5000**

# **Description**

Tachyon provides a very highly integrated Fibre Channel (FC) interface controller in a single chip solution. It supports both networking and mass storage over a single host connection. In addition, Tachyon provides a high performance controller at an inexpensive cost due to its significant number of design features.

Tachyon is packaged in a 208 pin Metal Quad (MQuad®) flat pack.

# **Table of Contents**

| 1. | Fibre  | Channel General Information              | 5        |

|----|--------|------------------------------------------|----------|

|    | 1.1    | Fibre Channel Data Hierarchy             | 5        |

|    | 1.2    | Networking Encapsulation                 | 6        |

|    | 1.3    | Mass Storage Encapsulation               | 7        |

|    | 1.4    | Fibre Channel Protocol for SCSI          | 7        |

|    | 1.5    | Profile Support                          | 7        |

|    | 1.6    | Host Bus Adapter Board                   | 8        |

| 2. | Archit | ectural Overview                         | S        |

|    | 2.1    | Transmit Process Overview                | ç        |

|    | 2.2    |                                          | 11       |

|    |        |                                          | 11       |

|    |        |                                          | 11       |

|    |        |                                          | 12       |

|    |        |                                          | 12       |

|    | 2.3    | <u> </u>                                 | 13       |

|    | ۵.5    |                                          | 13       |

|    |        | v                                        | 15       |

|    |        | v                                        | 15<br>15 |

|    |        | · ·                                      | 15       |

|    |        | 2.9.4 FOI WIRE for facily on as a farget | Le       |

| 3. | Archit | ectural Details                          | 16       |

|    | 3.1    | Tachyon Internal Block Diagram           | 16       |

| 4. | Tachy  | on Signal Descriptions                   | 17       |

|    | 4.1    | Tachyon Logic Symbol                     | 17       |

|    | 4.2    |                                          | 18       |

|    | 4.3    | ·                                        | 19       |

|    | 4.4    |                                          | 21       |

|    | 4.5    |                                          | 22       |

|    | 1.0    |                                          | 22       |

|    | 4.6    |                                          | 23       |

|    | 1.0    |                                          | 23       |

| 5  | Regist | ers 5                                    | 25       |

| 9. |        |                                          |          |

|    | 5.1    | · ·                                      | 25       |

|    | 5.2    |                                          | 27       |

|    | 5.3    | · ·                                      | 28       |

|    |        |                                          | 28       |

|    |        |                                          | 28       |

|    |        | •                                        | 26       |

|    |        |                                          | 29       |

|    |        |                                          | 30       |

|    | 5.4    | · ·                                      | 30       |

|    |        | 5.4.1 HPCQ Base Register                 | 30       |

|      |      | 5.4.2          | HPCQ Length Register                                 |

|------|------|----------------|------------------------------------------------------|

|      |      | 5.4.3          | HPCQ Producer Index Register                         |

|      |      | 5.4.4          | HPCQ Consumer Index Address Register                 |

|      |      | 5.4.5          | Host's Copy of the HPCQ Consumer Index Register      |

| 5    | 5.5  |                | gisters                                              |

|      |      | 5.5.1          | IMQ Base Register                                    |

|      |      | 5.5.2          | IMQ Length Register                                  |

|      |      | 5.5.2 $5.5.3$  |                                                      |

|      |      |                | IMQ Consumer Index Register                          |

|      |      | 5.5.4          | IMQ Producer Index Address Register                  |

| _    |      | 5.5.5          | Host's Copy of the IMQ Producer Index                |

| b    | 5.6  |                | Registers                                            |

|      |      | 5.6.1          | MFSBQ Base Register                                  |

|      |      | 5.6.2          | MFSBQ Length Register                                |

|      |      | 5.6.3          | MFSBQ Producer Index Register                        |

|      |      | 5.6.4          | MFSBQ Consumer Index Register                        |

|      |      | 5.6.5          | MFS Buffer Length Register                           |

| 5    | 5.7  | SFSBQ          | Registers                                            |

|      |      | 5.7.1          | SFSBQ Base Register                                  |

|      |      | 5.7.2          | SFSBQ Length Register                                |

|      |      | 5.7.3          | SFSBQ Producer Index Register                        |

|      |      | 5.7.4          | SFSBQ Consumer Index Register                        |

|      |      | 5.7.5          | SFS Buffer Length Register                           |

| 5    | 5.8  |                | egisters                                             |

|      | •••  | 5.8.1          | SEST Base Register                                   |

|      |      | 5.8.2          | SEST Length Register                                 |

|      |      | 5.8.3          | SCSI Buffer Length Register                          |

| 5    | 5.9  |                | n Registers                                          |

| J    | 0.9  |                |                                                      |

|      |      | 5.9.1          | Tachyon Configuration Register                       |

|      |      | 5.9.2          | Tachyon Control Register                             |

|      |      | 5.9.3          | Tachyon Status Register                              |

|      |      | 5.9.4          | Tachyon Flush SEST Cache Entry Register              |

|      |      | 5.9.5          | Tachyon EE_Credit Zero Timer Register                |

|      |      | 5.9.6          | Tachyon BB_Credit Zero Timer Register                |

|      |      | 5.9.7          | Tachyon Receive Frame Error Counter Register         |

| 5    | 6.10 | Frame I        | Manager Registers                                    |

|      |      | 5.10.1         | Frame Manager Configuration Register                 |

|      |      | 5.10.2         | Frame Manager Control Register                       |

|      |      | 5.10.3         | Frame Manager Status Register                        |

|      |      | 5.10.4         | Frame Manager RT_TOV/AL_TIME & ED_TOV Register       |

|      |      | 5.10.5         | Frame Manager Link Error Status Counters #1 Register |

|      |      | 5.10.6         | Frame Manager Link Error Status Counters #2 Register |

|      |      |                | Frame Manager World Wide Name Hi Register            |

|      |      |                | Frame Manager World Wide Name Lo Register            |

|      |      |                | Frame Manager Received AL PA Register                |

|      |      |                | Frame Manager Primitive Register                     |

|      |      | 0.10.10        | Tranc manager trininge negions                       |

| . тя | SI   |                |                                                      |

|      |      | 6.1.1          | TSI Transaction Types                                |

|      |      | 6.1.2          | Data Structure Transaction Size                      |

|      |      | 0.1.2          |                                                      |

|      |      |                |                                                      |

|      |      | 6.1.3<br>6.1.4 | TSI Transaction Protocol                             |

|     |         | 6.1.6     | Address Cycle                                | 62  |

|-----|---------|-----------|----------------------------------------------|-----|

|     |         | 6.1.7     | Driving Bi-Directional Signals               | 62  |

|     |         | 6.1.8     | Write Transactions                           | 62  |

|     |         | 6.1.9     | Read Transactions                            | 62  |

|     |         | 6.1.10    | TSI Transaction Window                       | 63  |

|     |         | 6.1.11    | TSI Transaction Ordering                     | 63  |

|     |         | 6.1.12    | Endian-ness                                  | 63  |

|     |         | 6.1.13    | Parity                                       | 63  |

|     |         | 6.1.14    | Error Handling                               | 64  |

|     |         | 6.1.15    | Reset                                        | 65  |

|     |         | 6.1.16    | Arbitration                                  | 66  |

|     |         | 6.1.17    | Interrupts                                   | 66  |

|     |         | 6.1.18    | Host Interface Design Notes                  | 67  |

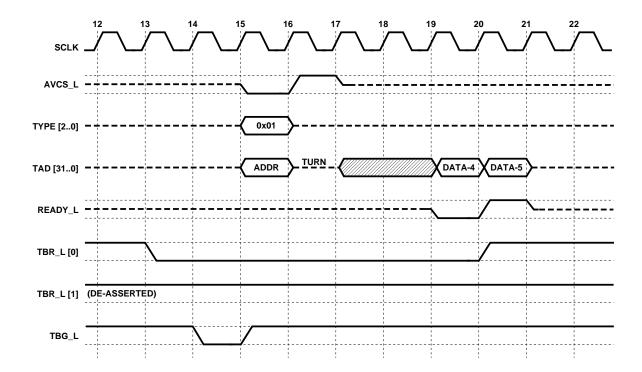

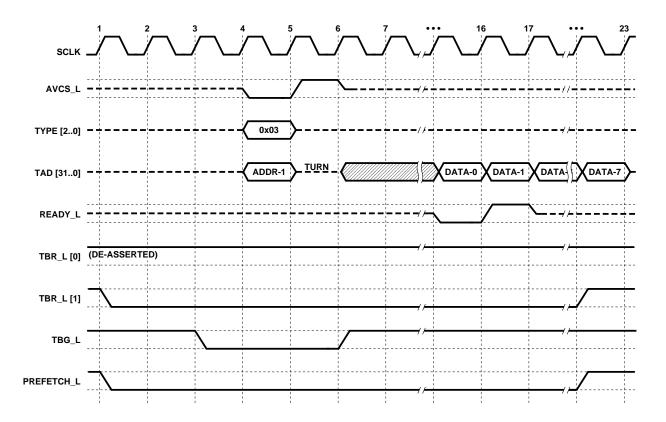

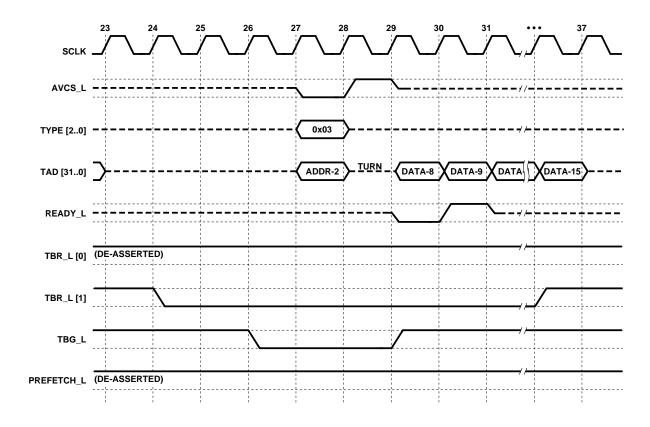

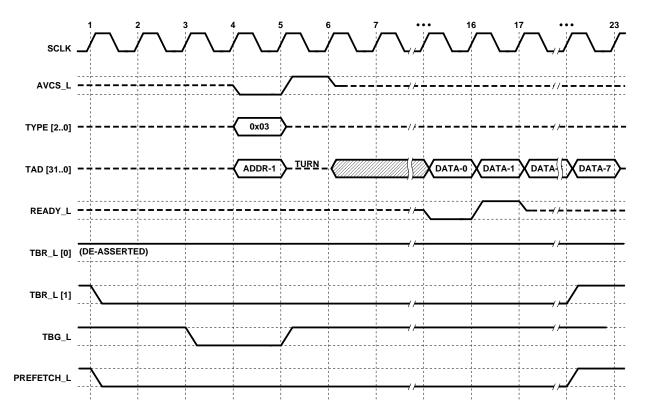

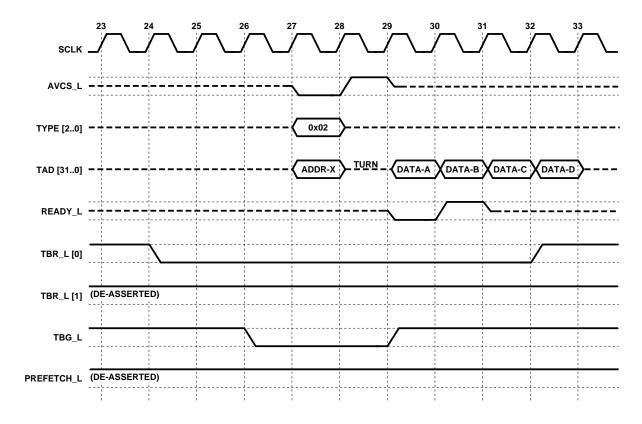

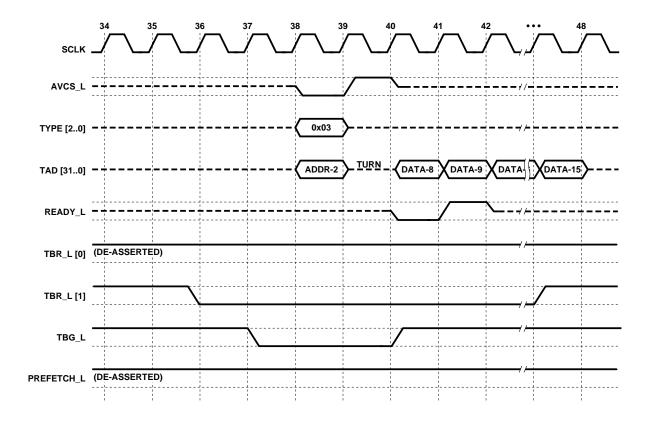

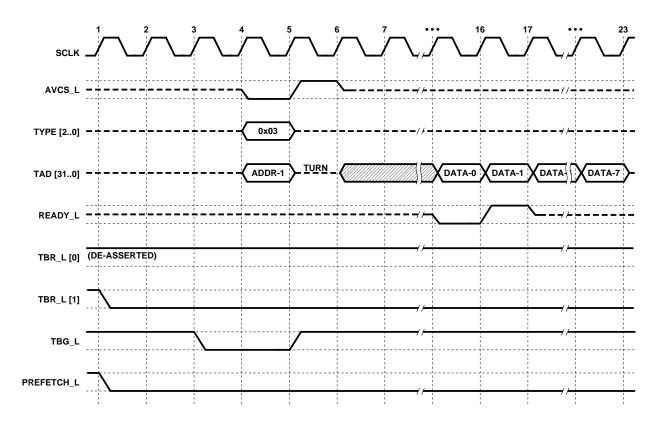

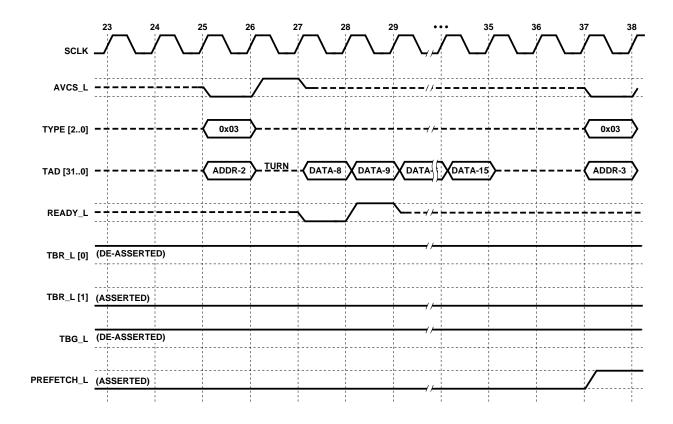

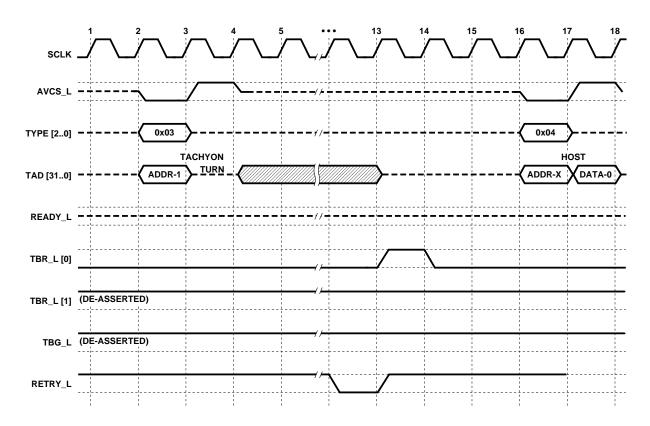

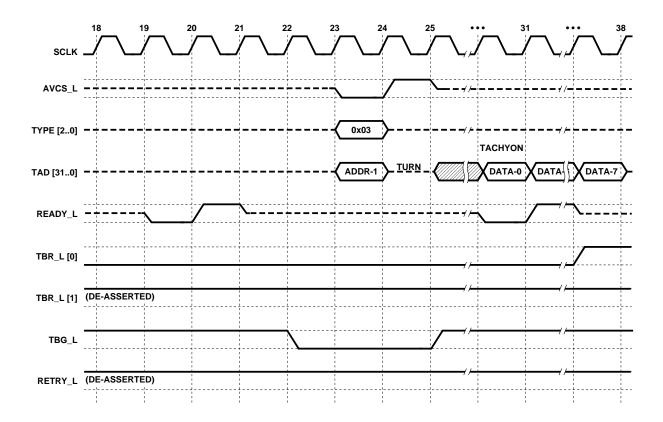

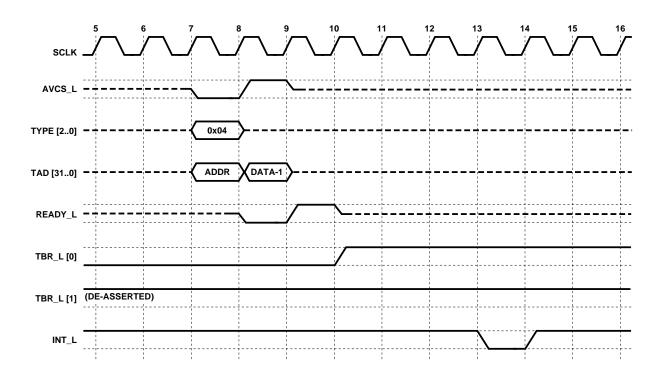

|     | 6.2     |           | actional Waveforms                           | 67  |

|     |         | 6.2.1     | Slave Reads and Writes                       | 68  |

|     |         | 6.2.2     | DMA Writes                                   | 71  |

|     |         | 6.2.3     | DMA Write Streaming                          | 74  |

|     |         | 6.2.4     | DMA Reads                                    | 76  |

|     |         | 6.2.5     | DMA Read Prefetching                         | 78  |

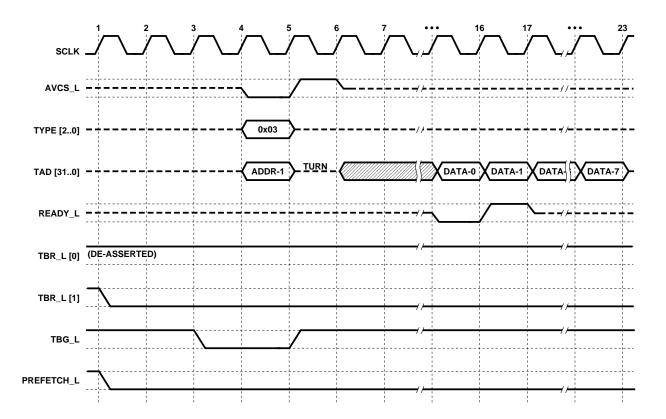

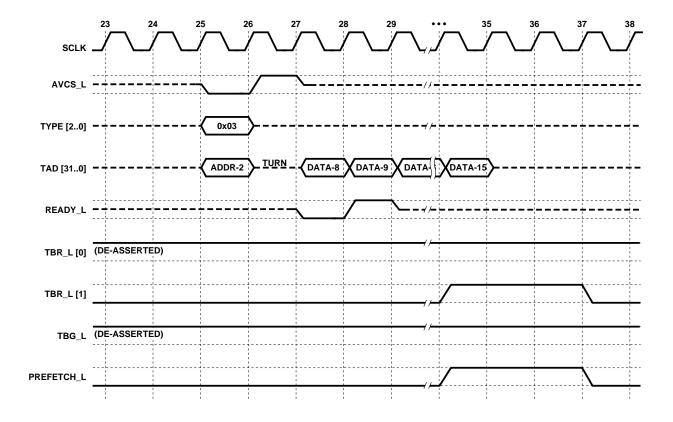

|     |         | 6.2.6     | DMA Read Channels                            | 80  |

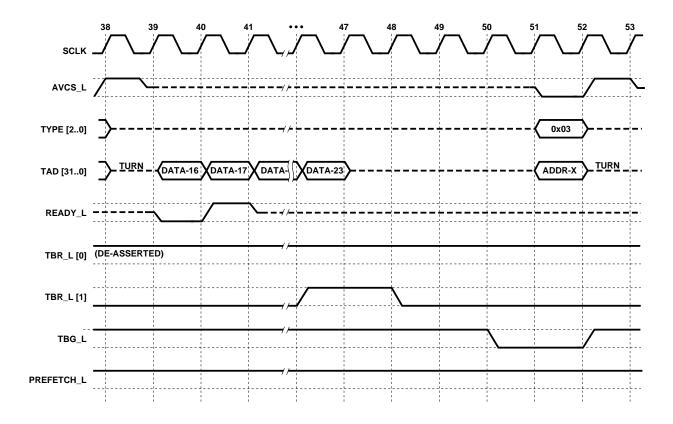

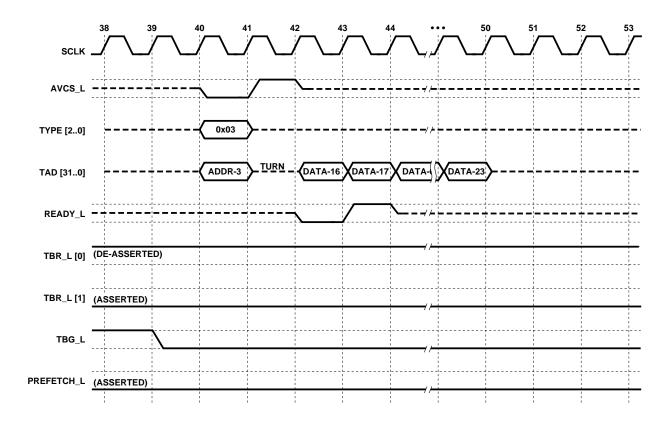

|     |         | 6.2.7     | Streamed Block Reads                         | 83  |

|     |         | 6.2.8     | Prefetching Across Back-To-Back Read Streams | 86  |

|     |         | 6.2.9     | Retried Read Transaction                     | 89  |

|     |         | 6.2.10    | Interrupt Signal                             | 91  |

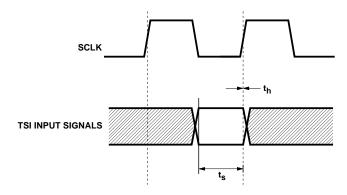

|     | 6.3     |           | ning Requirements                            | 92  |

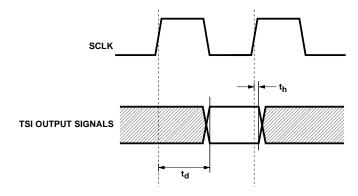

|     |         | 6.3.1     | TSI Input Signal Timing Requirements         | 92  |

|     |         | 6.3.2     | TSI Output Signal Timing Requirements        | 93  |

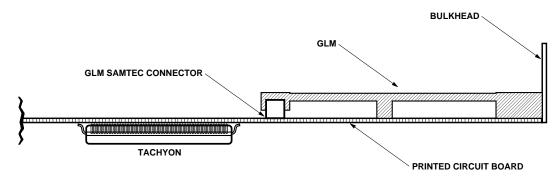

|     | 6.4     |           | gnal Information                             | 94  |

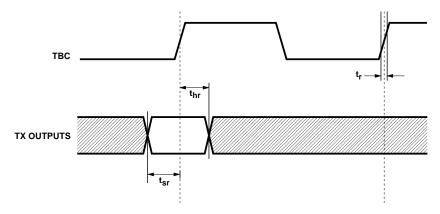

|     |         | 6.4.1     | GLM Transmit Signals                         | 94  |

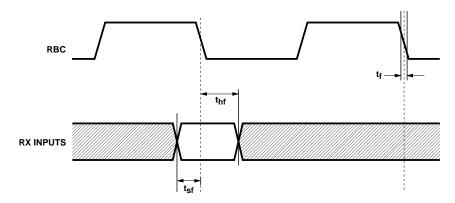

|     |         | 6.4.2     | GLM Receive Signals                          | 95  |

| _   | Elector | ical Dec  | autuati aura                                 | 06  |

| 7.  | Liectr  |           | criptions                                    | 96  |

|     | 7.1     |           | e Maximum Ratings                            | 96  |

|     | 7.2     | Recom     | mended Operating Conditions                  | 96  |

|     | 7.3     | Electric  | al Parameters                                | 97  |

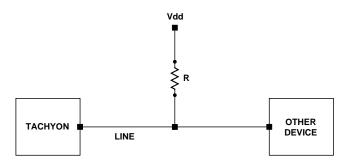

|     | 7.4     | Pull-Up   | Values                                       | 98  |

|     | 7.5     | Pull-Do   | wn Value                                     | 98  |

|     | 7.6     | Externa   | d PLL Components                             | 99  |

|     |         |           |                                              |     |

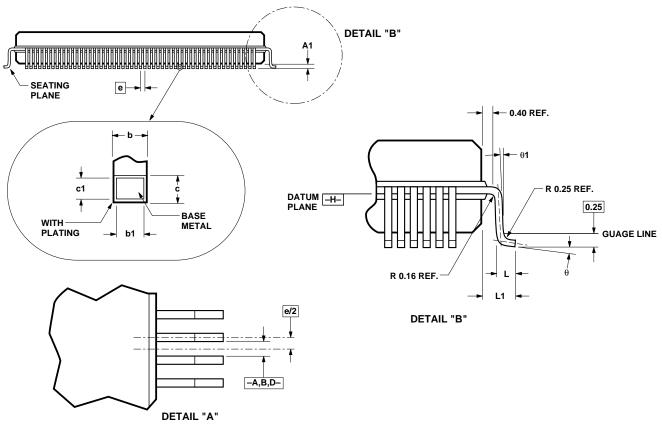

| 8.  | Mecha   | nical De  | escriptions                                  | 99  |

|     | 8.1     | General   | Information                                  | 99  |

|     | 8.2     |           | l Specifications                             | 99  |

|     | 8.3     |           | ions                                         | 100 |

|     | 8.4     |           | nended Handling Precautions                  | 101 |

|     |         |           |                                              |     |

| 1   | Limite  | ed Airflo | w Applications                               | 102 |

| 1.2 | Imple   | menting   | Tachyon with Little Endian System            | 103 |

| _   |         |           |                                              |     |

| 1.3 | PCB L   | ayout S   | uggestions                                   | 105 |

# 1. Fibre Channel General Information

Fibre Channel supports both networking and mass storage interconnections. The Fibre Channel standard defines a number of encapsulation methods. These methods enable both networking and mass storage protocols to be transported over a single Fibre Channel physical interface. This Fibre Channel General Information section gives an overview of the Fibre Channel data hierarhy and describes how Tachyon manages networking and mass storage (particularly SCSI) devices.

# 1.1 Fibre Channel Data Hierarchy

Fibre Channel technology defines a hierarchical structure for data transactions. The data terminology of this hierarchy is defined below:

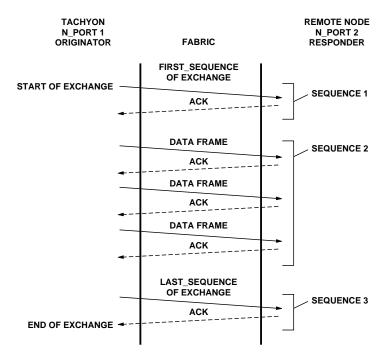

## **Exchange**

The exchange is the highest level of the data transaction hierarchy. The exchange defines a conversation occurring between two nodes. This conversation can be a long or short term interchange of information. An exchange consists of one or more sequences. An exchange is also known as an I/O transaction.

### Sequence

The sequence in Fibre Channel protocol correlates to a data packet or datagram in networking protocols. A sequence consists of a set of one or more frames. Each frame of a particular sequence contains a common Sequence\_ID. A node sends frames of a sequence unidirectionally to the remote node. The sequence includes the corresponding Link Control frames (e.g., ACKs, BSYs,

RJTs, etc.) that may be sent from the remote node.

A sequence can be any length, but to satisfy various timing and complexity constraints, a node may not be able to send the entire sequence all at once. The sequence can be divided into chunks, or frames, of data.

### **Frame**

The frame is the smallest unit of information interchange between two nodes. A frame must meet many stringent constraints. Various fabrics and nodes may impose their own constraints, so some nodes may have to send frames of varying sizes in order to satisfy these constraints. Frames have the following FC frame format:

| FIELD NAME | SOF | FRAME HEADER | DATA PAYLOAD | CRC | EOF |   |

|------------|-----|--------------|--------------|-----|-----|---|

| # OF BYTES | 4   | 24           | 0 – 2112     | 4   | 4   | 1 |

Figure 1.1 Fibre Channel Frame Format.

The Fibre Channel standard supports a frame payload up to 2112 bytes; however, Tachyon only supports an outbound frame payload up to **2048** bytes. This outbound frame payload includes optional headers.

The following figure shows an exchange example.

Figure 1.2 Exchange Example.

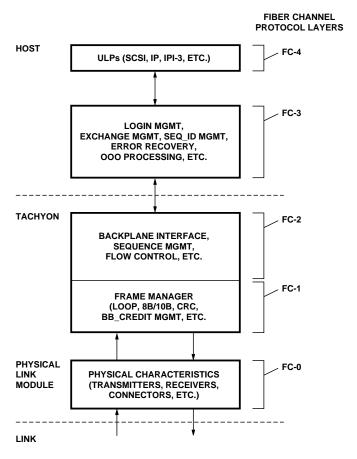

Figure 1.3 Fibre Channel Protocol Block Diagram.

# 1.2 Networking Encapsulation

Fibre Channel supports any known networking protocol. This is possible because Fibre Channel has defined FC-4, which specifies the mapping of Upper Level Protocols (ULPs) to the lower Fibre Channel levels, FC-3, FC-2, FC-1, and FC-0. Examples of ULPs include SCSI, IP, IPI, etc. The Fibre Channel Physical Interface comprises Fibre Channel protocol levels FC-2, FC-1, and FC-0.

The following figure shows a block diagram of Tachyon with the associated Fibre Channel protocol layers.

Using the Fibre Channel Physical Interface, FC-4 mapping protocols can transfer ULP data. For example, in most networking protocol stacks, the concept of a data packet or datagram exists. The networking data packet or datagram is analogous to the Fibre Channel sequence. To send a sequence, the Originator node segments the sequence into frames. The ULP data packet is written to the data payload field of the Fibre Channel frame(s). Then the SOF, header, CRC, and EOF information is added. The Originator node transmits these encapsulated frames across the Fibre Channel interconnection fabric. The Responder node receives and reassembles the sequence. When the data transmission is complete, the ULP manages the remainder of the data processing.

Mass storage Fibre Channel exchanges map directly to device I/O transactions. However, networking exchanges are not as easily defined and networking exchanges can occur in many

different ways. One way is a "long term" exchange. This is where a node sends data to another node, establishes an exchange between the nodes as a virtual link, and keeps the exchange active. Another way is a "short term" exchange, where a TCP connection is mapped onto an exchange. An exchange is created when an application connects. An exchange is terminated when an application disconnects.

# 1.3 Mass Storage Encapsulation

Fibre Channel was originally intended as a follow-on technology to lower performance mass storage interconnects. In particular, Fibre Channel focused on improving SCSI and IPI technologies. The Fibre Channel standards groups defined encapsulation methods for both of these protocols. Tachyon supports both SCSI and IPI protocols, and provides special hardware assists for the SCSI protocol. These SCSI hardware assists execute the encapsulation protocol in hardware to provide high performance and low latency I/O transactions. The exchange originator transmits these encapsulated SCSI frames across the Fibre Channel interconnection fabric. The responder receives and reassembles the fibre channel sequence. When the sequence is reassembled, the remainder of the data processing is managed using upper layer SCSI protocol.

# 1.4 Fibre Channel Protocol for SCSI

This section includes Fibre Channel Protocol for SCSI (FCP) information and how a SCSI I/O transaction maps onto the Fibre Channel transaction hierarchy. Each SCSI I/O transaction maps on a separate independent Fibre Channel exchange. For FCP, an exchange splits into three distinct phases: the Command Phase, the Data Phase, and the Status Phase. Each phase involves the transmission and/or reception of one or more Fibre Channel sequences. These sequences provide a mechanism of flow control and notification of impending transfers between the initiator and the target device. The Command Phase, Data Phase, and Status Phase are defined below:

### **Command Phase**

The FCP Initiator uses the Command Phase to inform the target device of its intention to perform an I/O transaction. The Command Phase consists of a single frame SCSI Command Sequence (FCP\_CMND) that carries information to the target device(s). This information includes the direction of transfer, the length of transfer, and the SCSI address. After the target device processes this SCSI Command Sequence, the transaction enters the Data Phase. If a Data Phase does not exist, the transaction will enter the Status Phase.

### **Data Phase**

The Data Phase consists of a two step process:

The target transmits or receives data via the Data Sequence (FCP\_DATA). The direction of transfer is identified in the original Command Sequence. This data sequence may consist of one or more frames. 2. The target device sends a Transfer Ready (FCP\_XFER\_RDY) sequence to inform the initiator that it has the resources ready for a data transfer. The FCP\_XFER\_RDY sequence is an optional step for an FCP Initiator Read Exchange. When the initiator receives the FCP\_XFER\_RDY, the process moves on to the second step.

### **Status Phase**

The Status Phase begins when the last FCP\_DATA completes. In the Status Phase, the target device sends a single frame SCSI Status Sequence (FCP\_RSP) describing how well the transaction proceeded. Once the initiator processes this sequence, the SCSI I/O transaction is complete.

# 1.5 Profile Support

Tachyon supports the FCSI profiles for FC-IP and FCP. Tachyon does not provide hardware assists for any other profiles, such as IPI-3. By using the generic sequence transmit and receive capabilities of Tachyon, the host can support any known profiles. Agilent Technologies will only test FCSI profiles for FC-IP and FCP.

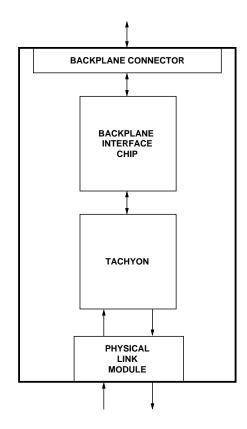

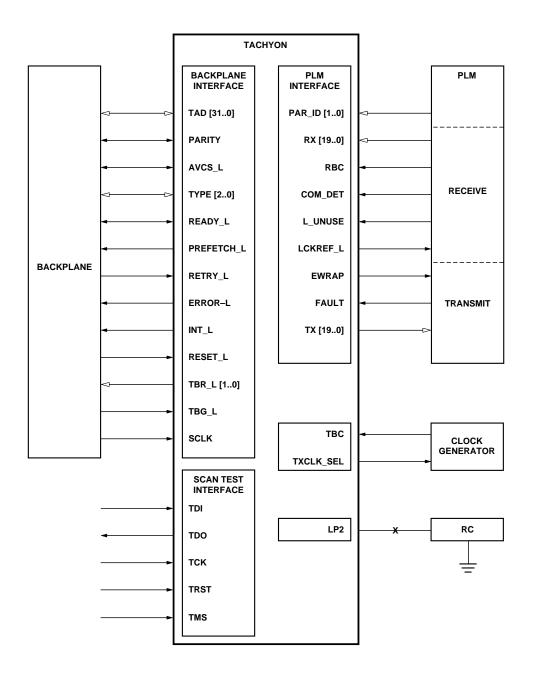

# 1.6 Host Bus Adapter Board

A generic Fibre Channel host bus adapter board contains the following components:

- 1. A Backplane Connector, which connects the backplane interface chip to the host bus

- 2. A Backplane Interface Chip, which enables connection to PCI, EISA, a propriety bus, etc.

- 3. Tachyon, the Fibre Channel interface controller chip

- 4. A Physical Link Module (PLM), for example, a 20-bit Gigabit Link Module (GLM)

Figure 1.4 Typical Host Bus Adapter Board Block Diagram.

# 2. Architectural Overview

This section provides an architectural overview of the transmit, receive, and SCSI hardware assists processes of Tachyon.

# 2.1 Transmit Process Overview

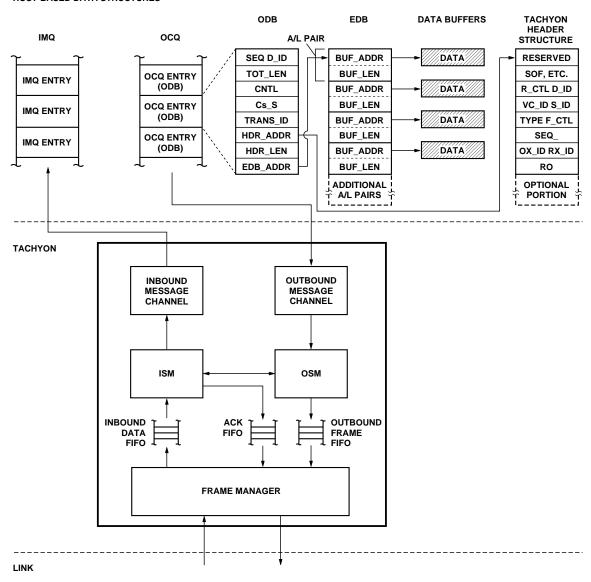

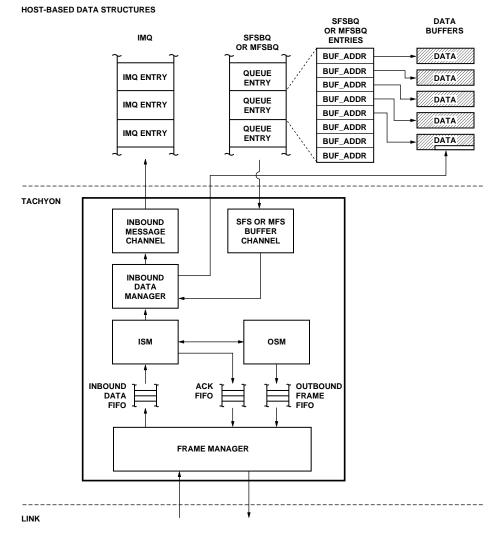

The following figure illustrates the transmit process overview.

### **HOST-BASED DATA STRUCTURES**

Figure 2.1 Transmit Process Overview.

A normal transmit transaction begins when the host creates buffers of data to be sent. These data buffers are stored in host memory. The host creates a Tachyon Header Structure which contains Fibre Channel header information and resides in host memory. The host creates an Outbound Descriptor Block (ODB) host data structure that defines the sequence of data to be transmitted. The ODB contains Fibre Channel information (e.g., maximum frame size, class of service, exchange identifier, sequence identifier, etc.) that is obtained from the host managed login parameters. The ODB contains a pointer (Hdr\_Addr) to the Tachyon Header Structure. Tachyon uses the Fibre Channel information in the ODB and the Tachyon Header Structure to construct the Fibre Channel frame headers. The ODB also contains a pointer (EDB Addr) to the Extended Descriptor Block (EDB). The EDB contains Address/Length pairs (A/L pairs) that define where the data buffers are located in host memory.

The Outbound Command Queue (OCQ) is an area in host memory consisting of an array of OCQ entries. The producer index of the OCQ, known as the OCQ Producer Index, points to the next available OCQ entry in which an ODB can be created. Once the host creates the ODB, it writes the index of that OCQ entry (ODB) to the OCQ Producer Index register. This notifies Tachyon that a new valid ODB exists. The OCQ Producer Index is incremented to the next available OCQ entry for the following valid ODB.

If Tachyon's Outbound Sequence Manager (OSM) is not currently transmitting a sequence, the OSM performs a DMA operation to move the ODB via the Outbound Message Channel from host memory into an internal Tachyon resource. When the OSM receives the ODB, the OSM has all the information needed to transmit the sequence. It has all of the Fibre Channel information to construct the Fibre Channel frame headers and all of the A/L pairs that point to the data in host memory.

The OSM retrieves data from the Outbound Message Channel in frame size packets for transmission. The OSM DMAs the first frame from the data buffer in host memory to the Outbound Frame FIFO. Once the entire frame is in the Outbound Frame FIFO, the OSM notifies the Frame Manager to begin transmitting the frame onto the link. When the first word of the frame is transmitted onto the link, the OSM is notified. The OSM then begins to move the second frame from host memory to the Outbound Frame FIFO. The first frame is being moved from the Outbound Frame FIFO onto the link during the same time that the second frame is being moved from host memory into the Outbound Frame FIFO. This operation continues until the entire sequence has been transmitted.

For a normal Class 1 (dedicated connection with ACKs) and for a Class 2 (connectionless transaction with ACKs) transmit transaction, the remote node returns ACKs to Tachyon when

the remote node receives frames. When Tachyon's Inbound Sequence Manager (ISM) receives a frame, the ISM first determines if it is an ACK frame. If the frame is an ACK frame, the ISM passes the ACK to the OSM. The OSM verifies that the ACK is associated with the current outbound sequence and increments an ACK counter. The OSM maintains a count of the number of frames transmitted for the sequence and the number of ACK frames received. When all frames of the sequence have been transmitted and the number of ACK frames equals the number of transmitted frames, then the sequence has been transmitted successfully to the remote node. For Class 3, when the remote node receives the frames, it does not return ACKs to Tachyon.

When the OSM transmits the sequence successfully, it notifies the ISM to generate an outbound completion message. The ISM sends this completion message to the host as an entry in the Inbound Message Queue (IMQ). Completion messages contain information on the status of the transfer and any information needed by the host for queue maintenance. In this case, the outbound completion message notifies the host that the sequence has been transmitted successfully.

# 2.2 Receive Process Overview

The ISM manages receive processes for four types of sequences: 1) Single Frame Sequences, 2) Multiframe Sequences, In Order, 3) Multiframe Sequences, Out of Order, and 4) Multiframe Sequences, Deferred P\_BSY Mode.

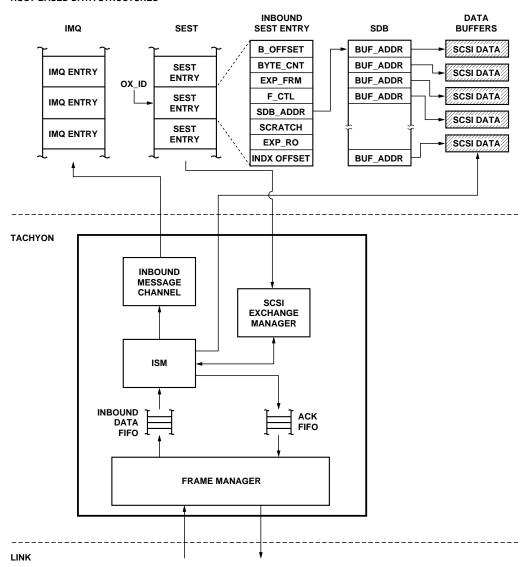

The following figure illustrates the SFS and MFS receive Processes:

# 2.2.1 Single Frame Sequence Reception

As Tachyon receives a frame, it stores the frame in the Inbound Data FIFO while it verifies the Cyclic Redundancy Check (CRC). If the CRC fails, Tachyon discards the frame. If the CRC passes, Tachyon notifies the ISM of the received frame.

The ISM checks the frame to determine if it is a single frame sequence (SFS). If it is, Tachyon uses the next available buffer in the Single Frame Sequence Buffer Queue (SFSBQ) and DMAs the SFS (Fibre Channel Header and a data payload) to the host via the Inbound Data Manager and the SFS Buffer Channel. If the entire SFS does not fit into one buffer, Tachyon continues packing the remaining data into the next available buffer until it becomes full. If the buffer becomes full. the ISM provides a new buffer and the process continues until the SFS is totally stored. When the DMA operation completes, the ISM transmits the ACK frame (if the frame is Class 1 or Class 2) that is associated with the SFS.

Figure 2.2 Receive Process Overview.

Next, the ISM generates an inbound sfs completion message and passes it through the Inbound Data Manager and Inbound Message Channel as an entry in the IMQ. After Tachyon sends the completion message, Tachyon then generates an interrupt to signal the host to process the received sequence. As its default, Tachyon generates interrupts for inbound sequences. For the host to avoid unnecessary interrupts, interrupt avoidance techniques can be used when any type of completion message is passed as an entry into the IMQ.

# 2.2.2 Multiframe Sequence, In Order Reception

As Tachyon receives a frame, it is stored in the Inbound Data FIFO while the CRC is verified. If the CRC fails, then the frame is discarded. If the CRC passes, the ISM is notified. The ISM first checks the frame to determine if it is a SFS, which in this case, it is not.

Next, the ISM checks if it is currently reassembling a multiframe sequence (MFS). If the ISM is already reassembling a multiframe sequence, the ISM checks the frame to determine whether the frame belongs to the current multiframe sequence. If it does not, the ISM generates a busy response (P\_BSY) to be sent to the remote node and the frame is discarded. The P\_BSY informs the remote node that Tachyon does not have the resources available to reassemble another sequence at this time. If Tachyon is in the Deferred P\_BSY mode, Tachyon does not automatically send a P\_BSY to the remote node. Refer to "2.2.4 Multiframe Sequence, Deferred P\_BSY Mode"

If the ISM receives a frame for a MFS when it is not currently reassembling a MFS, Tachyon DMAs the frame to host memory. The host uses buffers from the Multiframe Sequence Buffer Queue (MFSBQ) to reassemble a MFS. When Tachyon receives the first frame of the MFS, a new buffer is provided from the MFSBQ and the Fibre Channel Header information of the frame is moved into that buffer. Data payload of the frame is packed into the following buffer. As subsequent frames arrive, the ISM checks if each frame is the next expected frame of the sequence. Assuming that Tachyon receives the sequence in order, Tachyon discards the Fibre Channel Header and passes the remaining data payload to the host to be packed into buffers. As each new frame arrives, Tachyon processes it the same way. Tachyon packs the data payload into the current buffer until it becomes full. Once it becomes full, the ISM provides a new buffer and the process continues. As Tachyon receives each frame and moves it into host memory, the ISM sends the ACK frame (if the frame is Class 1 or Class 2) that is associated with the MFS.

When the last frame arrives, various fields in the Fibre Channel Header are saved in internal registers. Tachyon passes the last frame, with the Fibre Channel Header discarded, to the host. The ISM generates an inbound mfs completion message and passes it as an entry on the IMQ, and updates the IMQ Producer Index. After Tachyon sends the completion message to the host, Tachyon generates an interrupt to signal the host to process the received sequence. As its default, Tachyon generates interrupts for inbound sequences. To avoid unnecessary interrupts, the host can use interrupt avoidance techniques when any type of completion message is passed as an entry into the IMQ.

# 2.2.3 Multiframe Sequence, Out Of Order (OOO) Reception

The Out of Order Multiframe Reception operates the same as the in order multiframe reception until the first OOO frame arrives. When the ISM determines that the frame is OOO, it generates an inbound ooo completion message and passes it as an entry on the IMQ. Then the ISM restarts the reception by copying the entire OOO frame, including the Fibre Channel Header, and sending it to the host using new data buffers. Then the ISM processes the remaining frames in the sequence, assuming that the subsequent frames arrive in order. The ISM does not generate an interrupt until the entire sequence has arrived.

At each point of discontinuity, that is, when a new OOO frame arrives, Tachyon generates an inbound\_ooo completion message and uses a new buffer to re-start the reassembly.

# 2.2.4 Multiframe Sequence, Deferred P BSY Mode

Tachyon is designed to reassemble one MFS at a time. When Tachyon receives a frame for a new MFS while a current MFS is being reassembled, Tachyon generates a N\_Port busy response (P\_BSY) for the frame(s) of that new MFS. The remote node that receives the P\_BSY can retry the sequence later. Hopefully, when the remote node retries sending the sequence, Tachyon has completed the previous MFS so that it can accept the new MFS.

This process works well when Tachyon communicates with only one other remote node, e.g., a client in a client-server configuration. However, a server in a client-server configuration may be receiving MFS from many clients (remote nodes) at the same time. When Tachyon receives several new MFS frames, other than the current MFS being reassembled, the new frames are P BSY'd. The remote nodes resend the frames causing even more interference with the current MFS being reassembled. These excessive retries may cause the remote nodes to stop sending their MFS, which leads to upper layer error recovery overhead. This overhead can be reduced by using the Deferred P BSY mode.

In Deferred P\_BSY mode, the host sets the Disable AUTO P\_BSY bit in the Tachyon Configuration register so that Tachyon does not automatically send a P\_BSY to the remote node. When Tachyon receives a new MFS in Deferred P\_BSY mode, Tachyon sends the new MFS

frame to the host via the SFSBQ. Tachyon generates an inbound\_busied\_frame completion message. The host stores this frame in a Deferred P\_BSY queue.

When Tachyon receives all of the frames for the current MFS it is reassembling, it sets the Deferred ACK bit in the inbound mfs completion message and defers the final ACK generation to the host. Tachyon does this so that the host can send a P\_BSY to one of the waiting remote nodes. This operation allows one of the waiting remote nodes to retry its MFS before the current remote node can start a new MFS. In Deferred P\_BSY mode, Tachyon attempts to process MFSs in a way that all remote nodes have fair access.

# 2.3 SCSI Hardware Assists Overview

The ability to reassemble only one multiframe sequence may be sufficient for client-based or request reply networking traffic, but is not adequate for I/O traffic. A typical scenario is a host that is connected to many SCSI I/O devices. Because SCSI I/O devices are typically mechanical devices and are relatively slow compared to the host, a host may have hundreds or even thousands of active SCSI I/O transactions. Since it is possible to have many active SCSI I/O transactions, it is necessary to reassemble more than one inbound sequence at a time. By using Tachyon's SCSI hardware assists, the host is capable of concurrently reassembling 16,384 SCSIassisted sequences.

# 2.3.1 FCP Read for Tachyon as an Initiator

An FCP Read transaction is considered "inbound" for Tachyon as an initiator. When the initiator host wants to perform a Read transaction, it creates an entry in the host-based SCSI Exchange State Table (SEST). Each used entry in the SEST contains exchange state information for one SCSI I/O transaction. An Inbound SEST Entry contains a pointer to the SCSI Descriptor Block (SDB). The SDB is a list of pointers to empty buffers in host memory. The host pre-allocates these empty buffers to receive all the Read data for the exchange.

The initiator host sends an FCP\_CMND for a Read to the target. The FCP\_CMND requests the target to send the SCSI read data.

When the target is ready to transmit the SCSI read data to the initiator, it may send an FCP XFER RDY, which is an optional step for an FCP Read Exchange. When the initiator Tachyon receives the FCP\_XFER\_RDY, it discards it. When the initiator Tachyon receives a frame for the Read data sequence from the target, the initiator Tachyon operates in one of two modes, 1) Out of Order Reassembly mode or 2) In Order Reassembly mode. When the initiator host enables OOO Reassembly, then frames for a sequence from the target can arrive in any order. When the host enables In Order Reassembly, then frames must arrive in order.

For each frame received, Tachyon uses the Originator Exchange Identifier (OX\_ID) in the Fibre Channel Header as an index into the initiator host SEST. Once Tachyon has identified the appropriate Inbound SEST Entry, the ISM DMAs the SCSI read data to the host buffers. Tachyon continues receiving the data until all of the data is packed into host buffers.

In the final phase of the FCP Read, the initiator Tachyon receives a FCP\_RSP from the target. When the ISM receives the FCP RSP, it passes the FCP RSP to host memory via the SFSBQ. This FCP\_RSP notifies the host that the FCP Read transaction is complete. Then, the ISM generates an inbound scsi status completion message and passes this completion message as an entry on the IMQ. The ISM interrupts the host. The interrupt avoidance rules apply here as well.

The following figure illustrates the FCP Read process for Tachyon as an initiator:

### **HOST-BASED DATA STRUCTURES**

Figure 2.3 FCP Read for Tachyon as an Initiator.

# 2.3.2 FCP Read for Tachyon as a Target

An FCP Read exchange is considered "outbound" for Tachyon as a target. For FCP Read transactions for the target Tachyon, SCSI hardware assists are not used.

The target Tachyon receives an FCP CMND for an FCP Read from the initiator and passes it to the target host. The target host builds an EDB that defines where the Read data is located in the target host memory. The target host may program the target Tachyon to send an FCP XFER RDY via the OCQ to the initiator indicating that it is ready to send the Read data. The target host then programs the target Tachyon to send the requested SCSI read data via the OCQ to the initiator. When it is finished, the target host programs the target Tachyon to send an FCP RSP indicating that the FCP Read transaction is complete.

# 2.3.3 FCP Write for Tachyon as an Initiator

An FCP Write transaction is considered "outbound" for Tachyon as an initiator. When the initiator host wants to perform a Write transaction, it creates an Outbound SEST Entry. The Outbound SEST Entry contains a pointer to an EDB that points to the SCSI write data.

The initiator host sends an FCP\_CMND for a Write to the target. When the initiator Tachyon receives an FCP\_XFER\_RDY from the target, it checks the value of the DATA\_RO field. If the DATA\_RO is zero, the initiator Tachyon manages the Write transaction. If the DATA\_RO field is non-zero, Tachyon passes this FCP\_XFER\_RDY to the host. In this case, the initiator host is responsible for managing the data transfer.

When the initiator Tachyon sends all the Write data, it waits to receive an FCP\_RSP from the target. Initiator Tachyon passes the FCP\_RSP and an inbound\_scsi\_status\_completion message to the initiator host. This informs the host that the exchange completed.

# 2.3.4 FCP Write for Tachyon as a Target

An FCP Write exchange is considered "inbound" for Tachyon as a target. The target Tachyon receives an FCP CMND for an FCP Write from the initiator. The target host must create an SDB that points to an empty buffer that receives the Write data from the initiator. When the target host has allocated enough buffers and is ready to receive the data, it sends an FCP\_XFER\_RDY with the DATA RO field equal to zero to the initiator. If the target host is not ready to manage the entire requested Write transaction, it sends multiple FCP XFER RDYs to complete the transaction.

When the target Tachyon receives the SCSI write data, it operates in one of two modes, 1) Out of Order Reassembly mode or 2) In Order Reassembly mode. When the target Tachyon receives all of the data, the target Tachyon sends an inbound\_scsi\_data completion message to the IMQ of the target host. The target Tachyon then sends an FCP\_RSP to the initiator indicating that the exchange has completed.

# 3. Architectural Details

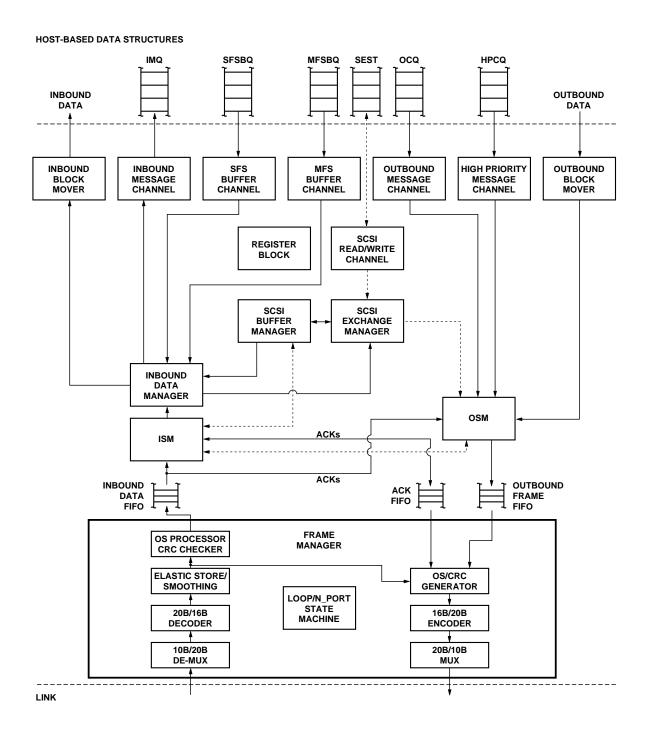

# 3.1 Tachyon Internal Block Diagram

The Tachyon Internal Block Diagram shows the high level chip architecture.

Figure 3.1 Tachyon Internal Block Diagram.

# 4. Tachyon Signal Descriptions

# 4.1 Tachyon Logic Symbol

Figure 4.1 Tachyon Logic Symbol.

# 4.2 Tachyon Pin-out

| D:  | D-17-1-1                            | D:  | D- 1 T-1-1   | D:  | D- 1 T-1-1   | D:  | D- 1 T-1-1           |

|-----|-------------------------------------|-----|--------------|-----|--------------|-----|----------------------|

| Pin | Pad Label                           | Pin | Pad Label    | Pin | Pad Label    | Pin | Pad Label            |

| 1   | Vdd2 (a)                            | 53  | Vdd          | 105 | Vdd2 (a)     | 157 | Vdd                  |

| 2   | Vss2 (e)                            | 54  | Vss2 (e)     | 106 | TAD[26]      | 158 | Vss                  |

| 3   | RX[8]                               | 55  | IDD_TEST (c) | 107 | TAD[27]      | 159 | TX[17]               |

| 4   | RX[9]                               | 56  | LP2          | 108 | TAD[28]      | 160 | TX[[19]              |

| 5   | RX[19]                              | 57  | PLLAGND      | 109 | Vdd          | 161 | L_UNUSE              |

| 6   | Vdd                                 | 58  | PLLVdd       | 110 | Vss          | 162 | TXCL_SEL             |

| 7   | Vss                                 | 59  | PLLVss       | 111 | TAD[29]      | 163 | Vdd2 (a)             |

| 8   | RX[17]                              | 60  | TAD[0]       | 112 | TAD[30]      | 164 | Vss                  |

| 9   | RX[15]                              | 61  | TAD[1]       | 113 | TAD[31]      | 165 | TBC                  |

| 10  | RX[13]                              | 62  | TAD[2]       | 114 | VDD2 (a)     | 166 | Vdd2 (a)             |

| 11  | Vdd2 (a)                            | 63  | Vdd          | 115 | Vss2 (e)     | 167 | Vss2 (e)             |

| 12  | Vss2 (e)                            | 64  | Vss          | 116 | TYPE[0]      | 168 | TX[1]                |

| 13  | RX[11]                              | 65  | TAD[3]       | 117 | TYPE[1]      | 169 | TX[3]                |

| 14  | RX[10]                              | 66  | TAD[4]       | 118 | TYPE[2]      | 170 | TX[5]                |

| 15  | EWRAP                               | 67  | TAD[5]       | 119 | PARITY       | 171 | Vss                  |

| 16  | Vdd2 (a)                            | 68  | Vdd2 (a)     | 120 | Vdd          | 172 | Vss                  |

| 17  | Vss2 (e)                            | 69  | Vss2 (e)     | 121 | Vss          | 173 | TX[7]                |

| 18  | RX[18]                              | 70  | TAD[6]       | 122 | TCK          | 174 | TX[0]                |

| 19  | RX[16]                              | 71  | TAD[7]       | 123 | Vss2 (e)     | 175 | TX[2]                |

| 20  | RX[14]                              | 72  | Vdd          | 124 | TMS          | 176 | Vss                  |

| 21  | Vdd                                 | 73  | Vss          | 125 | RSTN         | 177 | Vss                  |

| 22  | Vss                                 | 74  | TAD[8]       | 126 | TDI          | 178 | TX[4]                |

| 23  | RX[12]                              | 75  | TAD[9]       | 127 | Vss2 (e)     | 179 | TX[6]                |

| 24  | PAR_ID[1]                           | 76  | TAD[10]      | 128 | TDO          | 180 | TX[8]                |

| 25  | Vdd                                 | 77  | Vss          | 129 | Vss2 (e)     | 181 | Vdd                  |

| 26  | Vss2 (e)                            | 78  | Vss          | 130 | Vss2 (e)     | 182 | Vss                  |

| 27  | Vss                                 | 79  | Vdd          | 131 | Vdd2 (a)     | 183 | Vss                  |

| 28  | PREFETCH L                          | 80  | TAD[11]      | 132 | reserved (d) | 184 | TX[9]                |

| 29  | TBG L                               | 81  | TAD[12]      | 133 | reserved (d) | 185 | PAR ID[0]            |

| 30  | TBR L[1]                            | 82  | TAD[13]      | 134 | reserved (d) | 186 | Vss                  |

| 31  | TBR L[0]                            | 83  | TAD[14]      | 135 | Vdd          | 187 | Vss                  |

| 32  | Vdd2 (a)                            | 84  | Vdd2 (a)     | 136 | SCAN EN (d)  | 188 | RBC                  |

| 33  | Vss2 (e)                            | 85  | Vss2 (e)     | 137 | reserved (b) | 189 | Vdd                  |

| 34  | RESET L                             | 86  | TAD[15]      | 138 | reserved (b) | 190 |                      |

| 35  | INT L                               | 87  | TAD[16]      | 139 | reserved (b) | 191 | RX[1]                |

| 36  | ERROR L                             | 88  | Vdd          | 140 | TEST_MODE    | 193 | RX[3]                |

| 37  | Vdd2 (a)                            | 89  | Vss          | 141 | reserved (d) | 193 | RX[5]                |

| 38  | Vss2 (e)                            | 90  | TAD[17]      | 142 | Vdd2 (a)     | 194 | Vdd2 (a)             |

| 39  | RETRY L                             | 91  | TAD[18]      | 143 | Vss2 (e)     | 195 | Vss2 (e)             |

| 40  | READY L                             | 92  | TAD[19]      | 144 | TX[12]       | 196 | RX[7]                |

| 41  | AVCS L                              | 93  | Vdd2 (a)     | 145 | TX[14]       | 197 | LCKREF L             |

| 42  | Vdd                                 | 94  | Vss2 (e)     | 146 | TX[14]       | 198 | FAULT                |

| 43  | Vss                                 | 95  | TAD[20]      | 147 | Vdd2 (a)     | 199 | Vdd2 (a)             |

| 44  | PLL RSTN                            | 96  | TAD[21]      | 148 | Vss2 (e)     | 200 | Vuu2 (a)<br>Vss2 (e) |

| 45  | reserved (c)                        | 97  | TAD[22]      | 149 | TX[18]       | 200 | COM DET              |

| 46  | PLL_IDD_TEST (b)                    | 98  | Vdd          | 150 | TX[10]       | 201 | RX[0]                |

| 46  | PLL_IDD_TEST (b) PLL TEST DATA (b)  | 99  | Vss          | 151 | TX[11]       | 202 | RX[0]<br>RX[2]       |

|     | PLL_TEST_DATA (b) PLL TEST_MODE (c) |     |              | 151 |              | 203 |                      |

| 48  |                                     | 100 | TAD[23]      | _   | Vdd          |     | Vdd2 (a)             |

| 49  | Vdd                                 | 101 | TAD[24]      | 153 | Vss          | 205 | Vss                  |

| 50  | Vss                                 | 102 | TAD[25]      | 154 | TX[13]       | 206 | RX[4]                |

| 51  | SCLK                                | 103 | Vss2 (e)     | 155 | TX[15]       | 207 | RX[6]                |

| 52  | Vdd2 (a)                            | 104 | Vdd2 (a)     | 156 | Vdd2 (a)     | 208 | Vdd                  |

Table 4.1 Tachyon Pinout.

## **Tachyon Pinout Notes**

- (a) For most applications, Vdd and Vdd2 internal power straps may be connected on the printed circuit board (PCB). Refer to "A.3 PCB Layout Suggestions".

- (b) Pin has internal pull-up and may be left unconnected (solder pad only) or pulled up to Vdd (3.6 V) with a 4.7 k $\Omega$  resistor.

**WARNING** Do not pull up reserved pins to a voltage greater than Vdd (3.6 V)

- (c) Pin has internal pull-down and may be left unconnected (solder pad only) or connected to Vss.

- (d) Pin must be left unconnected.

- (e) For most applications, Vss and Vss2 may be connected on the PCB. Refer to "A.3 PCB Layout Suggestions".

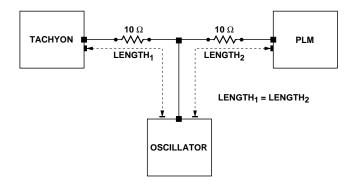

# 4.3 Physical Link Module (PLM) Interface

| Pin #   | I/O | Pad Label | Pad Name               | Description                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-----|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Various | 0   | TX[190]   | Transmit Data          | 10-bit or 20-bit transmit data bus to the PLM. For 10-bit PLMs, only the TX[90] outputs are used. The PAR_ID bit determines whether a 10-bit or 20-bit PLM should be used.                                                                                                                                                                                                          |

| 165     | I   | TBC       | Transmit Byte Clock    | 53.125 MHz or 26.5625 MHz clock (± 0.01% average tolerance) supplied by the oscillator. Note that for the TBC: 1) at 26 MHz, a maximum 40/60 duty cycle is allowed; 2) at 53 MHz, only a maximum 45/55 duty cycle is allowed.                                                                                                                                                       |

| Various | I   | RX[190]   | Receive Data           | 10-bit or 20-bit receive data bus from the PLM. For 10-bit PLMs, only the RX[90] outputs are used. The PAR_ID bit determines whether a 10-bit or 20-bit PLM should be used.                                                                                                                                                                                                         |

| 188     | I   | RBC       | Receive Byte Clock     | The receive byte clock signal is derived from the incoming data stream. The clock frequency is 53.125 MHz for 1063 Mbaud and 10-bit 531 Mbaud PLMs, and 26.5625 MHz for 10-bit 266 Mbaud PLMs (± 0.01%). 20-bit 531 Mbaud PLMs are not supported. Note that for RBC: 1) at 26 MHz, a maximum 40/60 duty cycle is allowed; 2) at 53 MHz, only a maximum 45/55 duty cycle is allowed. |

| 15      | 0   | EWRAP     | Electrical Wrap Enable | When asserted high by a host Write to the Frame Manager Configuration register, this signal tells the PLM to loopback the serialized transmit data to the receive deserializer. This signal is also used as a reset to internal logic on the PLM in response to a laser fault signal to perform recovery. An external loopback hood is not required for EWRAP.                      |

Table 4.2 Physical Link Module (PLM) Interface.

# 4.3 Physical Link Module (PLM) Interface (Continued)

| Pin # | I/O | Pad Label | Pad Name              |                    | Description                            |                                       |

|-------|-----|-----------|-----------------------|--------------------|----------------------------------------|---------------------------------------|

| 197   | О   | LCKREF_L  | Lock to Reference     |                    | ow, this signal pr                     |                                       |

|       |     |           |                       |                    | directing the rece                     |                                       |

|       |     |           |                       | _                  | its to obtain freq                     |                                       |

|       |     |           |                       |                    | the Transmit By                        |                                       |

|       |     |           |                       |                    | rted low, this sig                     |                                       |

|       |     |           |                       |                    | its PLL to the TI                      |                                       |

| 201   | I   | COM_DET   | Comma Detect          |                    | nigh by the PLM,                       |                                       |

|       |     |           |                       |                    | K28.5 control c                        |                                       |

|       |     |           |                       |                    | of positive disp                       |                                       |

|       |     |           |                       |                    | detected on the l                      |                                       |

|       |     |           |                       | on the Receive I   | me time as the da                      | ata is presented                      |

| 1.01  | т т | I IMILION | Tinle II              |                    |                                        |                                       |

| 161   | I   | L_UNUSE   | Link Unusable         |                    | nigh, this signal i                    |                                       |

|       |     |           |                       |                    | ble for data tran<br>r being received. | · · · · · · · · · · · · · · · · · · · |

| 198   | I   | FAULT     | Fault                 |                    |                                        |                                       |

| 198   | 1   | FAULI     | raun                  |                    | nigh, this signal is detected on the   |                                       |

|       |     |           |                       |                    | proper power lev                       |                                       |

|       |     |           |                       | on the laser.      | Toper power levi                       | er nas occurred                       |

| 162   | 0   | TXCLK SEL | Transmit Clock Select |                    | clock frequency                        | the external                          |

| 102   |     | TACER_SEE | Transmit Clock Sciect |                    | ng hardware sho                        |                                       |

|       |     |           |                       |                    | rived from the P.                      |                                       |

|       |     |           |                       | TXCLK SEL          | Clock Fre                              |                                       |

|       |     |           |                       | 0                  | 53.1250                                |                                       |

|       |     |           |                       | 1                  | 26.5625                                |                                       |

| 24    | I   | PAR_ID[1] | Parallel ID           | These two bits a   | re asserted by th                      | e PLM to indi-                        |

| 185   |     | PAR_ID[0] |                       | cate the link rate | e and assumed in                       | terface width                         |

|       |     |           |                       |                    | y are interpreted                      | by Tachyon as                         |

|       |     |           |                       | follows.           |                                        |                                       |

|       |     |           |                       | PAR_ID[10]         | Link Rate                              | Data Width                            |

|       |     |           |                       | 01                 | 265.625 MHz                            | 10 bits                               |

|       |     |           |                       | 10                 | 531.25 MHz                             | 10 bits                               |

|       |     |           |                       | 11                 | 1062.5 MHz                             | 20 bits                               |

Table 4.2 Physical Link Module (PLM) Interface.

# Note:

Tachyon supports GLMs that conform to the FCSI-301-Revision 1.0 GLM family.

# 4.4 PLL External Connections

Tachyon contains a PLL which is used for internal functionality. This section describes how the external pins of this PLL should be connected.

| Pin # | I/O | Pad Label     | Pad Name                                    | Description                                                                                                                                                                                                           |

|-------|-----|---------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44    | I   | PLL_RSTN      | PLL Reset                                   | When asserted low, this signal is the reset signal for the PLL. During normal operation this pin should be left unconnected. This pin has an internal pull-up.                                                        |

| 46    | I   | PLL_IDD_TEST  | PLL Quiescent Current<br>(IDDQ) Test Enable | This pin has an internal pull-up. Refer to "LSI's LCB500K Design Manual, 1994, sections 3.24 and 3.6.3 (IDD Test)" for usage.                                                                                         |

| 47    | I   | PLL_TEST_DATA | PLL Test Data Input                         | This pin controls the system clock when PLL_TEST_MODE is asserted high. This pin has an internal pull-up.                                                                                                             |

| 48    | I   | PLL_TEST_MODE | PLL Test Mode Select                        | When asserted high, the PLL's VCO output is bypassed, and PLL_TEST_DATA drives the system clock. This pin has an internal pulldown.                                                                                   |

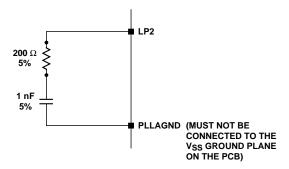

| 56    | I   | LP2           | PLL External RC<br>Network                  | This pin is used for external RC circuitry of the PLL. This pin should be connected to a $200\Omega$ 5% resistor, 1nF 5% capacitor, and the PLLAGND pin in series. Refer to "7.6 External PLL Components" on page 99. |

| 57    | I   | PLLAGND       | PLL Analog Ground                           | This pin is used for external RC circuitry of the PLL. This pin should be connected to a 1nF 5% capacitor, 200 $\Omega$ 5% resistor, and the LP2 pin in series. Refer to "7.6 External PLL Components" on page 99.    |

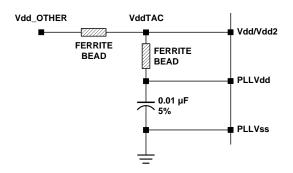

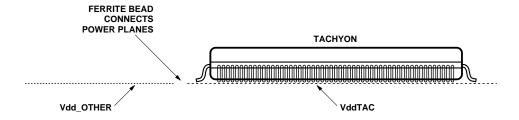

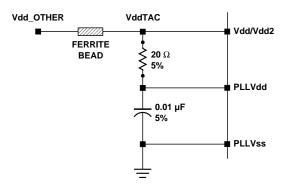

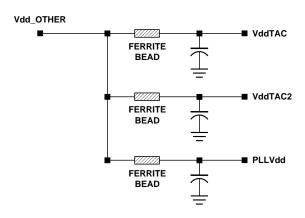

| 58    | I   | PLLVdd        | PLL Vdd                                     | This pin should be connected to a Vdd source via ferrite bead with capacitor to Vss. For additional details and alternative methods of connecting this pin, refer to "A.3 PCB Layout Suggestions" on page 106.        |

| 59    | I   | PLLVss        | PLL Vss                                     | This pin should be connected to a Vss source. Refer to "A.3 PCB Layout Suggestions" on page 106.                                                                                                                      |

Table 4.3 PLL External Connections.

# 4.5 JTAG 1149.1 Scan Test Interface

| Pin # | I/O | Pad Label | Pad Name                                           | Description                                                                                                                                                                                                  |

|-------|-----|-----------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55    | I   | IDD_TEST  | Boundary Scan<br>(JTAG) Cells' IDDQ<br>Test Enable | This pin has an internal pulldown. Refer to LSI or "LSI's LCB500K Design Manual, 1994, p. 13-82" for details.                                                                                                |

| 122   | I   | TCK       | Test Clock                                         | Transitions the Test Access Port (TAP) state machine to the next state on the rising edge of this signal. If not used, leave unconnected or pull up with a $4.7~\mathrm{k}\Omega$ resistor to Vdd.           |

| 124   | I   | TMS       | Test Mode Select                                   | This signal determines the next state of the TAP state machine. If not used, leave unconnected or pull up with a 4.7 k $\Omega$ resistor to Vdd.                                                             |

| 125   | I   | RSTN      | TAP Reset                                          | When asserted low, the TAP controller and RAM BIST are reset. If not used, leave unconnected or pull up with a 4.7 k $\Omega$ resistor to Vdd.                                                               |

| 126   | I   | TDI       | Test Data In                                       | Used to scan data serially into the boundary register cells. If not used, leave unconnected or pull up with a 4.7 $\Omega$ resistor to Vdd.                                                                  |

| 128   | 0   | TDO       | Test Data Out                                      | Used to scan data serially from the boundary register cells. If not used, leave unconnected or pull up with a 4.7 k $\Omega$ resistor to Vdd.                                                                |

| 136   | I   | SCAN_EN   | Internal Scan Chain<br>Enable                      | This pin has an internal pulldown. Assert this pin high when performing internal scan chain tests.                                                                                                           |

| 140   | I   | TEST_MODE | Test Enable                                        | When asserted high, this control signal tristates all pins on the Tachyon package, with the exception of "reserved" pins 132, 133, 134, and 141. If not used, connect Vss through a 4.7 k $\Omega$ resistor. |

Table 4.4 JTAG Scan Test Interface.

# 4.5.1 JTAG Instructions

| Instruction | Instruction Type | Encoding |

|-------------|------------------|----------|

| Bypass      | Mandatory        | 11111    |

| Extest      | Mandatory        | 00000    |

| Sample      | Mandatory        | 00001    |

| Clamp       | Optional         | 00110    |

| High-z      | Optional         | 00111    |

Table 4.5 JTAG Instructions.

For information on the use of JTAG Boundary Scan, refer to the "IEEE 1149.1 Boundary Scan specification".

# 4.6 Tachyon System Interface (TSI)

This section describes the Tachyon System Interface for the Tachyon Fibre Channel chip. Included in this discussion is a description of the signals as well as a description of the protocol used across this interface.

# 4.6.1 TSI Signal List

| Pin #             | I/O | Pad Label                     | Pad Name                     | Description                                                                                                                                                                                                                                                                                                           |

|-------------------|-----|-------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Various           | I/O | TAD[310]                      | Multiplexed Address/<br>Data | Address is driven by the transaction master during the address phase. The master drives only word addresses, so only bits TAD[312] contain useful information; however, parity must be generated for TAD[310]. During the data cycles(s), data is driven by the device being read or by the device mastering a write. |

| 119               | I/O | PARITY                        | Parity Information           | This bi-directional signal carries parity information for address and data on the TSI. Parity is optional, and is defined by the Parity Even (bit 1) and Parity Enable (bit 2) bits in the Tachyon Configuration register.                                                                                            |

| 41                | I/O | AVCS_L                        | Address Valid Chip<br>Select | This signal is driven by the master of a transaction during the address phase.                                                                                                                                                                                                                                        |

| 118<br>117<br>116 | I/O | TYPE[2]<br>TYPE[1]<br>TYPE[0] | Transaction Types            | Asserted low by the master of a transaction. TYPE indicates the size and direction of the transaction. Refer to "6.1.1 TSI Transaction Types" on page 60.                                                                                                                                                             |

| 40                | I/O | READY_L                       | Device Ready                 | Asserted by a transaction responder when a transaction is complete. Refer to "6.1.7 Driving Bi-Directional Signals" on page 62. More information about READY_L is available in "4.6 Tachyon System Interface (TSI)" and "6.2 TSI Functional Waveforms".                                                               |

| 39                | I   | RETRY_L                       | Read Retry                   | Asserted by the host to terminate a read request if the read data cannot be available to Tachyon.                                                                                                                                                                                                                     |

| 28                | 0   | PREFETCH_L                    | Prefetch Request             | Asserted low by Tachyon to signal that the next sequential data will be read. This signal may be active during retry. Refer to "6.1.9 Read Transactions" on page 62.                                                                                                                                                  |

| 36                | 0   | ERROR_L                       | Error Out                    | Asserted low by Tachyon to indicate a bus parparity error, protocol error, or internal parity error.                                                                                                                                                                                                                  |

| 35                | О   | INT_L                         | Interrupt                    | Asserted low by Tachyon to signal that a message has been posted to the host.                                                                                                                                                                                                                                         |

| 34                | I   | RESET_L                       | Synchronous Reset            | Asserted low by the host to perform a hard reset of Tachyon. RESET_L must be held low for a minimum of 10 clock periods. All configuration information is lost on reset.                                                                                                                                              |

Table 4.6 TSI Signal List.

# 4.6.1 TSI Signal List (Continued)

| Pin # | I/O | Pad Label | Pad Name     | Description                                     |

|-------|-----|-----------|--------------|-------------------------------------------------|

| 30    | О   | TBR_L[1]  | Bus Requests | One bus request signal is asserted when         |

| 31    |     | TBR_L[0]  |              | Tachyon needs to master a transaction.          |

|       |     |           |              | TBR_L[1] indicates a read using the pre-        |

|       |     |           |              | fetched channel. TBR_L[0] is used for writes    |

|       |     |           |              | and non-prefetched reads. If only one bus       |

|       |     |           |              | request signal is desired, these two active low |

|       |     |           |              | signals should be ANDed together, external to   |

|       |     |           |              | the chip. Refer to "6.1.16 Arbitration" on page |

|       |     |           |              | 66.                                             |

| 29    | I   | $TBG_L$   | Bus Grant    | Asserted low by the host to signal acceptance   |

|       |     |           |              | of Bus Request.                                 |

| 51    | I   | SCLK      | System Clock | 24-40 MHz system clock used to drive the        |

|       |     |           |              | backplane side of Tachyon.                      |

Table 4.6 TSI Signal List.

# 5. Registers5.1 Register Overview

| Register Name                                  | Read/<br>Write | Address     | Reset Value   |

|------------------------------------------------|----------------|-------------|---------------|

| OCQ Base register                              | W              | 0x0000      | 0x00000000    |

| OCQ Length register                            | W              | 0x0004      | 0x00000000    |

| OCQ Producer Index register                    | W              | 0x0008      | 0x00000000    |

| OCQ Consumer Index Address register (3)        | W              | 0x000C      | 0x00000000    |

| Host's Copy of Tachyon's OCQ Consumer Index    | R              | host memory |               |

| HPCQ Base register                             | W              | 0x0040      | 0x00000000    |

| HPCQ Length register                           | W              | 0x0044      | 0x00000000    |

| HPCQ Producer Index register                   | W              | 0x0048      | 0x00000000    |

| HPCQ Consumer Index Address register (3)       | W              | 0x004C      | 0x00000000    |

| Host's Copy of Tachyon's HPCQ Consumer Index   | R              | host memory |               |

| IMQ Base register                              | W              | 0x0080      | 0x00000000    |

| IMQ Length register                            | W              | 0x0084      | 0x00000000    |

| IMQ Consumer Index register                    | W              | 0x0088      | 0x00000000    |

| IMQ Producer Index Address register (3)        | W              | 0x008C      | 0x00000000    |

| Host's Copy of Tachyon's IMQ Producer Index    | R              | host memory |               |

| MFSBQ Base register                            | W              | 0x00C0      | 0x00000000    |

| MFSBQ Length register                          | W              | 0x00C4      | 0x00000000    |

| MFSBQ Producer Index register                  | W              | 0x00C8      | 0x00000000    |

| MFSBQ Consumer Index register                  | R              | 0x00CC      | 0x00000000    |

| MFS Buffer Length register                     | W              | 0x00D0      | 0x00000000    |

| SFSBQ Base register                            | W              | 0x0100      | 0x00000000    |

| SFSBQ Length register                          | W              | 0x0104      | 0x00000000    |

| SFSBQ Producer Index register                  | W              | 0x0108      | 0x00000000    |

| SFSBQ Consumer Index register                  | R              | 0x010C      | 0x00000000    |

| SFS Buffer Length register                     | W              | 0x0110      | 0x00000000    |

| SEST Base register                             | W              | 0x0140      | 0x00000000    |

| SEST Length register                           | W              | 0x0144      | 0x00000000    |

| SCSI Buffer Length register                    | W              | 0x0148      | 0x00000000    |

| Tachyon Configuration register                 | R/W            | 0x0184      | 0x00000002    |

| Tachyon Control register                       | W              | 0x0188      | 0x00000000    |

| Tachyon Status register                        | R              | 0x018C      | HW dependent  |

| Tachyon Flush SEST Cache Entry register        | R/W            | 0x0190      | 0x00000000    |

| Tachyon EE_Credit Zero Timer register          | R              | 0x0194      | 0x00000000 (2 |

| Tachyon BB_Credit Zero Timer register          | R              | 0x0198      | 0x00000000 (2 |

| Tachyon Receive Frame Error Counter register   | R              | 0x019C      | 0x00000000    |

| Frame Manager Configuration register           | R/W            | 0x01C0      | 0x00000000    |

| Frame Manager Control register                 | W              | 0x01C4      | 0x00000000    |

| Frame Manager Status register                  | R              | 0x01C8      | 0x00000000    |

| Frame Manager RT_TOV/AL_TIME & ED_TOV register | W              | 0x01CC      | 0x001001F5    |

Table 5.1 Tachyon Memory Map.

# 5.1 Register Overview (Continued)

| Register Name                                 | Read/<br>Write | Address | Reset Value |

|-----------------------------------------------|----------------|---------|-------------|

| Frame Manager Link Error Counters #1 register | R              | 0x01D0  | 0x00000000  |

| Frame Manager Link Error Counters #2 register | R              | 0x01D4  | 0x00000000  |

| Frame Manager World Wide Name Hi register     | R/W            | 0x01E0  | 0x00000000  |

| Frame Manager World Wide Name Lo register     | R/W            | 0x01E4  | 0x00000000  |

| Frame Manager Received AL_PA register         | R              | 0x01E8  | 0x00000000  |

| Frame Manager Primitive register              | W              | 0x01EC  | 0x00000000  |

Table 5.1 Tachyon Memory Map. (Continued)

## **Tachyon Memory Map Notes**

- 1. At reset, Tachyon clears all registers to zero, unless otherwise noted. Reset is defined as power-on, a hardware reset, or a software reset.

- 2. While Tachyon clears registers to zero at reset, certain registers (such as EE\_Credit Zero Timer and BB\_Credit Zero Timer registers) begin counting up immediately following a reset. As a result, if the host reads a register immediately after a reset, the value may be non-zero.

- 3. If the host reads an invalid or Write only (W) register, the transaction completes normally, and Tachyon returns 0x000000000.

- 4. Tachyon ignores bits 31..9 of the address during register accesses.

- 5. If the host writes to Read only (R) registers, the transaction completes but Tachyon does not write the data to the register.

- 6. Some Tachyon registers contain bits that indicate a certain parameter is either active or inactive. For most cases, 1=active and 0=inactive, but there are exceptions. Refer to the detailed description of each register bit for specifics.

# 5.2 Length Register Values

The following table summarizes the programmed values for length registers.  $% \left( 1\right) =\left( 1\right) \left( 1\right)$

| Length Register Name                                | Length<br>(n)                                                                            | Programmed<br>Length Field<br>Value<br>(n-1) | Minimum<br>Programmed<br>Value | Maximum<br>Programmed<br>Value |

|-----------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------|--------------------------------|

| OCQ Length register                                 | The Number of OCQ Queue Entries (Must be a power of 2)                                   | n-1                                          | 1                              | 255                            |

| HPCQ Length register                                | The Number of<br>HPCQ Queue Entries<br>(Must be a power of 2)                            | n-1                                          | 1                              | 255                            |

| IMQ Length register                                 | The Number of IMQ Queue Entries (Must be a power of 2)                                   | n-1                                          | 3                              | 255                            |

| MFSBQ Length register                               | The Number of MFSBQ Queue Entries (Must be a power of 2)                                 | n-1                                          | 1                              | 255                            |

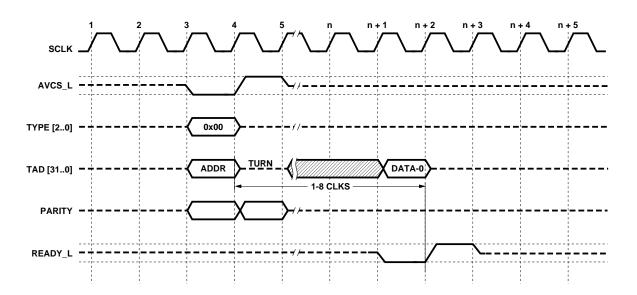

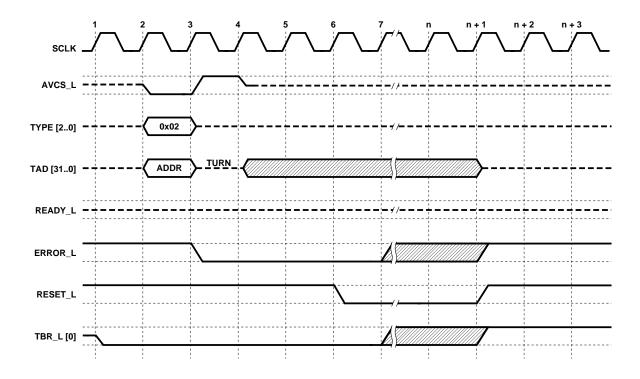

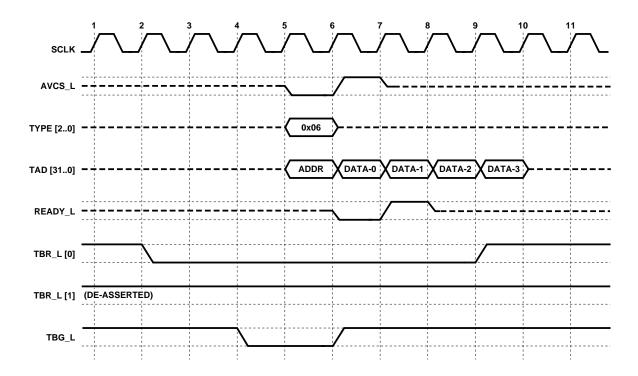

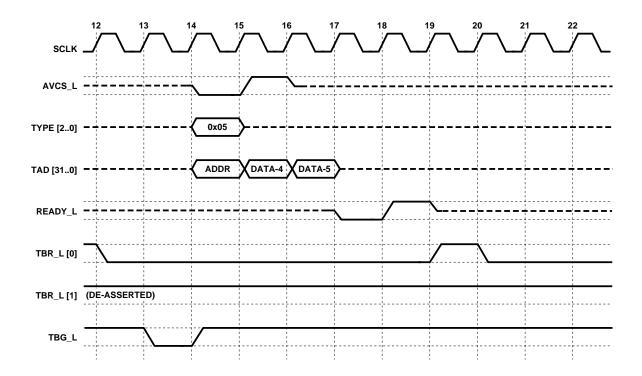

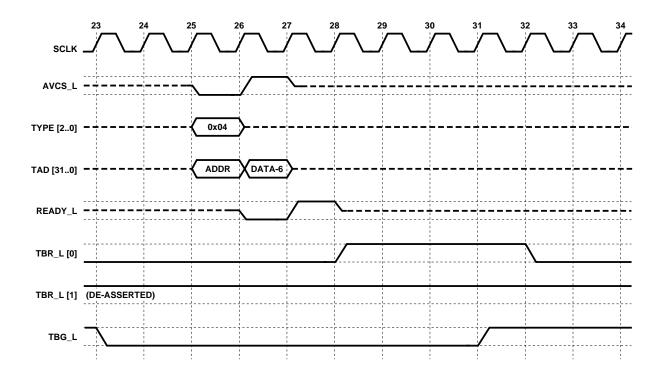

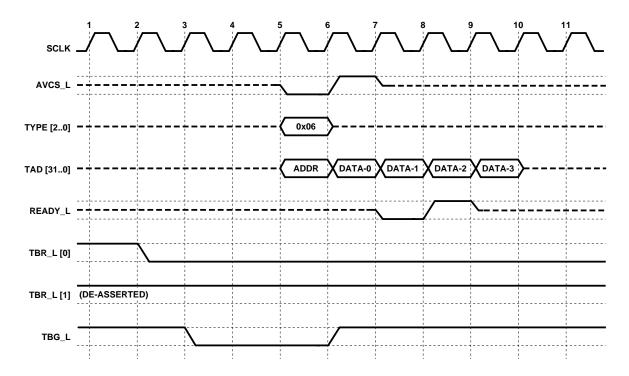

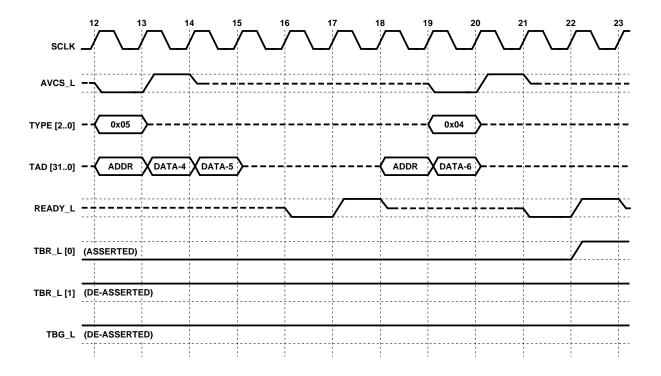

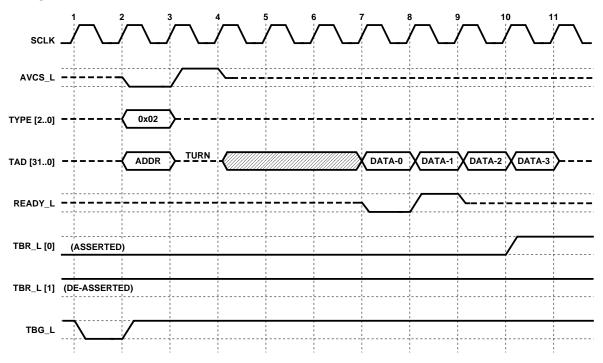

| MFS Buffer Length register                          | The Number of Bytes of<br>the MFS Receive Buffers<br>(Must be a power of 2)              | n-1                                          | 511                            | 65,535                         |