# R0P7760TH002TRK

**General Information Manual**

SH7760 T-Engine Development Kit

Rev.1.00

#### Cautions

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas

Technology Corporation product best suited to the customer's application; they do not convey any license under

any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third

party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corporation by various means,

- including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please he sure to evaluate all information as a total system before making a final

- programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

## **Precautions for Safety**

## **Definitions of Signal Words**

In both the General Information Manual and on the product itself, several icons are used to insure proper handling of this product and also to prevent injuries to you or other persons, or damage to your properties.

This chapter describes the precautions which should be taken in order to use this product safely and properly. Be sure to read this chapter before using this product.

This symbol represents a warning about safety. It is used to arouse caution about a potential danger that will possibly inflict an injury on persons. To avoid a possible injury or death, please be sure to observe the safety message that follows this symbol.

**DANGER** indicates an imminently dangerous situation that will cause death or heavy wound unless it is avoided. However, there are no instances of such danger for the product presented in this manual.

**WARNING** indicates a potentially dangerous situation that will cause death or heavy wound unless it is avoided.

**CAUTION** indicates a potentially dangerous situation that will cause a slight injury or a medium-degree injury unless it is avoided.

**CAUTION**

**CAUTION** with no safety warning symbols attached indicates a potentially dangerous situation that will cause property damage unless it is avoided.

**IMPORTANT**

This is used in operation procedures or explanatory descriptions to convey exceptional conditions or cautions to the user.

In addition to the five above, the following are also used as appropriate.

△means WARNING or CAUTION.

Example:

Omeans PROHIBITION.

Example:

means A FORCIBLE ACTION.

Example:

## **⚠ WARNING**

#### Warnings for AC Power Supply:

- If the attached AC power cable does not fit the receptacle, do not alter the AC power cable and do not plug it forcibly. Failure to comply may cause electric shock and/or fire.

- Use an AC power cable which complies with the safety standard of the country.

- Do not touch the plug of the AC power cable when your hands are wet. This may cause electric shock.

- This product is connected signal ground with frame ground. If your developing product is transformless (not having isolation transformer of AC power), this may cause electric shock. Also, this may give an unrepairable damage to this product and your developing one.

While developing, connect AC power of the product to commercial power through isolation transformer in order to avoid these dangers.

- If other equipment is connected to the same branch circuit, care should be taken not to overload the circuit.

- When installing this equipment, insure that a reliable ground connection is maintained.

- If you smell a strange odor, hear an unusual sound, or see smoke coming from this product, then

disconnect power immediately by unplugging the AC power cable from the outlet.

Do not use this as it is because of the danger of electric shock and/or fire. In this case, contact your

local distributor.

- Before setting up this product and connecting it to other devices, turn off power or remove a power cable to prevent injury or product damage.

#### Warnings to Be Taken for This Product:

- Do not disassemble or modify this product. Personal injury due to electric shock may occur if this

product is disassembled and modified. Disassembling and modifying the product will void your

warranty.

- Make sure nothing falls into the cooling fan on the top panel, especially liquids, metal objects, or anything combustible.

#### Warning for Installation:

• Do not set this product in water or areas of high humidity. Make sure that the product does not get wet. Spilling water or some other liquid into the product may cause unrepairable damage.

#### Warning for Use Environment:

This equipment is to be used in an environment with a maximum ambient temperature of 35°C. Care should be taken that this temperature is not exceeded.

## **⚠** CAUTION

Note on Connecting the Power Supply:

- Do not use any power cable other than the one that is included with the product.

- The power cable included with the product has its positive and negative poles color-coded by red and black, respectively.

- Pay attention to the polarities of the power supply. If its positive and negative poles are connected in reverse, the internal circuit may be broken.

- Do not apply any voltages exceeding the product's rated power supply voltage (5.0 V ±5%). Extreme voltages may cause a burn due to abnormal heat or cause the internal circuit to break down.

Cautions to Be Taken for Handling This Product:

- Use caution when handling the main unit. Be careful not to apply a mechanical shock.

- Do not touch the connector pins of the product main unit and the target MCU connector pins directly. Static electricity may damage the internal circuits.

- Excessive flexing or force of the flexible cable for connecting this product to the emulation probe may break connector.

Cautions to Be Taken for System Malfunctions:

- If the product malfunctions because of interference like external noise, do the following to remedy the trouble.

- (1) Press the RESET button on the board.

- (2) If normal operation is not restored after step (1), shut OFF the product once and then reactivate it.

## Content

| Precautions for Safety                         | 1  |

|------------------------------------------------|----|

| 1. Outline                                     |    |

| 1.1 Package Components                         | 8  |

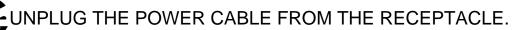

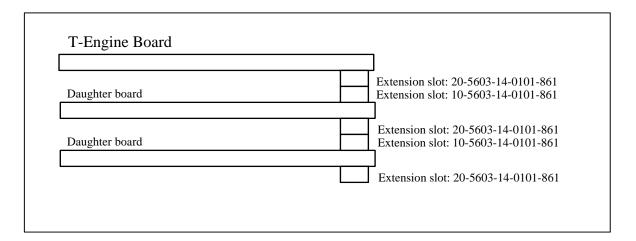

| 1.2 System Configuration                       | 9  |

| 1.2.1 T-Engine Features                        | 9  |

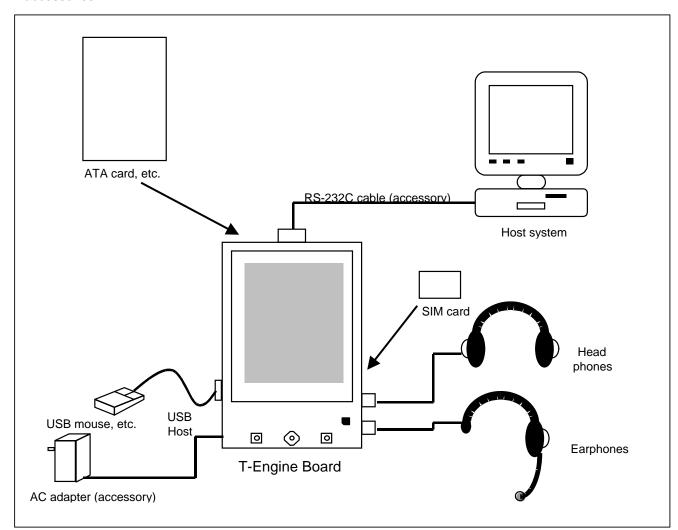

| 1.2.2 T-Engine Configuration                   | 9  |

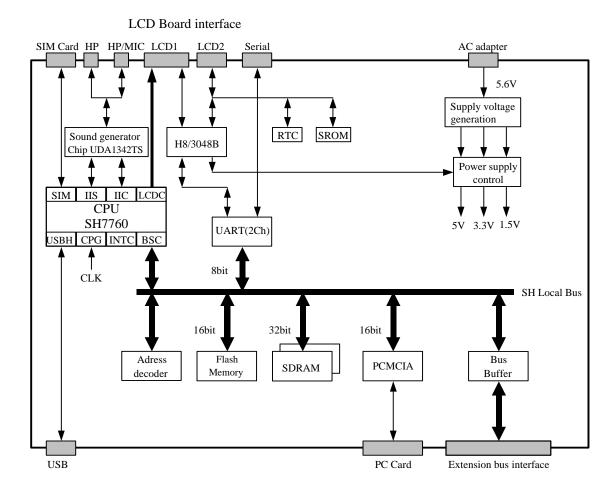

| 1.3 T-Engine Appearance                        | 11 |

| 1.4 T-Engine Specifications                    | 15 |

| 2. Installation                                | 17 |

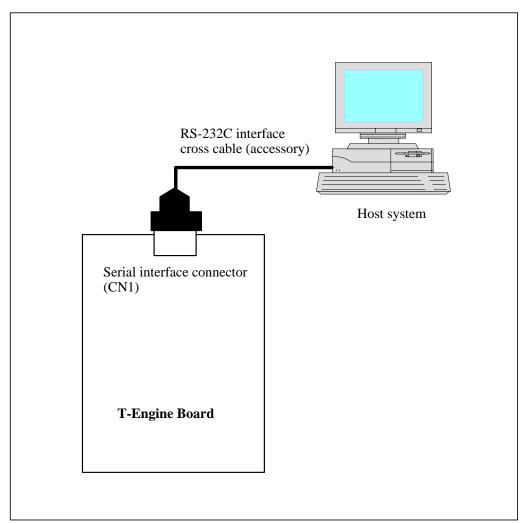

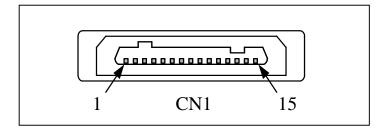

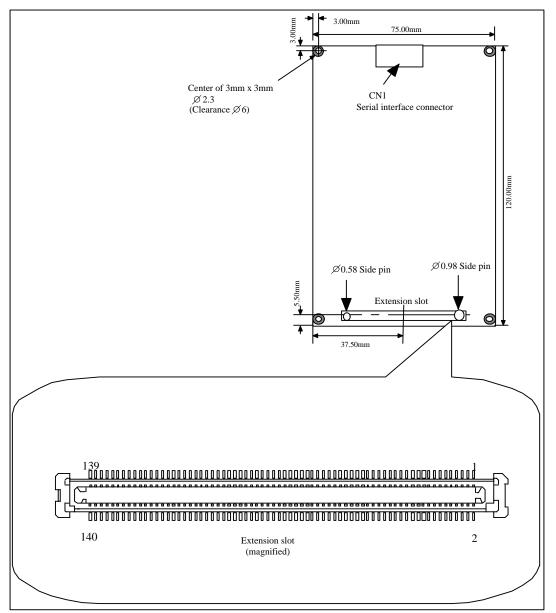

| 2.1 Host System Connection                     | 17 |

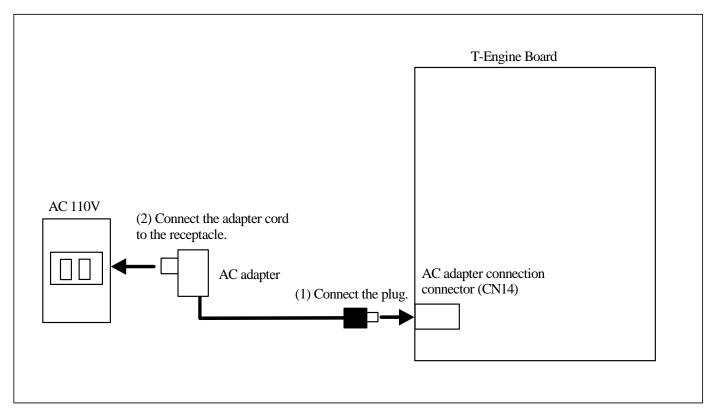

| 2.2 AC Adapter Connection                      | 18 |

| 2.3 Turning ON or OFF the T-Engine Board       | 19 |

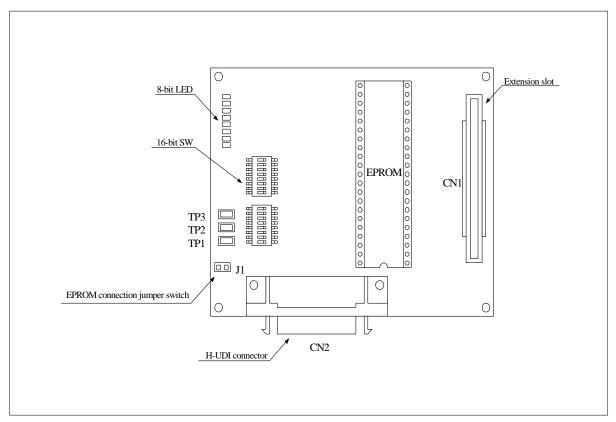

| 2.4 Using the Debug Board                      | 19 |

| 2.4.1 Debug Board Function                     | 19 |

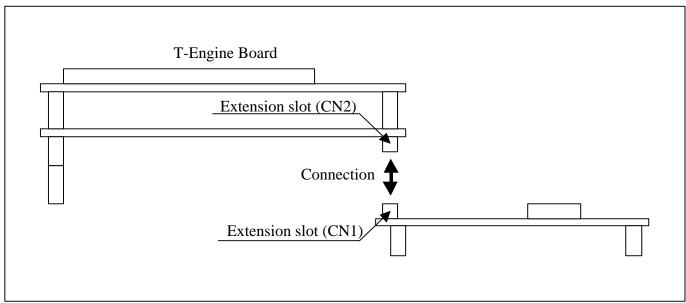

| 2.4.2 Debug Board Connection                   | 20 |

| 2.4.3 Debug Board Jumper Switches              | 21 |

| 2.4.4 8-bit LEDs on the Debug Board            | 21 |

| 2.4.5 16-bit SWs on the Debug Board            | 21 |

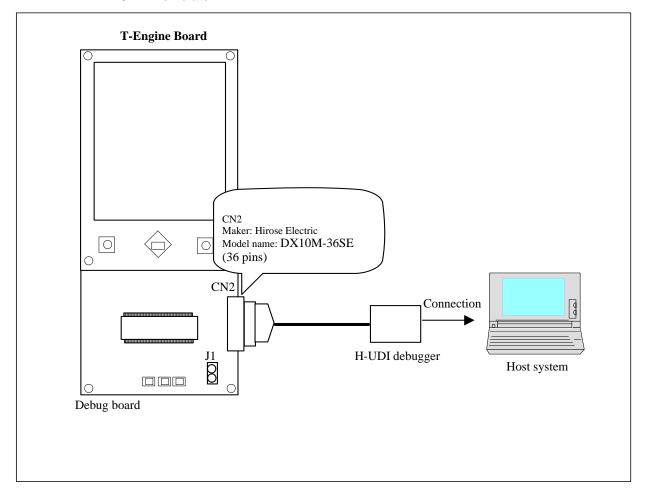

| 2.4.6 H-UDI Debugger Connection                | 22 |

| 3. Switches                                    | 23 |

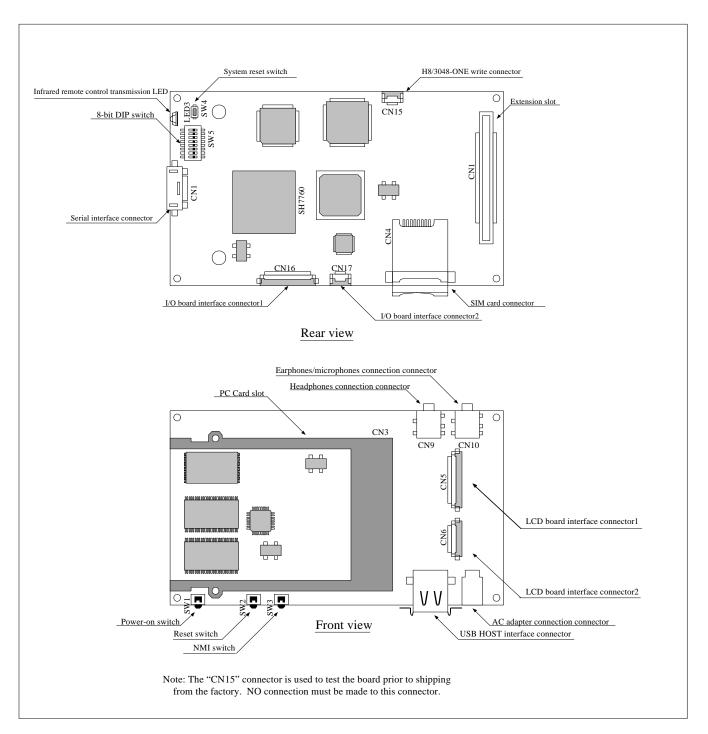

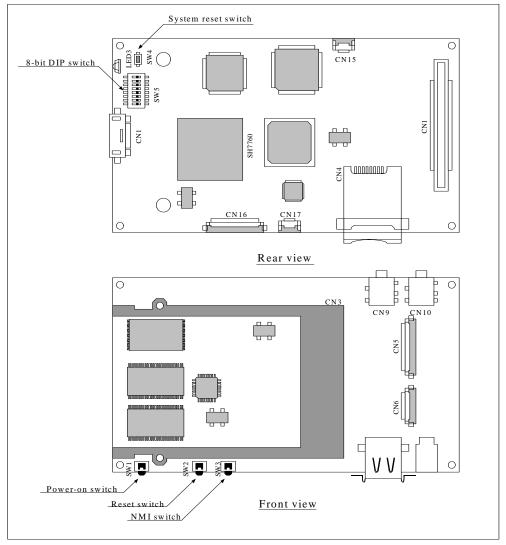

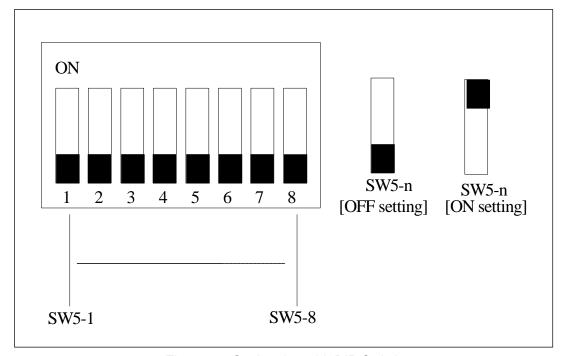

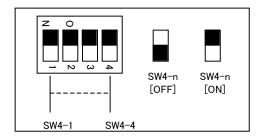

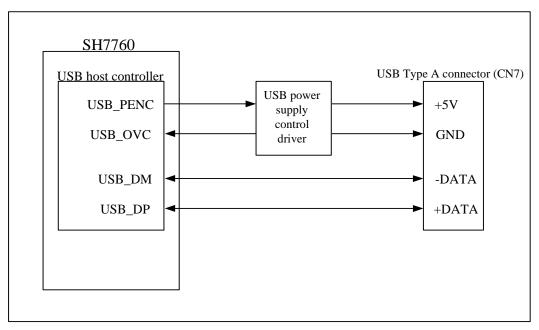

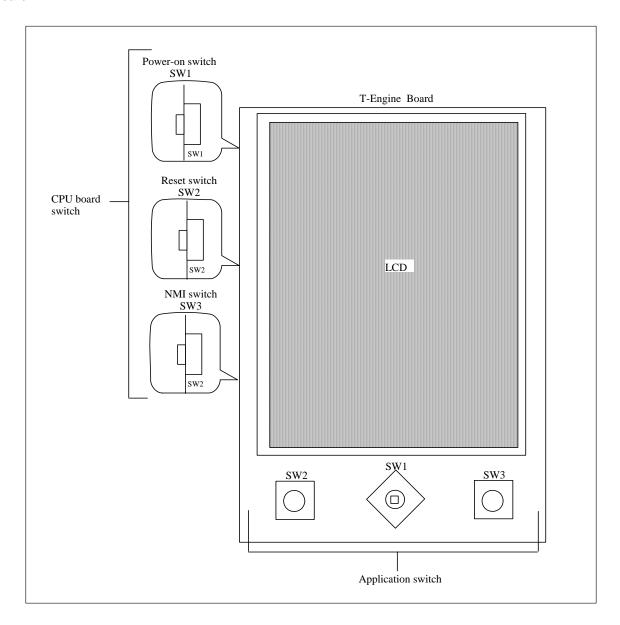

| 3.1 CPU Board Switches                         | 23 |

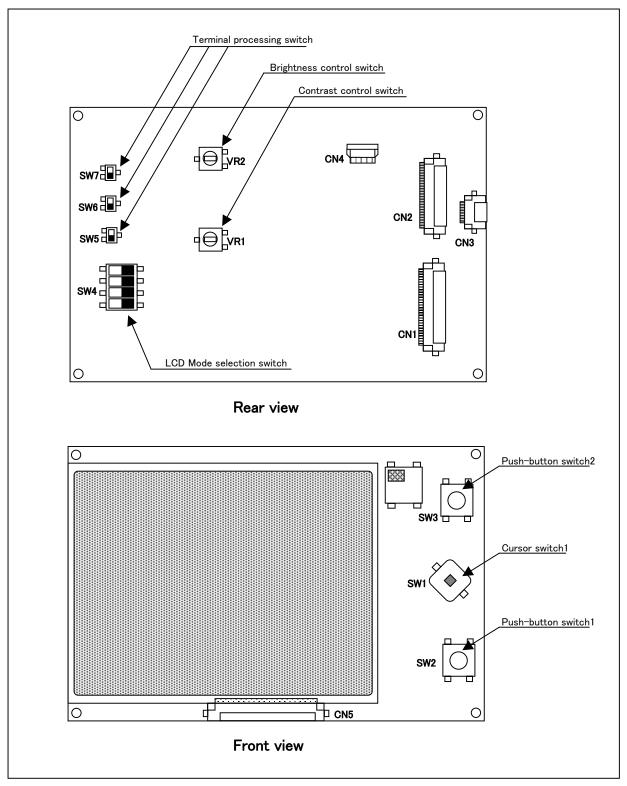

| 3.2 LCD Board Switch                           | 25 |

| 3.2.1 Application Switch                       | 25 |

| 3.2.2 LCD configuration switch                 | 25 |

| 4. Memory Map                                  | 27 |

| 4.1 Memory Map for the T-Engine Board          | 27 |

| 4.2 Memory Map during Debug Board Connection   | 28 |

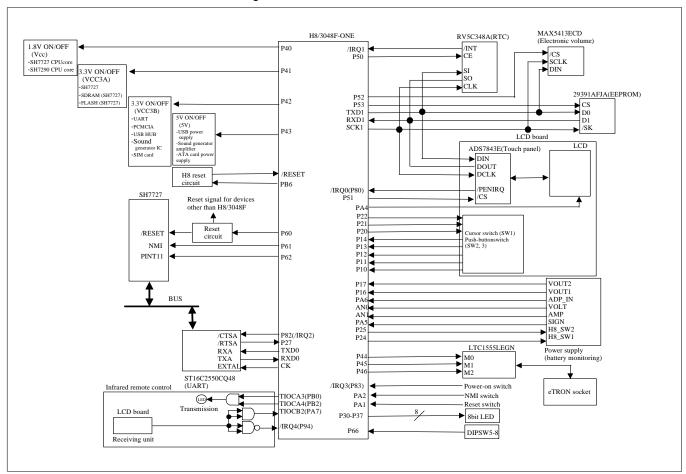

| 5. Functional Blocks                           | 30 |

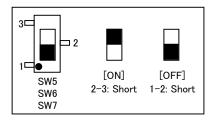

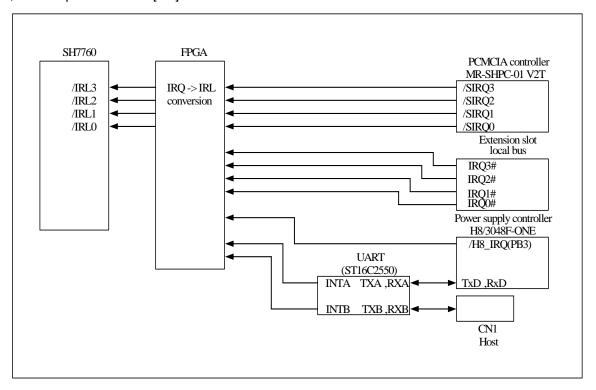

| 5.1 PCMCIA                                     | 30 |

| 5.1.1 Block Description                        | 30 |

| 5.1.2 Connector Pins                           | 31 |

| 5.1.3 Register Map                             | 33 |

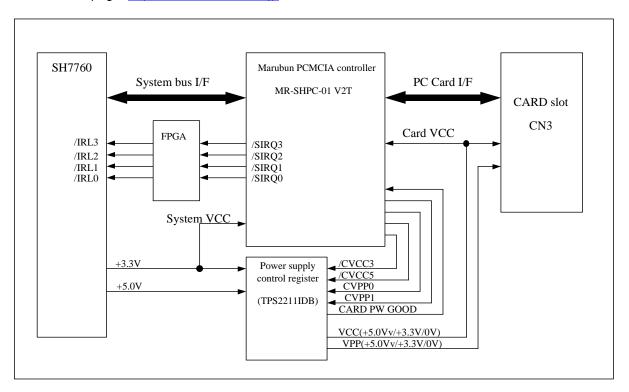

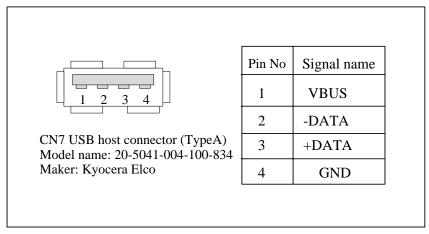

| 5.2 USB Host                                   | 34 |

| 5.2.1 Block Description                        | 34 |

| 5.2.2 Connector Pins                           | 35 |

| 5.2.3 Register Map                             | 35 |

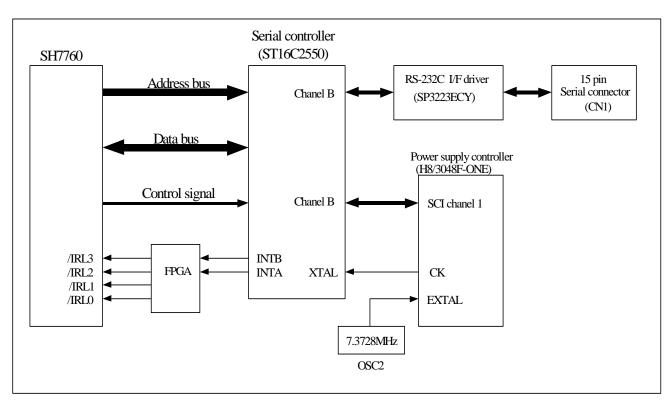

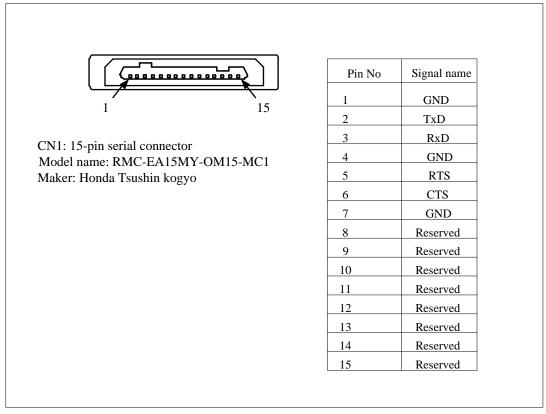

| 5.3 UART                                       | 36 |

| 5.3.1 Block Description                        | 36 |

| 5.3.2 Connector Pins                           | 37 |

| 5.3.3 Register Map                             | 38 |

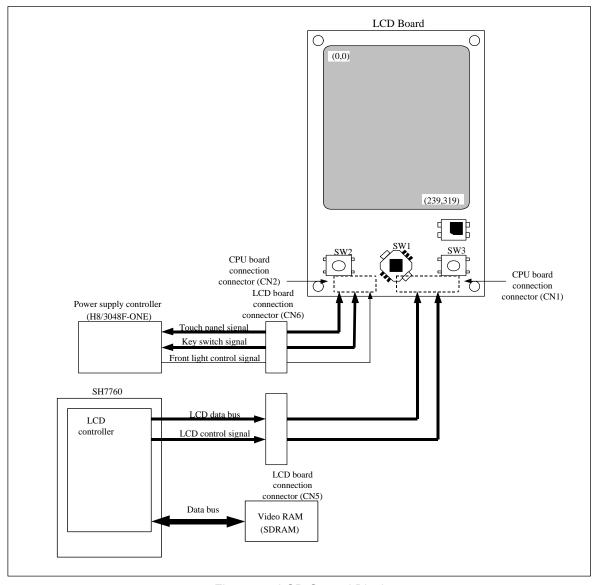

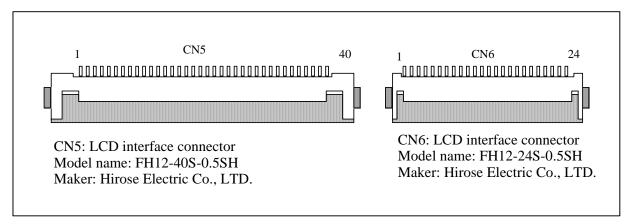

| 5.4 LCD                                        | 39 |

| 5.4.1 Block Description                        | 39 |

| 5.4.2 Connector Pins                           | 40 |

| 5.4.3 Register Map                             | 41 |

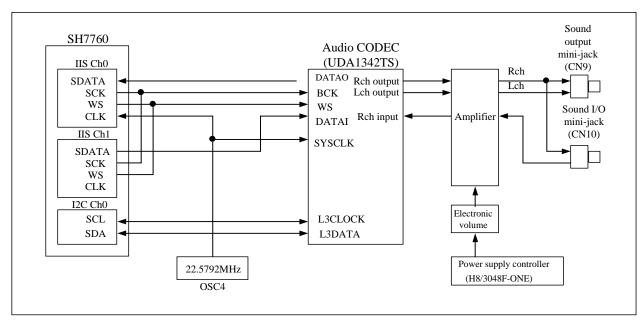

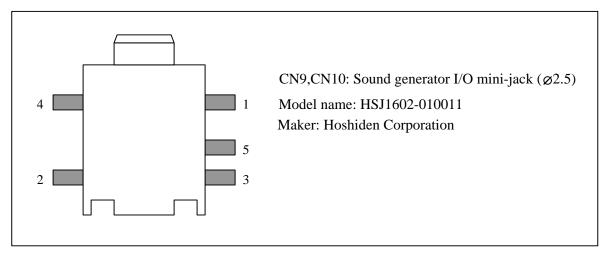

| 5.5 Sound Generator                            | 42 |

| 5.5.1 Block Description                        | 42 |

| 5.5.2 Connector Pins                           | 43 |

| 5.5.3 Register Map                             | 44 |

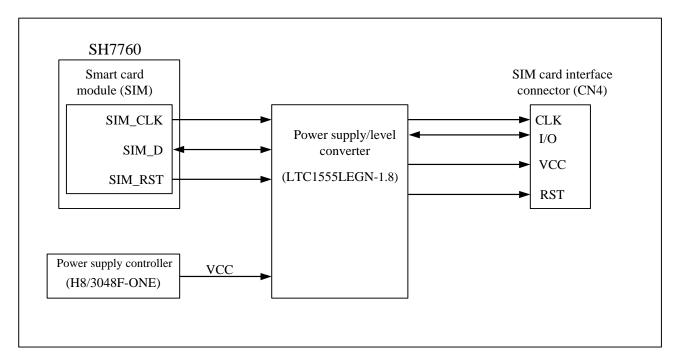

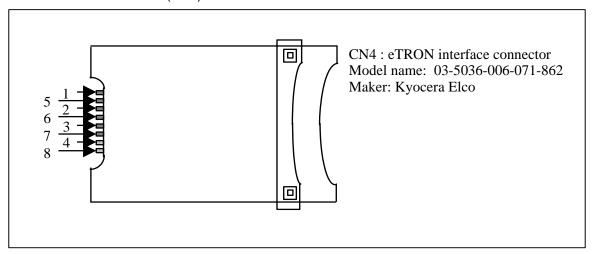

| 5.6 eTRON Interface                            | 45 |

| 5.6.1 Block Description                        | 45 |

| 5.6.2 Connector Pins                           | 46 |

| 5.6.3 Register Map                             | 47 |

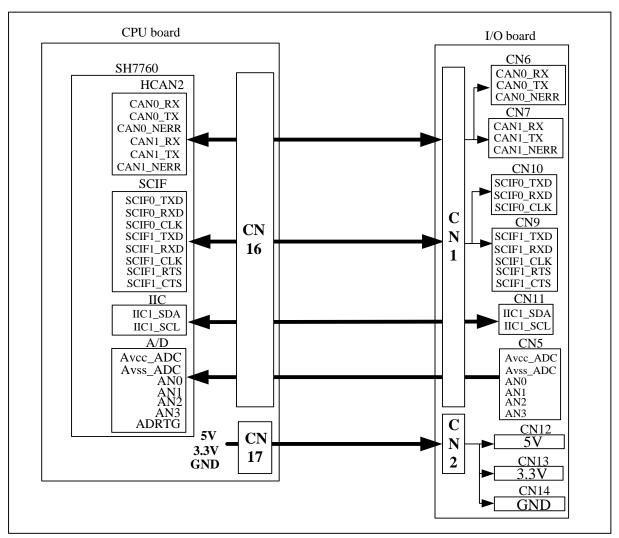

| 5.7 I/O Board                                  |    |

| 5.7.1 Block Description                        | 48 |

| 5.7.2 Connector (Through-Hole) Pin Assignments | 49 |

|                                                |    |

| 6. Power Supply Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 6.1. Power Supply Controller Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                   |

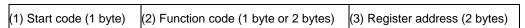

| 6.2 Serial Communications between SH7760 and the Power Supply Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52                   |

| 6.2.1 Serial Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52                   |

| 6.2.2 Power Supply Control Register Read Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52                   |

| 6.2.3 Read Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53                   |

| 6.2.4 Normal Response during a Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54                   |

| 6.2.5 Error Response during a read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54                   |

| 6.2.6 Power Supply Control Register Write Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                   |

| 6.2.7 Write Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

| 6.2.8 Normal Response during a Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56                   |

| 6.2.9 Error Response during a Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                   |

| 6.3 RTC (Real-time Clock) Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58                   |

| 6.3.1 RTC Control Register (RTCCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59                   |

| 6.3.2 RTC Status Register (RTCSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                   |

| 6.3.3 Second Counter (SECCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                   |

| 6.3.4 Minute Counter (MINCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                   |

| 6.3.5 Hour Counter (HRCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |

| 6.3.6 Day-of-the-Week Counter (WKCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62                   |

| 6.3.7 Day Counter (DAYCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62                   |

| 6.3.8 Month Counter (MONCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62                   |

| 6.3.9 Year Counter (YRCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63                   |

| 6.3.10 Alarm Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63                   |

| 6.3.11 Second Alarm Register (SECAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                   |

| 6.3.12 Minute Alarm Register (MINAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                   |

| 6.3.13 Hour Alarm Register (HRAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

| 6.3.14 Day-of-the-Week Alarm Register (WKAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64                   |

| 6.3.15 Day Alarm Register (DAYAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                   |

| , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| 6.3.16 Month Alarm Register (MONAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65                   |

| , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                   |

| 6.3.16 Month Alarm Register (MONAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65<br>65<br>66       |

| 6.3.16 Month Alarm Register (MONAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65<br>65<br>66       |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65<br>65<br>66<br>68 |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (YAPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (YAPDR) 6.4.10 XB Position Dot Register (XBPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (XAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (YBPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (YAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (YBPDR) 6.4.12 XC Position Dot Register (XCPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (YAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (YBPDR) 6.4.12 XC Position Dot Register (XCPDR) 6.4.13 YC Position Dot Register (YCPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (YPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (XBPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (YBPDR) 6.4.12 XC Position Dot Register (XCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position Dot Register (YCPDR) 6.4.14 XA Position Dot Register (YCPDR)                                                                                                                                                                                                                                                                                                                                                     |                      |

| 6.3.16 Month Alarm Register (MONAR). 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR). 6.4 Touch Panel Functions. 6.4.1 Touch Panel Control Register (TPLCR). 6.4.2 Touch Panel Status Register (TPLSR). 6.4.3 Touch panel Sampling Control Register (TPLSCR). 6.4.4 X Position A/D Register (XPAR). 6.4.5 Y Position A/D Register (YPAR). 6.4.6 X Position Dot Register (XPDR). 6.4.7 Y Position Dot Register (YPDR). 6.4.8 XA Position Dot Register (XAPDR). 6.4.9 YA Position Dot Register (XBPDR). 6.4.10 XB Position Dot Register (XBPDR). 6.4.11 YB Position Dot Register (YBPDR). 6.4.12 XC Position Dot Register (XCPDR). 6.4.13 YC Position Dot Register (YCPDR). 6.4.14 XA Position A/D Register (XAPAR). 6.4.15 YA Position A/D Register (YAPAR).                                                                                                                                                                                                                                                                                                                                   |                      |

| 6.3.16 Month Alarm Register (MONAR). 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions. 6.4.1 Touch Panel Control Register (TPLCR). 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR). 6.4.4 X Position A/D Register (XPAR). 6.4.5 Y Position A/D Register (YPAR). 6.4.6 X Position Dot Register (XPDR). 6.4.7 Y Position Dot Register (YPDR). 6.4.8 XA Position Dot Register (XAPDR). 6.4.9 YA Position Dot Register (XAPDR). 6.4.10 XB Position Dot Register (XBPDR). 6.4.11 YB Position Dot Register (YBPDR). 6.4.12 XC Position Dot Register (XCPDR). 6.4.13 YC Position Dot Register (YCPDR). 6.4.14 XA Position A/D Register (XAPAR). 6.4.15 YA Position A/D Register (YAPAR). 6.4.16 XB Position A/D Register (XBPAR).                                                                                                                                                                                                                                                                                            |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (XPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (YAPDR) 6.4.10 XB Position Dot Register (YBPDR) 6.4.11 YB Position Dot Register (YCPDR) 6.4.12 XC Position Dot Register (XCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position A/D Register (YAPAR) 6.4.15 YA Position A/D Register (YAPAR) 6.4.16 XB Position A/D Register (XBPAR) 6.4.17 YB Position A/D Register (YBPAR)                                                                                                                                                                                                                                                                     |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (XPDR) 6.4.8 XA Position Dot Register (YAPDR) 6.4.9 YA Position Dot Register (XBPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (YBPDR) 6.4.12 XC Position Dot Register (YCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position A/D Register (YAPAR) 6.4.15 YA Position A/D Register (YAPAR) 6.4.16 XB Position A/D Register (YBPAR) 6.4.17 YB Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YBPAR)                                                                                                                                                                                                                             |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (YPDR) 6.4.9 YA Position Dot Register (YAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (XPDR) 6.4.12 XC Position Dot Register (XCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position A/D Register (YCPDR) 6.4.15 YA Position A/D Register (YAPAR) 6.4.16 XB Position A/D Register (YAPAR) 6.4.17 YB Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR)                                                                                                                                                                                     |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (XPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (XAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (XCPDR) 6.4.12 XC Position Dot Register (XCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position A/D Register (YCPDR) 6.4.15 YA Position A/D Register (XAPAR) 6.4.16 XB Position A/D Register (XBPAR) 6.4.17 YB Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YBPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.20 DX Dot Register (DXDR)                                                                       |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch Panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (YPAR) 6.4.6 X Position Dot Register (YPAR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (YAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (YBPDR) 6.4.12 XC Position Dot Register (YCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position A/D Register (YCPDR) 6.4.15 YA Position A/D Register (XAPAR) 6.4.16 XB Position A/D Register (XBPAR) 6.4.17 YB Position A/D Register (XBPAR) 6.4.18 XC Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.20 DX Dot Register (DXDR) 6.4.21 DY Dot Register (DYDR) |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (XPAR) 6.4.6 X Position Dot Register (YPAR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (XAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (XBPDR) 6.4.12 XC Position Dot Register (YCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position A/D Register (YCPDR) 6.4.15 YA Position A/D Register (XAPAR) 6.4.16 XB Position A/D Register (YAPAR) 6.4.17 YB Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YBPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.21 DY Dot Register (DYDR) 6.4.21 DY Dot Register (DYDR) 6.4.22 X Position Dot Calculation A/D Value (XPARDOT)                           |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (XPAR) 6.4.6 X Position Dot Register (XPDR) 6.4.7 Y Position Dot Register (XPDR) 6.4.9 YA Position Dot Register (YPDR) 6.4.10 XB Position Dot Register (YAPDR) 6.4.11 YB Position Dot Register (YBPDR) 6.4.12 XC Position Dot Register (XCPDR) 6.4.13 YC Position Dot Register (XCPDR) 6.4.14 XA Position A/D Register (YAPAR) 6.4.15 YA Position A/D Register (XAPAR) 6.4.16 XB Position A/D Register (YBPAR) 6.4.17 YB Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YBPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.22 X Position Dot Calculation A/D Value (XPARDOT) 6.4.23 X Position Dot Calculation A/D Value (XPARDOT1)                                                                        |                      |

| 6.3.16 Month Alarm Register (MONAR) 6.3.17 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR) 6.4 Touch Panel Functions 6.4.1 Touch Panel Control Register (TPLCR) 6.4.2 Touch Panel Status Register (TPLSR) 6.4.3 Touch panel Sampling Control Register (TPLSCR) 6.4.4 X Position A/D Register (XPAR) 6.4.5 Y Position A/D Register (XPAR) 6.4.6 X Position Dot Register (YPAR) 6.4.7 Y Position Dot Register (YPDR) 6.4.8 XA Position Dot Register (XAPDR) 6.4.9 YA Position Dot Register (XAPDR) 6.4.10 XB Position Dot Register (XBPDR) 6.4.11 YB Position Dot Register (XBPDR) 6.4.12 XC Position Dot Register (YCPDR) 6.4.13 YC Position Dot Register (YCPDR) 6.4.14 XA Position A/D Register (YCPDR) 6.4.15 YA Position A/D Register (XAPAR) 6.4.16 XB Position A/D Register (YAPAR) 6.4.17 YB Position A/D Register (YBPAR) 6.4.18 XC Position A/D Register (YBPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.19 YC Position A/D Register (YCPAR) 6.4.21 DY Dot Register (DYDR) 6.4.21 DY Dot Register (DYDR) 6.4.22 X Position Dot Calculation A/D Value (XPARDOT)                           |                      |

| 6.4.26 X Position Dot Calculation A/D value 4 (XPARDOT4)                         | 78  |

|----------------------------------------------------------------------------------|-----|

| 6.4.27 Y Position Dot Calculation A/D Value (YPARDOT)                            | 79  |

| 6.4.28 Y Position Dot Calculation A/D Value 1 (YPARDOT1)                         | 79  |

| 6.4.29 Y Position Dot Calculation A/D Value 2 (YPARDOT2)                         | 79  |

| 6.4.30 Y Position Dot Calculation A/D Value 3 (YPARDOT3)                         | 80  |

| 6.4.31 Y Position Dot Calculation A/D Value 4 (YPARDOT4)                         | 80  |

| 6.4.32 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR)           |     |

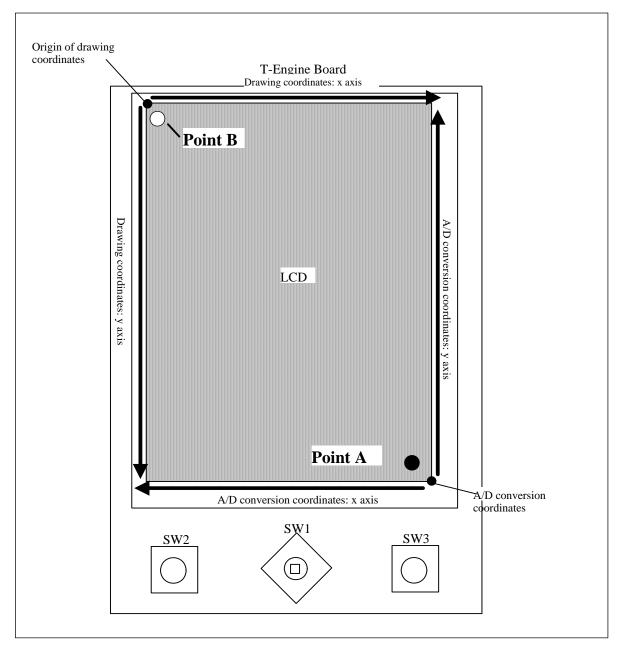

| 6.4.33 Touch Panel Calibration Method (2-point System)                           |     |

| 6.5 Key Switch Control                                                           |     |

| 6.5.1 CPU Board Switch Control                                                   |     |

| 6.5.2 LCD Board Switch Control (Application Switch)                              | 84  |

| 6.5.3 Key Switch Registers                                                       |     |

| 6.5.4 Key Control Register (KEYCR)                                               |     |

| 6.5.5 Key Auto Repeat Time Register (KATIMER)                                    |     |

| 6.5.6 Key Bit Pattern Register (KBIPR)                                           |     |

| 6.5.7 Key Input Status Register (KEYSR)                                          |     |

| 6.5.8 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR)            |     |

| 6.6 Power Supply Control                                                         |     |

| 6.6.1 System Power Control Register 1 (SPOWCR1)                                  |     |

| 6.6.2 System Power Control Register 2 (SPOWCR2)                                  |     |

| 6.6.3 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR)            |     |

| 6.7 LCD Front Light Control                                                      |     |

| 6.7.1 LCD Front Light Register (LCDR)                                            |     |

| 6.8 Reset Control                                                                |     |

| 6.8.1 RESTCR Register (RESTCR)                                                   |     |

| 6.9 Infrared Remote Control                                                      |     |

| 6.9.1 Infrared Remote Control Register (IRRCR)                                   |     |

| 6.9.2 Infrared Remote Control Status Register (IRRSR)                            |     |

| 6.9.3 Receive Data Count Register for Infrared Remote Control Signals (IRRRDNR)  |     |

| 6.9.4 Transmit Data Count Register for Infrared Remote Control Signals (IRRSDNR) |     |

| 6.9.5 Receive FIFO Data Register for Infrared Remote Control Signals (IRRRFDR)   |     |

| 6.9.6 Transmit FIFO Data Register for Infrared Remote Control Signals (IRRSFDR)  |     |

| 6.9.7 RTC/Touch Panel/Key Input/Power Supply Status Register (RTKISR)            |     |

| 6.9.8 Infrared Remote Control Data Structure                                     |     |

| 6.10 Serial EEPROM Control                                                       |     |

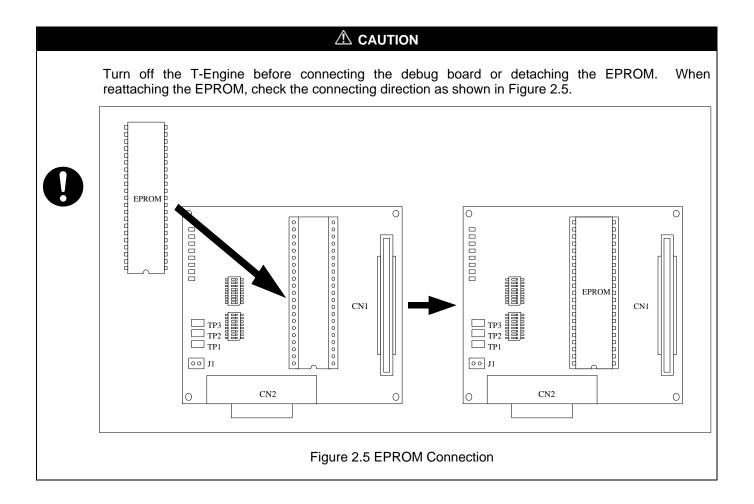

| 6.10.1 EEPROM Control Register (EEPCR)                                           | 99  |