# R0P751RLC0011RL

Outline

SH7751R Evaluation Platform

| Keep safety   | first in | vour | circuit design | !snr     |

|---------------|----------|------|----------------|----------|

| . toop calety |          | ,    | on our acong   | <b>7</b> |

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# IMPORTANT INFORMATION

# **READ FIRST**

- READ this user's manual before using this product.

- KEEP the user's manual handy for future reference.

Do not attempt to use the product until you fully understand its mechanism.

#### This Product:

In this manual, this product points out the following product which Renesas Solutions Corporation manufactured. A user's user system and host machine are not included.

### Purpose of the Product:

This product is a device to support the development of a system that uses the SuperH Risc engine Family SH7751R of Renesas 32-bit RISC MCUs. It provides support for system development in both software and hardware. Be sure to use this product correctly according to said purpose of use. Please avoid using this product for other than its intended purpose of use.

#### For those who use this product:

This product can only be used by those who have carefully read the user's manual and know how to use it. Use of this product requires the basic knowledge of electric circuits, logical circuits, and MCUs.

#### Precautions to be Taken when Using This Product:

- (1) This product is a development supporting unit for use in your program development and evaluation stages. In mass-producing your program you have finished developing, be sure to make a judgment on your own risk that it can be put to practical use by performing integration test, evaluation, or some experiment else.

- (2) In no event shall Renesas Solutions Corporation be liable for any consequence arising from the use of this product.

- (3) Renesas Solutions Corporation strives to renovate or provide a workaround for product malfunction at some charge or without charge. However, this does not necessarily mean that Renesas Solutions Corporation guarantees the renovation or the provision under any circumstances.

- (4) This product has been developed by assuming its use for program development and evaluation in laboratories. Therefore, it does not fall under the application of Electrical Appliance and Material Safety Law and protection against electromagnetic interference when used in Japan.

- (5) Renesas cannot anticipate every possible circumstance that might involve a potential hazard. The warnings in this user's manual and on the product are therefore not all inclusive. Therefore, you must use the product safely at your own risk.

- (6) This emulator does not conform to safety standards such as UL or IEC. Be careful when you take this emulator overseas.

- (7) This product is a product used for development of a program, and an evaluation stage. It cannot include in a user's product and cannot mass-produce.

- (8) Even if it is the case where fault is in the device carried in this product, it does not exchange for the fault repair article of a device.

- (9) Operation of all CF cards cannot be guaranteed.

- (10) Connection with the apparatus of all LAN interfaces cannot be guaranteed.

- (11) When you do not use it for a long time, please pull out and keep a power supply plug from a plug socket etc. for safety.

- (12) This product is a lead free mounting product.

- (13) Generally each brand name carried in these data is each maker's trademark or registered trademark.

- (14) Near DC jack of this product becomes high temperature. Be careful of a burn.

#### **Limited Applications:**

This emulator product is not authorized for use in transportation, vehicular, medical (where human life is potentially at stake), aerospace, nuclear, or undersea repeater applications. Buyers of this emulator product must notify Renesas Technology Corporation, Renesas Solutions Corporation or an authorized Renesas Technology product distributor before planning to use the product in such applications.

#### Improvement Policy:

Renesas Technology Corp. (including its subsidiaries, hereafter collectively referred to as Renesas) pursues a policy of continuing improvement in design, performance, and safety of the product. Renesas reserves the right to change, wholly or partially, the specifications, design, user's manual, and other documentation at any time without notice.

#### All Rights Reserved:

- 1. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Renesas' semiconductor products. Renesas assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 2. No license is granted by implication or otherwise under any patents or other rights of any third party or Renesas.

- 3. This user's manual and emulator product are copyrighted and all rights are reserved by Renesas. No part of this user's manual, all or part, may be reproduced or duplicated in any form, in hard-copy or machine-readable form, by any means available without Renesas' prior written consent.

#### State Law:

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you.

This warranty gives you specific legal rights, and you may have other rights which may vary from state to state.

#### The Warranty is Void in the Following Cases:

Renesas shall have no liability or legal responsibility for any problems caused by misuse, abuse, misapplication, neglect, improper handling, installation, repair or modifications of the product without Renesas' prior written consent or any problems caused by the user system.

#### Figures:

Some figures in this user's manual may show items different from your actual system.

\* Compact Flash<sup>TM</sup> is the registered trademark of SanDisk Corporation.

# **Precautions for Safety**

# **Definitions of Signal Words**

In both the General Information Manual and on the product itself, several icons are used to insure proper handling of this product and also to prevent injuries to you or other persons, or damage to your properties.

This chapter describes the precautions which should be taken in order to use this product safely and properly.

Be sure to read this chapter before using this product.

This symbol represents a warning about safety. It is used to arouse caution about a potential danger that will possibly inflict an injury on persons. To avoid a possible injury or death, please be sure to observe the safety message that follows this symbol.

**DANGER** indicates an imminently dangerous situation that will cause death or heavy wound unless it is avoided. However, there are no instances of such danger for the product presented in this manual.

**WARNING** indicates a potentially dangerous situation that will cause death or heavy wound unless it is avoided.

**CAUTION** indicates a potentially dangerous situation that will cause a slight injury or a medium-degree injury unless it is avoided.

**CAUTION** with no safety warning symbols attached indicates a potentially dangerous situation that will cause property damage unless it is avoided.

**NOTE** emphasizes essential information.

In addition to the five above, the following are also used as appropriate.

△ means WARNING or CAUTION.

Example:

# **CAUTION AGAINST AN ELECTRIC SHOCK**

Example:

# DISASSEMBLY PROHIBITED

means A FORCIBLE ACTION.

Example:

# UNPLUG THE POWER CABLE FROM THE RECEPTACLE.

# Warnings for AC Power Supply:

- If If the attached AC power cable does not fit the receptacle, do not alter the AC power cable and do not plug it forcibly. Failure to comply may cause electric shock and/or fire.

- Use an AC power cable which complies with the safety standard of the country.

- Do not touch the plug of the AC power cable when your hands are wet. This may cause electric shock.

- This product is connected signal ground with frame ground. If your developing product is transformless (not having isolation transformer of AC power), this may cause electric shock. Also, this may give an unrepairable damage to this product and your developing one.

While developing, connect AC power of the product to commercial power through isolation transformer in order to avoid these dangers.

- If other equipment is connected to the same branch circuit, care should be taken not to overload the circuit.

- If you smell a strange odor, hear an unusual sound, or see smoke coming from this product, then

disconnect power immediately by unplugging the AC power cable from the outlet.

Do not use this as it is because of the danger of electric shock and/or fire. In this case, contact your

local distributor.

- Before setting up this product and connecting it to other devices, turn off power or remove a power cable to prevent injury or product damage.

# Warnings to Be Taken for This Product:

- Do not disassemble or modify this product. Personal injury due to electric shock may occur if this product is disassembled and modified.

- Make sure nothing falls into the cooling fan on the top panel, especially liquids, metal objects, or anything combustible.

# Warning for Installation:

- Do not set this product in water or areas of high humidity. Make sure that the product does not get wet. Spilling water or some other liquid into the product may cause unrepairable damage.

- Please use this product indoors.

# Warning for Use Environment:

• This equipment is to be used in an environment with a maximum ambient temperature of 35°C. Care should be taken that this temperature is not exceeded.

# Note on Connecting the Power Supply:

- Do not use any power cable other than the one that is included with the product.

- At the time of connection with installation of this product or other equipments, please extract an AC/DC adaptor from a plug socket and prevent an injury and an accident.

- Pay attention to the polarities of the power supply. If its positive and negative poles are connected in reverse, the internal circuit may be broken.

#### Power supply injection:

• Once the power is turned off, wait for about 10 seconds before turning it back on again.

#### Cautions to Be Taken for Handling This Product:

- Handle the product with caution, taking care not to apply strong mechanical shock to the product by dropping or letting it fall down.

- Do not touch the communication interface connector pins or other connector pins directly with your hand. Static electricity from your body may break down the internal circuit of the product.

- Do not pull the product by the cable connecting to a board in it. Do not hold down a board while you pull the other end of it. The cable may break.

| Contents |                                                           |    |

|----------|-----------------------------------------------------------|----|

| 1.       | Outline                                                   | 10 |

| 1.1.     | Package Components                                        | 10 |

| 1.2.     | System Configuration                                      | 11 |

| 1.2.1.   | System Configuration                                      | 11 |

| 1.2.2.   | Names and Functions of each part of the System            | 12 |

| 1.3.     | Setup Method (Up to Boot loader starting)                 | 13 |

| 1.4.     | Specification List                                        | 14 |

| 1.5.     | Address Map                                               | 16 |

| 2.       | Functional Specification                                  | 17 |

| 2.1.     | Power Supply Specification                                | 17 |

| 2.1.1.   | DC Jack Input Power Supply                                | 18 |

| 2.2.     | Switches Specification                                    | 18 |

| 2.2.1.   | DIP Switch for CPU Mode Setup                             | 18 |

| 2.2.2.   | DIP Switch for Debugging                                  | 19 |

| 2.2.3.   | Power On Switch                                           | 19 |

| 2.2.4.   | Switch for System Reset                                   | 19 |

| 2.2.5.   | Switch for Manual Reset                                   | 20 |

| 2.2.6.   | DIP Switch for Maintenance                                | 20 |

| 2.3.     | LED Specification                                         | 21 |

| 2.3.1.   | LED for the SH7751R status                                | 21 |

| 2.3.2.   | LED for the Ethernet Hub                                  | 21 |

| 2.3.3.   | LED for the CF Card                                       | 21 |

| 2.3.4.   | LED for the USB Hub                                       | 21 |

| 2.3.5.   | LED for Power Supply                                      | 21 |

| 2.3.6.   | LED for Debugging                                         | 21 |

| 2.4.     | JTAG Emurator Interface                                   | 22 |

| 2.5.     | Memories                                                  | 22 |

| 2.5.1.   | An Access Timing Setup to Each Device Connected to SH Bus | 22 |

| 2.6.     | PCI Devices                                               | 23 |

| 2.6.1.   | PCI Card Slot                                             | 23 |

| 2.6.2.   | CardBus Card Connector                                    | 23 |

| 2.6.3.   | LAN Connector                                             | 23 |

| 2.6.3.1. | MAC Address Assignment                                    | 23 |

| 2.7.     | 2D Graphic Controller Interface                           | 24 |

| 2.7.1.   | CRT Connector                                             | 24 |

| 2.7.2.   | LCD Connector                                             | 25 |

| 2.7.3.   | LCD Back Light Connector                                  | 26 |

| 2.7.4.   | USB Connector                                             | 26 |

| 2.7.5.   | SM501 Extention Connector                                 | 27 |

| 2.8.     | Touch Panel Connector                                     | 28 |

| 2.9.     | SH Bus Extention Connector                                | 29 |

| 2.10.    | Serial Connector                                          | 36 |

| 2.11.    | CF Card Connector                                         | 36 |

| 2.12.    | FROM Board Connector                                      | 37 |

| 2.13.    | Real Time Clock                                           | 39 |

| 2.14.    | Serial Interface (Internal FPGA)                          | 39 |

| 2.15.    | Reset Signal                                              | 40 |

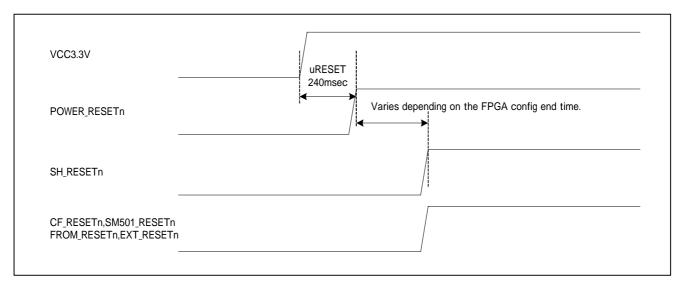

| 2.15.1.  | Power On Reset                                            | 40 |

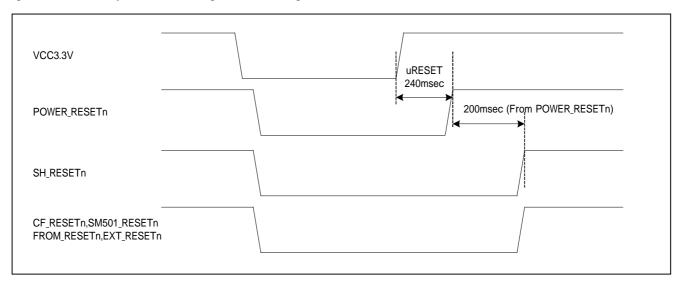

| 2.15.2.  | System Reset                                              | 41 |

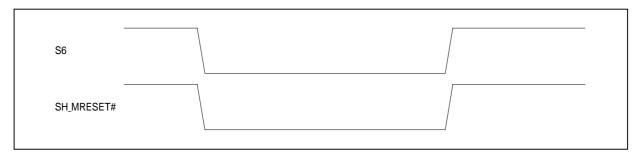

| 2.15.3.  | Manual Reset                                              | 41 |

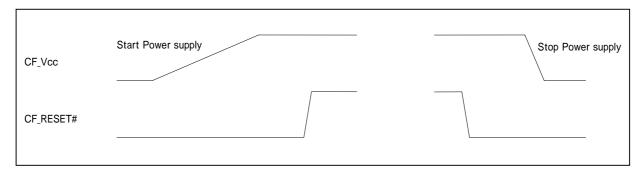

| 2.15.4.  | CF Card Reset                                             | 41 |

| 3.       | FPGA Logic Function Specification                         | 42 |

| 3.1.     | Pin Function                                              | 42 |

| 3.2.     | Register Map                                              | 47 |

| 4.       | Extension Board Specification                             | 48 |

| 4.1.     | About the extension boaed size                            |    |

| 4.2.     | The allowable current of add-in board and PCI card        | 49 |

| R0P751RLC0011RL | . User's manual |

|-----------------|-----------------|

|-----------------|-----------------|

| $\sim$ |     |     |

|--------|-----|-----|

| Co     | nta | ntc |

| -      | шс  | HIG |

| 4.2.1. | The allowable current of add-in board | 49 |

|--------|---------------------------------------|----|

| 4.2.2. | The allowable current of PCI board    |    |

| 5.     | Boot Loader Specification             |    |

| 5.1.   | Boot Loader Functional List           |    |

| 6      | Linux Kernel Download                 |    |

# 1. Outline

# 1.1. Package Components

This product is constituted by the following board and parts. When opened, please check whether it has gathered altogether.

Table 1.1.1 The contents list of packing

| Item                                     | Description                        | Quantity |

|------------------------------------------|------------------------------------|----------|

| R0P751RLC0011RL                          | SH7751R Platform                   | 1        |

| FROM Board (Bus width is 32bit 64M Byte) | Within boot loader                 | 1        |

| AC Adapter                               | DC12.0V 5.0A                       | 1        |

| CD-ROM                                   | User's manual, Sample program etc. | 1        |

<sup>\*</sup> If there is any question or doubt about the packaged product, contact your local distributor.

# 1.2. System Configuration

# 1.2.1. System Configuration

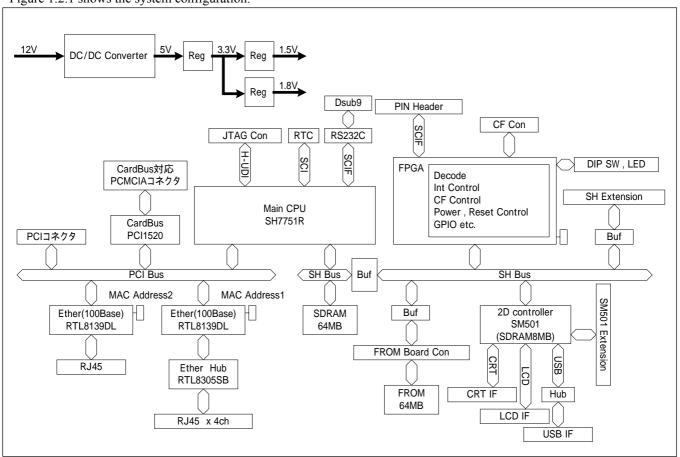

Figure 1.2.1 shows the system configuration.

Figure 1.2.1 R0P751RLC0011RL system configuration

# 1.2.2. Names and Functions of each part of the System

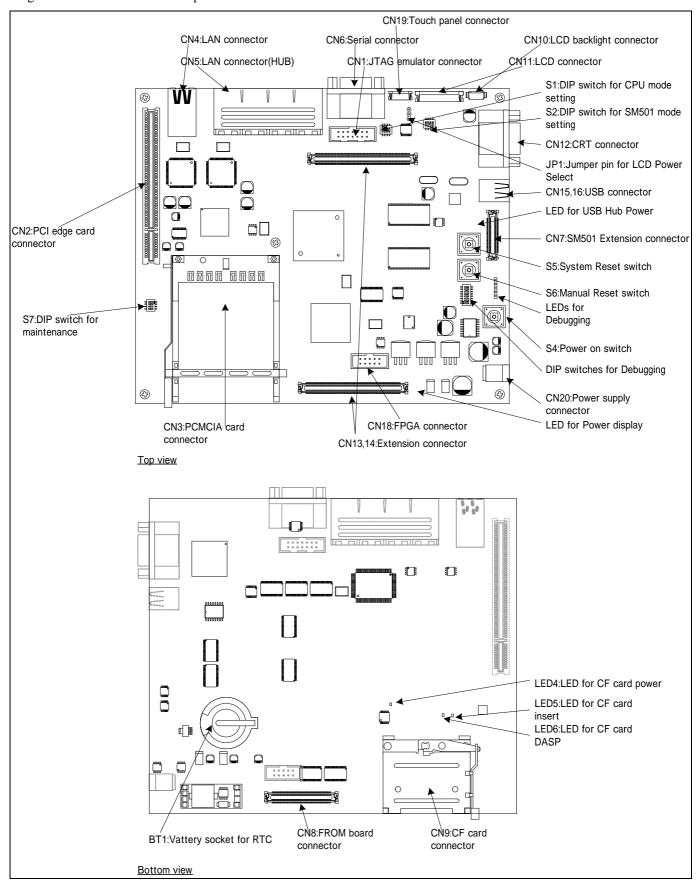

Figure 1.2.2 shows the names of parts reference.

Figure 1.2.2 Name of R0P751RLC0011RL's parts reference

# 1.3. Setup Method (Up to Boot loader starting)

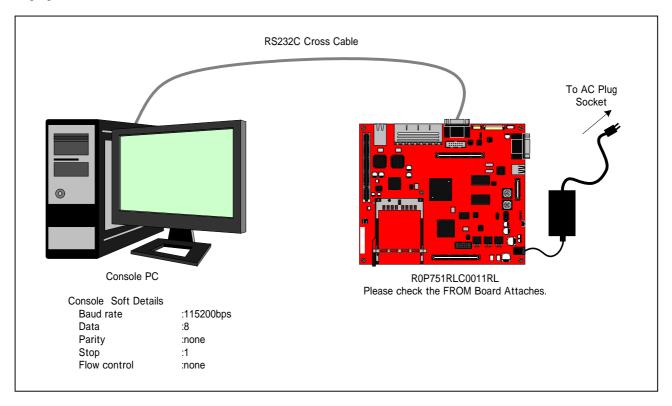

Figure 1.3.1 shows the setting up this system. Please prepare the follows:

Console PC

RS232C cross cable

Please prepare CF card, a CRT monitor, network environment, etc. if needed.

Figure 1.3.1 Set Up this system

(1) Please attach the FROM board in CN8 mounted in the solder side of R0P751RLC0011RL. (Be careful of poor contact.)

Where the power supply of this product is intercepted, please be sure to make connection of a FROM board. Moreover, be careful of poor contact of a FROM board. The mistaken usage leads to destruction of this product.

- (2) Connect the terminal for consoles with this board with a RS232C cross cable.

- (3) Start terminal software on the terminal for consoles.

(baudrate:115200bps, data:8bit, parity:none, stop bit:1bit, flow control:none)

- (4) Insert an attached AC/DC adaptor in CN20, and connect with a plug socket.

- (5) If S4 of R0P751RLC0011RL is pushed, a power supply injection will be carried out. (Red button)

If S4 is pushed again, power supply interception is possible. However, while using CF card, please carry out power supply interception processing in carried FPGA. When S4 is pushed during CF card operation and power supply interception is performed, there is possibility of destruction of CF card. Please refer to the clause of FPGA functional explanation about the specification of FPGA.

# 1.4. Specification List

Table 1.4.1 shows a list of specifications.

Table 1.4.1 R0P751RLC0011RL Specifications

| T                            | Table 1.4.1 R0P751RLC0011RL Specifications           |  |  |

|------------------------------|------------------------------------------------------|--|--|

| Item                         | Description                                          |  |  |

| CPU                          | HD6417751RBP240V (Renesas Technorogy)                |  |  |

|                              | • Input Clock: 20MHz                                 |  |  |

|                              | • CPU Clock(I): 240MHz (Mode 5)                      |  |  |

|                              | • Bus Clock(B): 120MHz (Mode 5)                      |  |  |

|                              | • Peripheral Clock(P): 60MHz (Mode 5)                |  |  |

|                              | • PCI Bus: 33MHz (4ch)                               |  |  |

|                              | • Package: 256pins BGA (1.27mm pitch)                |  |  |

| Memory                       | FROM board:S29PL127J60TFI130 (Spansion)              |  |  |

|                              | • FROM:64M Byte • 32bit Bus Access                   |  |  |

|                              | EDS2516ADTA-75E (Elpida memory)                      |  |  |

|                              | • SDRAM:64MB                                         |  |  |

| TDC A                        | • 32bit Bus Access                                   |  |  |

| FPGA                         | EP1C4F400C8N (ALTERA)                                |  |  |

|                              | • Address Decode ,Interrupt control ,CF control etc. |  |  |

|                              | Configuration ROM: EPCS4SI8N                         |  |  |

| 2D Graphic Controller        | SM501GX08LF00-AB (Silicon Motion)                    |  |  |

| LAN Controller               | RTL8139DL-LF (Realtek)                               |  |  |

|                              | LAN Connector: LU1S041C-43-LF(BOTHHAND)              |  |  |

| LAN Hub Controller           | RTL8305SB-VD-LF (Realtek)                            |  |  |

|                              | LAN Connector:0810-1X4T-36-F(BelFuse)                |  |  |

| CardBus Controller           | PCI1520ZHK (Texas Instruments)                       |  |  |

| Real Time Clock              | RTC-9701JE(Epson Toyocom)                            |  |  |

|                              | • Uses SH7751R'SCI                                   |  |  |

| LED                          | • for Debugging (8):Control FPGA register            |  |  |

|                              | • for Status (6)                                     |  |  |

| Switch                       | • for Power ON (x 1)                                 |  |  |

|                              | • for RESET (x 2)                                    |  |  |

|                              | • for Debugging (8bit x 1)                           |  |  |

|                              | • for Mode setting (4bit x 2)                        |  |  |

| Compact Flash Card Connector | Header: ICM-MA2H-SS52-N11B(LF)(SN) (JST)             |  |  |

|                              | Ejector: ICME-CB68L5-302N (JST)                      |  |  |

| PCMCIA Card Connector        | Header: ICM-CB68H-S112-502N(LF)(SN) (JST)            |  |  |

|                              | Ejector:ICM-MAE-R32 (JST)                            |  |  |

| Serial Connector             | RS232C Connector:JEY- 9P-1A2B (JST)                  |  |  |

|                              | SH7751R's SCIF                                       |  |  |

| Connectors                   | SH Bus Extension connector: 52837-1679 (Molex)       |  |  |

|                              | FROM board connector:52837-1079 (Molex)              |  |  |

|                              | SM501 Extension connector:52837-0679 (Molex)         |  |  |

|                              | USB connector:XM7A-0442-A (Omron)                    |  |  |

|                              | CRT connector:XM4L-1542-132 (Omron)                  |  |  |

|                              | LCD connector:40FLH-SM1-TB(LF)(SN) (JST)             |  |  |

|                              | LCD backlight connector:53261-0590 (Molex)           |  |  |

|                              | Touchpanel interface connector:                      |  |  |

|                              | 14FLH-SM1-TB (LF)(SN) (JST)                          |  |  |

|                              | SH7751R JTAG Emulator connector (14pins)             |  |  |

|                              | XG4C-1031 (Omron)                                    |  |  |

|                              | EPCS4SI8N connector (10pins)                         |  |  |

|                              | XG4C-1431 (Omron)                                    |  |  |

| Item                  | Description             |  |

|-----------------------|-------------------------|--|

| Power IN              | 2.1mmSocket Center Plus |  |

|                       | • From AC/DC Adapter    |  |

| Size                  | • Size: 170mm × 200mm   |  |

| Operating temperature | 5 to 35°C (no dew)      |  |

| Storage temperature   | -10 to 60°C (no dew)    |  |

# 1.5. Address Map

Figure 1.5.1 shows Address Map. Please refer to the clause of FPGA functional explanation about the specification of FPGA.

| H 0000_0000                              |        |                |                                   |

|------------------------------------------|--------|----------------|-----------------------------------|

|                                          | Area O | <u>32bit</u>   | FROM Area (64MB)                  |

| <u>H 03FF_FFFF</u>                       |        |                |                                   |

| H 0400 0000                              |        |                | FPGA Area (80B)                   |

| <u>H 0400_004F</u><br><u>H 0400_0050</u> | Area 1 | <u>16bit</u>   |                                   |

| H 07FF_FFFF                              |        |                | <u>Disable Area (FPGA Shadow)</u> |

| H 0800 0000                              |        |                |                                   |

|                                          | Area 2 | 8/16/32<br>bit | Extension Area (64MB)             |

| H OBFF_FFFF                              |        |                |                                   |

| H 0C00_0000                              |        |                |                                   |

|                                          | Area 3 | <u>32bit</u>   | SDRAM Area (64MB)                 |

| H OFFF_FFFF                              |        |                |                                   |

| H 1000 0000                              |        |                |                                   |

|                                          | Area 4 | <u>32bit</u>   | SM501GX08LF00 Area                |

| H 13FF_FFFF                              |        |                |                                   |

| H 1400_0000                              |        |                |                                   |

|                                          | Area 5 | <u>16bit</u>   | Compact FLASH Area (64MB)         |

| H 17FF_FFFF                              |        |                |                                   |

| H 1800 0000                              |        | - / - /        |                                   |

|                                          | Area 6 | 8/16/32<br>bit | Extension Area (64MB)             |

| H 1BFF_FFFF                              |        | <del>~</del>   |                                   |

Figure 1.5.1 SH7751R Address Map

# 2. Functional Specification

# 2.1. Power Supply Specification

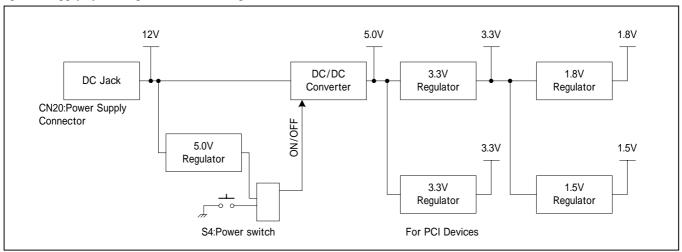

This board operates by supply of 12V from an attached AC/DC adaptor.

A power supply system figure is shown in Fig. 2.1.1

Figure 2.1.1 power-supply system figure

Each voltage is used by the following blocks. The main power supply use blocks are shown in Table 2.1.1.

| Voltage | Use place                   | Note              |

|---------|-----------------------------|-------------------|

|         | PCI connector               |                   |

| 1017    | PCMCIA connector            |                   |

| 12V     | Inverter for LCD            |                   |

|         | The connector for extension |                   |

|         | Standby power               |                   |

|         | PCI connector               |                   |

| 5.017   | PCMCIA connector            |                   |

| 5.0V    | LAN controller              | RTL8139DL         |

|         | USB Hub controller          |                   |

|         | 拡張connector                 |                   |

|         | PCI connector               |                   |

|         | PCMCIA connector            |                   |

|         | SH7751R                     | HD6417751RBP240   |

|         | FROM                        | S29PL127J60TFI130 |

| 3.3V    | SDRAM                       | EDS2516ADTA       |

|         | FPGA                        | EP1C4F400C8N      |

| 3.3 V   | SM501                       | SM501GX08LF00     |

|         | CF card connector           |                   |

|         | CardBus card controller     | PCI1520ZHK        |

|         | LAN controller              | RTL8139DL         |

|         | LAN Hub controller          | RTL8305SB         |

|         | The connector for extension |                   |

| 1.8V    | SM501 core power            | SM501GX08LF00     |

| 1.5V    | SH7751R core power          | HD6417751RBP240   |

| 1.3 V   | FPGA core power             | EP1C4F400C8N      |

Table 2.1.1 The main power supply use blocks

#### 2.1.1. DC Jack Input Power Supply

The input power supply specification from DC jack of this board is shown.

Please choose the power supply which suits the specification shown in Table 2.1.2 in the case of use of except for an attached AC/DC adaptor.

Table 2.1.2 DC jack input specification.

|                | 1 1                              |

|----------------|----------------------------------|

| Item           | Specification                    |

| Plug           | 2.5mm                            |

| Plug Polarity  | Outside: Minus, inner side:Plus. |

| Input voltage  | 12.0V                            |

| Supply current | More than 5.0A                   |

Keep in mind that near DC jack becomes high temperature very much at the time of this product operation.

When an AC/DC adaptor with the reverse polarity of a plug is used, it leads to destruction of this product. Moreover, keep in mind that there is possibility of emitting smoke and ignition.

# 2.2. Switches Specification

Three push switches and three DIP switches are mounted in this board.

#### 2.2.1. DIP Switch for CPU Mode Setup

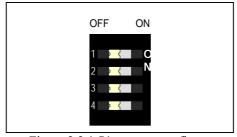

S1 is the DIP switch for a mode setup of operation of SH7751R. The clock mode and the endian of SH7751R are specified. The S1 specification is shown in Table 2.2.1 and the S1appearance figure is shown in Fig. 2.2.1. It is in a shading state at the time of shipment, it was made into the clock mode 5 (internal:240MHz, external bus:120MHz, circumference module:60MHz), and is set as a little endian.

Figure 2.2.1 S1 appearance figure

Table 2.2.1 S1 specification.

| Switch | Connection terminal | ON | OFF | Function                 |

|--------|---------------------|----|-----|--------------------------|

| S1-1   | SH7751R_MD0         | Н  | L   |                          |

| S1-2   | SH7751R_MD1         | Н  | L   | A setup of an clock mode |

| S1-3   | SH7751R_MD2         | Н  | L   |                          |

|        |                     |    |     | A setup of an endian     |

| S1-4   | SH7751R_MD5         | H  | L   | L:Big endian             |

|        |                     |    |     | H:Little endian          |

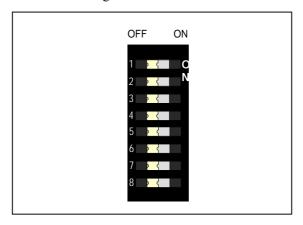

# 2.2.2. DIP Switch for Debugging

S3 is a DIP switch for debugging. It can connect with FPGA and can refer to by the dedicated register. It can be used of a user. Please refer to the clause of FPGA functional explanation about the specification of FPGA. The S3 appearance figure is shown in Table 2.2.2 and the S3 specification is shown in Fig. 2.2.2.

Figure 2.2.2 S3 appearance figure.

|        |                     | 1 able 2.2.2 | 33 specification | 1.                            |

|--------|---------------------|--------------|------------------|-------------------------------|

| Switch | Connection terminal | ON           | OFF              | Function                      |

| S3-1   | FPGA                | Н            | L                |                               |

| S3-2   | FPGA                | Н            | L                |                               |

| S3-3   | FPGA                | Н            | L                |                               |

| S3-4   | FPGA                | Н            | L                | Defence is respille at EDCA   |

| S3-5   | FPGA                | Н            | L                | Reference is possible at FPGA |

| S3-6   | FPGA                | Н            | L                |                               |

| S3-7   | FPGA                | Н            | L                |                               |

| S3-8   | FPGA                | Н            | L                |                               |

Table 2.2.2 S3 specification

#### 2.2.3. Power On Switch

S4 is a power supply switch. Key-top is "red". After inserting an attached AC/DC adaptor in CN20, a power supply is supplied to this board under switch-pushing. A power supply is again intercepted under S4 swich-pushing at the time of this board operation.

The method of power supply interception is controllable by "S4 switch-pushing" or the control from FPGA. When you perform sudden power supply interception by S4, since the data of CF card etc. may be destroyed, please perform power supply interception by the control from FPGA.

Please refer to the clause of FPGA functional explanation about the specification of FPGA.

## 2.2.4. Switch for System Reset

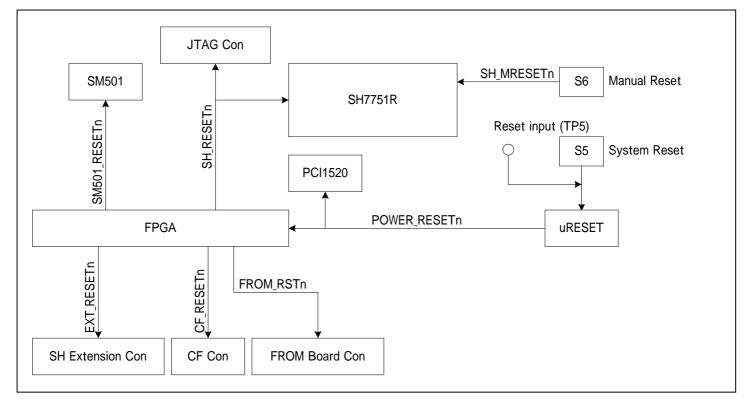

S5 is a system-reset switch. A key-top is "white". A reset pulse is generated to this timing in each device under S5 swich-pushing. The explanation about a reset signal is indicated to "2.15 Reset signal".

#### 2.2.5. Switch for Manual Reset

S6 is a manual reset switch. A key-top is "blue". Manual reset is inputted into SH7751R under S6 swich-pushing. There is no input to other devices. The explanation about a reset signal is indicated to "2.15 Reset signal".

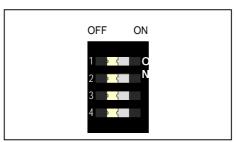

#### 2.2.6. DIP Switch for Maintenance

S7 is a DIP switch for a maintenance setup. Moreover, the bus width of FROM at the time of starting is also set up by ON/OFF of bit4.

It can connect with FPGA and can refer to by the dedicated register. Please refer to the clause of FPGA functional explanation about the specification of FPGA. An attached FROM board is connected, and if bit1 is set as "ON" and started, it will start in maintenance mode.

By starting in maintenance mode, use of boot loader update and test mode is attained.

Please refer to the clause of boot loader functional explanation about the specification in boot loader update and test mode.

The S7 specification is shown in Table 2.2.6 and the S7 appearance figure is shown in Fig. 2.2.6. It is in a shading state at the time of shipment, and it is set as normal mode starting and a bus width of 32 bits.

Figure 2.2.6 S7 appearance figure

Table 2.2.6 S7 specification

| Switch | Connection terminal | ON | OFF | Function                                          |

|--------|---------------------|----|-----|---------------------------------------------------|

| S7-1   | FPGA                | Н  | L   | Boot loader mode                                  |

| S7-2   | FPGA                | Н  | L   | Reservation                                       |

| S7-3   | FPGA                | Н  | L   | Reservation                                       |

| S7-4   | SH7751R_MD3         | Н  | L   | Area 0 bus width is specified 0: 16bit / 1: 32bit |

# 2.3. LED Specification

# 2.3.1. LED for the SH7751R status

LED1 is LED for a status display of SH7751R. It has connected with STATUS1, and STATUS0 of SH7751R ports. Functional assignment of LED is shown in Table 2.3.1.

Table 2.3.1 LED functional assignment.

| LED  | Function | Status          |

|------|----------|-----------------|

|      | Reset    | Lighting off    |

| LED1 | Sleep    | Green lighting  |

| LED1 | Standby  | Red lighting    |

|      | Nomal    | Orange lighting |

#### 2.3.2. LED for the Ethernet Hub

LED2 and LED3 are connected to LED\_ACT4, and LED\_SPD4 of RTL8305SB. A function changes with setup of RTL8305SB. Please refer to the data of RTL8305SB about the details of the usage.

#### 2.3.3. LED for the CF Card

LED4, LED5, and LED 6 are LED for CF cards. It is automatically controlled by CF card insertion. LED functional assignment is shown in Table 2.3.2.

Table 2.3.2 LED functional assignment

| LED  | Function                                   | Status   |

|------|--------------------------------------------|----------|

| LED4 | At the time of the power supply to CF card | Lighting |

| LED5 | At the time of CF card insertion           | Lighting |

| LED6 | At the time of CF_DASP mode                | Lighting |

#### 2.3.4. LED for the USB Hub

LED7 and LED8 are connected to a USB Hub controller. If a power supply is supplied to each USB connector, it will light up.LED functional assignment is shown in Table 2.3.3.

Table 2.3.3 LED functional assignment

| LED  | Function                                  | Status   |

|------|-------------------------------------------|----------|

| LED7 | It is power supply supply to USB Hub No.1 | Lighting |

| LED8 | It is power supply supply to USB Hub No.2 | Lighting |

# 2.3.5. LED for Power Supply

LED17 is LED for a power supply display. If a power supply is supplied to this board, it will light up.

#### 2.3.6. LED for Debugging

LED9 to LED16 are LED for debugging. It is controllable by FPGA. Please refer to the clause of FPGA functional explanation about the specification of FPGA.

## 2.4. JTAG Emurator Interface

CN1 is a connector for JTAG emulator. The emulator which used the H-UDI interface of SH7751R is connected. Please use it, connecting the emulator corresponding to H-UDI made from Renesas Technology Corp.

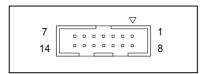

The general-view figure of a JTAG emulator connector is shown in Fig. 2.4.1, and signal arrangement is shown in Table 2.4.1.

Figure 2.4.1 Appearance figure of JTAG emulator connector

Table 2.4.1 Signal arrangement of JTAG emulator connector

| Pin number | Signal name |

|------------|-------------|

| 1          | TCK         |

| 2          | TRST#       |

| 3          | TDO         |

| 4          | ASEBRK#     |

| 5          | TMS         |

| 6          | TDI         |

| 7          | RESET#      |

| 8          | GND         |

| 9          | GND         |

| 10         | GND         |

| 11         | NC          |

| 12         | GND         |

| 13         | GND         |

| 14         | GND         |

#### 2.5. Memories

The list of the memory carried in this product is shown in Table 2.5.1.

Table 2.5.1 memory list

| Classification | Start address | Size | Bus width | Note                                        |

|----------------|---------------|------|-----------|---------------------------------------------|

| External FROM  | H'0000_0000   | 64MB | 32bit     | At the time of mounting of an enclosed FROM |

|                |               |      |           | board                                       |

| External SDRAM | H'0C00_0000   | 64MB | 32bit     |                                             |

# 2.5.1. An Access Timing Setup to Each Device Connected to SH Bus

The timing specification of each device linked to the SH7751R local bus of this board is shown in Table 2.5.2.

(STATUS: Input clock is 20MHz and CPU modeis mode5)

Table 2.5.2 The timing specification of each device

| Area | Classification       | Product name      | Bus width | Timing specifications                                                                    |

|------|----------------------|-------------------|-----------|------------------------------------------------------------------------------------------|

| 0    | FROM Board           | S29PL127J60TFI130 | 32        | The number of soft waits: 9                                                              |

| 1    | FPGA                 | EP1C4F400C8N      | 16        | The number of soft waits: 3                                                              |

| 3    | SDRAM                | EDS2516ADTA-75-E  | 32        | CAS latency: 3                                                                           |

| 4    | 2DGraphic controller | SM501GX08LF00-AB  | 32        | The number of soft waits: 9                                                              |

| 5    | CF card              | CF card           | 16        | The number of SH7751R soft waits: 12 The CFCTL register of FPGA also needs to be set up. |

#### 2.6. PCI Devices

With this board, one PCI connector, one CardBus card controller, and two LAN controllers are connected to the PCI bus of SH7751R. One of two LAN controllers connects a Hub controller, and it has 4 ports.

Each device number (DEVNO) is shown in Table 2.6.1. A device number is a number of a device set as the object of configuration access.

Table 2.6.1 device number list

| DEVNO | Device                        | Function                                | Interruption |

|-------|-------------------------------|-----------------------------------------|--------------|

| H'0   | PCI card connector            | all-purpose PCI card                    | PCI_INTA     |

| H'1   | RTL8139DL<br>(with RTL8305SB) | Ethernet 10/100Base (with Ethernet Hub) | PCI_INTB     |

| H'2   | PCI1520ZHK                    | PCI – CardBus bridge                    | PCI_INTC     |

| H'3   | RTL8139DL                     | Ethernet 10/100Base                     | PCI_INTD     |

#### 2.6.1. PCI Card Slot

CN2 is a PCI card connector. It has connected with the PCI bus of SH7751R.

Although the connector based on PCI 5V card specification is mounted, a PCI bus signal should use the card of 3.3V signal specification for the specification of SH7751R. If 5V signal is supplied to SH7751R, there is a possibility of destroying SH7751R.

#### 2.6.2. CardBus Card Connector

CN3 is a CardBus card controller, PCI1520ZHK (made from Texas Instruments) is connected to the PCI bus of SH7751R.

This controller supports the PC card and 3.3V CardBus card of 5V/3.3V mixture.

Please refer to the data of PCI1520ZHK about the details of the usage.

# 2.6.3. LAN Connector

This board -- as an Ethernet controller -- the product made from REALTEK -- two RTL8139DL(s) are mounted.

Please refer to the data of RTL8139DL about the details of the usage.

Moreover, RTL8139DL arranged for the device number 1 is connected to Hub controller RTL8305SB.

A Hub-controller (RTL8305SB) supports 4 ports.

# 2.6.3.1. MAC Address Assignment

The MAC Address is written in external EEPROM of RTL8139DL. Please refer to MAC1 and MAC2 on the solder side of this product.

MAC1 is supported the device number 1 and MAC2 is supported the device number 3.

# 2.7. 2D Graphic Controller Interface

This board -- as 2D graphic controller -- Silicon Motion Inc. make -- SM501GX08LF00-AB is mounted. It has connected with SH bus. About the "RDY" signal to SH7751R, timing adjustment is carried out in FPGA. Please refer to the data of SM501GX08LF00-AB about the details of the usage.

HCLK supplied to SM501GX about this product is use limitation in a laboratory, and Silicon Motion Inc. consents to operation by a maximum of 120MHz. In the adoption to a user's product, please perform a sufficient examination and sufficient evaluation.

#### 2.7.1. CRT Connector

CN12 is a connector for CRT connection. It has connected with the CRT output terminal of SM501. Signal arrangement of the connector for CRT interfaces is shown in Table 2.7.1.

Table 2.7.1 Signal arrangement of connector for CRT interfaces

| Pin number | Signal name |

|------------|-------------|

| 1          | R           |

| 2          | G           |

| 3          | В           |

| 4          | NC          |

| 5          | GND         |

| 6          | GND         |

| 7          | GND         |

| 8          | GND         |

| 9          | NC          |

| 10         | GND         |

| 11         | NC          |

| 12         | NC          |

| 13         | CRTHS       |

| 14         | CRTVS       |

| 15         | NC          |

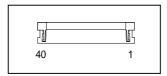

#### 2.7.2. LCD Connector

CN11 is a connector for LCD interfaces. It has connected with the LCD output terminal of SM501.

Please use it according to the specification of LCD which the user adopted. The supply voltage of LCD can be chosen in JP1. The connectors currently used are 40 FLH-SM1-TB (LF), and (SN) (made from the J.S.T. Mfg Co.,Ltd) The appearance figure of the connector for LCD interfaces is shown in Fig. 2.7.2, and signal arrangement is shown in Table 2.7.2.

Figure 2.7.2 Connector appearance figure for LCD interfaces

Table 2.7.2 Signal arrangement of connector for LCD interfaces

| Pin number  | Signal name | 1 connector for LCD interfaces  Note      |  |

|-------------|-------------|-------------------------------------------|--|

| 1 in number | GND         | Note                                      |  |

| 2           | CK          | Clock signal                              |  |

| 3           | GND         | Clock Signal                              |  |

| 4           |             | Horizontal Synchronizing signal           |  |

|             | HSYNC       | Horizontal Synchronizing signal           |  |

| 5           | GND         | Warding I Complement in a pictural        |  |

| 6           | VSYNC       | Vertical Synchronizing signal             |  |

| 7           | GND         |                                           |  |

| 8           | R0          | _                                         |  |

| 9           | R1          | _                                         |  |

| 10          | R2          | Red data                                  |  |

| 11          | R3          | _                                         |  |

| 12          | R4          |                                           |  |

| 13          | R5          |                                           |  |

| 14          | GND         |                                           |  |

| 15          | G0          |                                           |  |

| 16          | G1          |                                           |  |

| 17          | G2          | Green data                                |  |

| 18          | G3          |                                           |  |

| 19          | G4          |                                           |  |

| 20          | G5          |                                           |  |

| 21          | GND         |                                           |  |

| 22          | B0          |                                           |  |

| 23          | B1          |                                           |  |

| 24          | B2          | Blue data                                 |  |

| 25          | В3          | Diue data                                 |  |

| 26          | B4          |                                           |  |

| 27          | B5          |                                           |  |

| 28          | GND         |                                           |  |

| 29          | FPEN        | LCD enable                                |  |

| 30          | GND         |                                           |  |

| 31          | GND         |                                           |  |

| 32          | NC          |                                           |  |

| 33          | NC          |                                           |  |

| 34          | VCC         |                                           |  |

| 35          | VCC         |                                           |  |

| 36          | VCC         | 3.3V/5.0V change is possible at J1.       |  |

| 37          | VCC         | 1-2 short-circuit: 3.3V                   |  |

| 38          | VCC         | 2-3 short-circuit: 5.0V                   |  |

| 39          | VCC         | It is 3.3V setup at the time of shipment. |  |

| 40          | VCC         |                                           |  |

# 2.7.3. LCD Back Light Connector

CN10 is a connector for LCD inverter connection. The appearance figure of the connector for LCD inverter connection is shown in Fig. 2.7.3, and signal arrangement of the connector for LCD inverter connection is shown in Table 2.7.3. The connector currently used is the product 53261-0571 made from Molex. Conformity housing is 51021-0500.

Figure 2.7.3 Connector appearance figure for LCD inverter connection

Table 2.7.2 Signal arrangement of connector for LCD inverter connection

| Pin number | Signal name | Note                 |

|------------|-------------|----------------------|

| 1          | VCC         | 12.0V                |

| 2          | GND         |                      |

| 3          | VRMT        | Inverter ON/OFF      |

| 4          | VR0         | Brightness (however, |

| 5          | VR1         | short at 20Kohm).    |

#### 2.7.4. USB Connector

CN15 and CN16 are the connectors for USB connection. The USB terminal of SM501 is connected to LSI for USB Hub, and 2ch mounting is carried out. It is based on USB1.1.

# 2.7.5. SM501 Extention Connector

CN17 has connected the signal of I2C of SM501 and a ZV port, and AC97 and UART. The connector has not mounted. Please prepare of a user if needed. An assumption connector is the product 52837-0679 made from Molex. Signal arrangement is shown in Table 2.7.5.

Table 2.7.5 Signal arrangement of SM501 extension interface connector

| Pin number | Signal name | Note    | Pin number | Signal name | Note    |

|------------|-------------|---------|------------|-------------|---------|

| 1          | 5.0V        |         | 31         | GPIO59      | ZV port |

| 2          | 5.0V        |         | 32         | GPIO29      |         |

| 3          | 5.0V        |         | 33         | GPIO60      | ZV port |

| 4          | 5.0V        |         | 34         | GPIO37      | UART    |

| 5          | GND         |         | 35         | GPIO61      | ZV port |

| 6          | GND         |         | 36         | GND         |         |

| 7          | GPIO16      | ZV port | 37         | GPIO62      | ZV port |

| 8          | GND         |         | 38         | GND         |         |

| 9          | GPIO17      | ZV port | 39         | GPIO63      | ZV port |

| 10         | GND         |         | 40         | GND         |         |

| 11         | GPIO18      | ZV port | 41         | GND         |         |

| 12         | GPIO24      | AC97    | 42         | GPIO38      | UART    |

| 13         | GPIO19      | ZV port | 43         | VP_HREF     | ZV port |

| 14         | GPIO25      | AC97    | 44         | GND         |         |

| 15         | GPIO20      | ZV port | 45         | VP_VSYNC    | ZV port |

| 16         | GPIO26      | AC97    | 46         | GND         |         |

| 17         | GPIO21      | ZV port | 47         | VP_CLK      | ZV port |

| 18         | GND         |         | 48         | GND         |         |

| 19         | GPIO22      | ZV port | 49         | GND         |         |

| 20         | GND         |         | 50         | GPIO39      | UART    |

| 21         | GPIO23      | ZV port | 51         | I2CCK       | I2C     |

| 22         | GND         |         | 52         | GND         |         |

| 23         | GND         |         | 53         | GND         |         |

| 24         | GPIO27      | AC97    | 54         | GPIO40      | UART    |

| 25         | GPIO56      | ZV port | 55         | I2CDA       | I2CD    |

| 26         | GND         |         | 56         | GND         |         |

| 27         | GPIO57      | ZV port | 57         | GND         |         |

| 28         | GND         |         | 58         | GND         |         |

| 29         | GPIO58      | ZV port | 59         | 12V         |         |

| 30         | GPIO28      | AC97    | 60         | 12V         |         |

# 2.8. Touch Panel Connector

CN19 is a connector for interfaces for receiving the signal from LSI for touch-panel control. The inputted signal can be referred to in FPGA. Please prepare of a user about a touch-panel interface circuitry. Please refer to the clause of FPGA functional explanation about the specification of FPGA.

The appearance figure of the connector for touch-panel interfaces is shown in Fig. 2.8.1, and signal arrangement is shown in Table 2.8.1.

Figure 2.8.1 The connector appearance figure

Table 2.8.1 Signal arrangement of the connector (CN19)

| Pin number | Signal name | IO | Note                                                    |

|------------|-------------|----|---------------------------------------------------------|

| 1          | 3.3V        |    |                                                         |

| 2          | 3.3V        |    |                                                         |

| 3          | DCLK        | О  | Clock output (it can change on FPGA to 60kHz - 110kHz). |

| 4          | GND         |    |                                                         |

| 5          | CS#         | О  | Chip selection signal                                   |

| 6          | GND         |    |                                                         |

| 7          | DIN         | О  | Write Data                                              |

| 8          | GND         |    |                                                         |

| 9          | BUSY        | I  | Busy signal                                             |

| 10         | GND         |    |                                                         |

| 11         | DOUT        | I  | Read Data                                               |

| 12         | GND         |    |                                                         |

| 13         | IRQ#        | I  | Interruption                                            |

| 14         | GND         |    |                                                         |

# 2.9. SH Bus Extention Connector

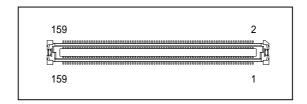

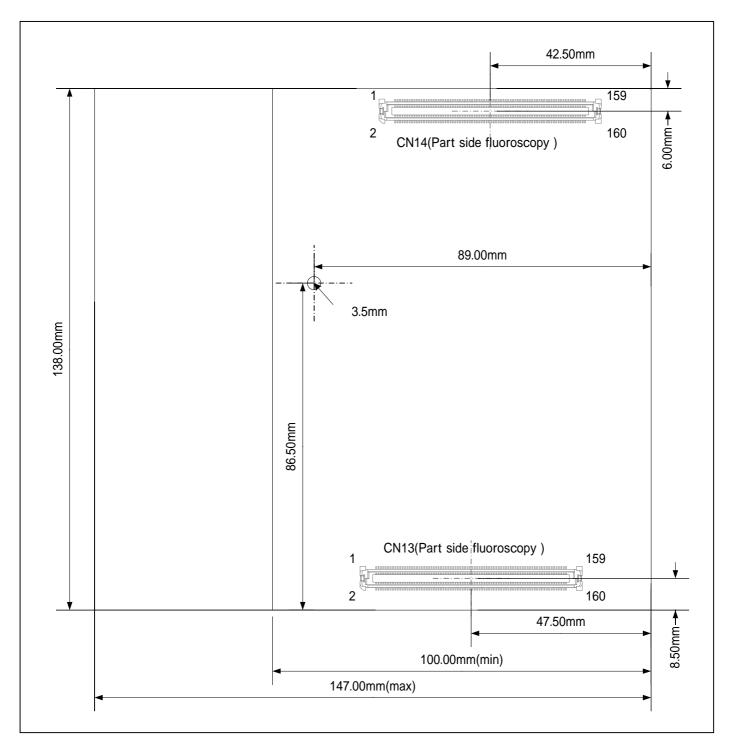

CN13 and CN14 are SH bus extension interface connectors. General-purpose from SH bus and FPGA for extension I/O is connected. The general-view figure of SH bus extension interface connector is shown in Fig. 2.9.1, and signal arrangement is shown in Table 2.9.1 and Table 2.9.2. A use connector is the product 52837-1679 made from Molex. Please refer to the clause of FPGA functional explanation about the specification of FPGA.

Figure 2.9.1 SH bus extension interface connector general-view figure

Table 2.9.1 Signal arrangement of SH bus extension interface connector (CN13)

| Pin number | Signal name | IO | Note |

|------------|-------------|----|------|

| 1          | 3.3V        |    |      |

| 2          | 3.3V        |    |      |

| 3          | 3.3V        |    |      |

| 4          | 3.3V        |    |      |

| 5          | 5.0V        |    |      |

| 6          | 5.0V        |    |      |

| 7          | 5.0V        |    |      |

| 8          | 5.0V        |    |      |

| 9          | GND         |    |      |

| 10         | GND         |    |      |

| 11         | CKIO        | О  |      |

| 12         | GND         |    |      |

| 13         | GND         |    |      |

| 14         | EXT_D0      | IO |      |

| 15         | EXT_D1      | IO |      |

| 16         | GND         |    |      |

| 17         | GND         |    |      |

| 18         | EXT_D2      | IO |      |

| 19         | EXT_D3      | IO |      |

| 20         | GND         |    |      |

| 21         | GND         |    |      |

| 22         | EXT_D4      | IO |      |

| 23         | EXT_D5      | IO |      |

| 24         | GND         |    |      |

| 25         | GND         |    |      |

| 26         | EXT_D6      | IO |      |

| 27         | EXT_D7      | IO |      |

| 28         | GND         |    |      |

| 29         | GND         |    |      |

| 30         | EXT_D8      | IO |      |

| 31         | EXT_D9      | IO |      |

| 32         | GND         |    |      |

| 33         | GND         |    |      |

| 34         | EXT_D10     | IO |      |

| 35         | EXT D11     | IO |      |

| Pin number | Signal name | IO | Note                                   |

|------------|-------------|----|----------------------------------------|

| 36         | GND         |    |                                        |

| 37         | GND         |    |                                        |

| 38         | EXT_D12     | IO |                                        |

| 39         | EXT_D13     | IO |                                        |

| 40         | GND         |    |                                        |

| 41         | GND         |    |                                        |

| 42         | EXT_D14     | IO |                                        |

| 43         | EXT_D15     | IO |                                        |

| 44         | GND         |    |                                        |

| 45         | GND         |    |                                        |

| 46         | EXT_D16     | IO |                                        |

| 47         | EXT_D17     | IO |                                        |

| 48         | GND         |    |                                        |

| 49         | GND         |    |                                        |

| 50         | EXT_D18     | IO |                                        |

| 51         | EXT_D19     | IO |                                        |

| 52         | GND         |    |                                        |

| 53         | GND         |    |                                        |

| 54         | EXT_D20     | IO |                                        |

| 55         | EXT_D21     | IO |                                        |

| 56         | GND         |    |                                        |

| 57         | GND         |    |                                        |

| 58         | EXT_D22     | IO |                                        |

| 59         | EXT_D23     | IO |                                        |

| 60         | GND         |    |                                        |

| 61         | GND         |    |                                        |

| 62         | EXT_D24     | IO |                                        |

| 63         | EXT_D25     | IO |                                        |

| 64         | GND         |    |                                        |

| 65         | GND         |    |                                        |

| 66         | EXT_D26     | IO |                                        |

| 67         | EXT_D27     | IO |                                        |

| 68         | GND         |    |                                        |

| 69         | GND         |    |                                        |

| 70         | EXT_D28     | IO |                                        |

| 71         | EXT_D29     | IO |                                        |

| 72         | GND         |    |                                        |

| 73         | GND         |    |                                        |

| 74         | EXT_D30     | IO |                                        |

| 75         | EXT_D31     | IO |                                        |

| 76         | GND         |    |                                        |

| 77         | GND         |    |                                        |

| 78         | EXT_RST_OUT | О  | The reset output to an expansive board |

| 79         | EXT_RST_IN  | I  | Reset input from an expansive board    |

| 80         | GND         |    |                                        |

| 81         | GND         |    |                                        |

| 82         | GND         |    |                                        |

| 83         | GND         |    |                                        |

| 84         | FPGA_GPIO21 | IO | It is controlled by FPGA               |

| 85         | FPGA_GPIO22 | IO | It is controlled by FPGA               |

| Pin number | Signal name        | IO | Note                     |

|------------|--------------------|----|--------------------------|

| 86         | GND                |    |                          |

| 87         | GND                |    |                          |

| 88         | FPGA_GPIO23        | IO | It is controlled by FPGA |

| 89         | FPGA_GPIO24        | IO | It is controlled by FPGA |

| 90         | GND                |    |                          |

| 91         | GND                |    |                          |

| 92         | FPGA_GPIO25        | IO | It is controlled by FPGA |

| 93         | FPGA_GPIO26        | IO | It is controlled by FPGA |

| 94         | GND                |    |                          |

| 95         | GND                |    |                          |

| 96         | FPGA_GPIO27        | IO | It is controlled by FPGA |

| 97         | FPGA_GPIO28        | IO | It is controlled by FPGA |

| 98         | GND                |    |                          |

| 99         | GND                |    |                          |

| 100        | FPGA_GPIO29        | IO | It is controlled by FPGA |

| 101        | FPGA_GPIO30        | IO | It is controlled by FPGA |

| 102        | GND                |    |                          |

| 103        | GND                |    |                          |

| 104        | FPGA_GPIO31        | IO | It is controlled by FPGA |

| 105        | FPGA_GPIO32        | IO | It is controlled by FPGA |

| 106        | GND                |    |                          |

| 107        | GND                |    |                          |

| 108        | FPGA_GPIO33        | IO | It is controlled by FPGA |

| 109        | FPGA_GPIO34        | IO | It is controlled by FPGA |

| 110        | GND                |    |                          |

| 111        | GND                |    |                          |

| 112        | FPGA_GPIO35        | IO | It is controlled by FPGA |

| 113        | FPGA_GPIO36        | IO | It is controlled by FPGA |

| 114        | GND                |    |                          |

| 115        | GND                |    |                          |

| 116        | FPGA_GPIO37        | IO | It is controlled by FPGA |

| 117        | FPGA_GPIO38        | IO | It is controlled by FPGA |

| 118        | GND                |    |                          |

| 119        | GND                |    |                          |

| 120        | FPGA_GPIO39        | IO | It is controlled by FPGA |

| 121        | FPGA_GPIO40        | IO | It is controlled by FPGA |

| 122        | GND                |    |                          |

| 123        | GND                |    |                          |

| 124        | FPGA_GPIO41        | IO | It is controlled by FPGA |

| 125        | FPGA_GPIO42        | IO | It is controlled by FPGA |

| 126        | GND                |    |                          |

| 127        | GND                | 10 | T                        |

| 128        | FPGA_GPIO43        | IO | It is controlled by FPGA |

| 129        | FPGA_GPIO44        | IO | It is controlled by FPGA |

| 130        | GND                |    |                          |

| 131        | GND<br>FRCA CRICAS | 10 | T                        |

| 132        | FPGA_GPIO45        | IO | It is controlled by FPGA |

| 133        | FPGA_GPIO46        | IO | It is controlled by FPGA |

| 134        | GND                |    |                          |

| 135        | GND                |    |                          |

| Pin number | Signal name | IO | Note                     |

|------------|-------------|----|--------------------------|

| 136        | FPGA_GPIO47 | IO | It is controlled by FPGA |

| 137        | FPGA_GPIO48 | IO | It is controlled by FPGA |

| 138        | GND         |    |                          |

| 139        | GND         |    |                          |

| 140        | FPGA_GPIO49 | IO | It is controlled by FPGA |

| 141        | FPGA_GPIO50 | IO | It is controlled by FPGA |

| 142        | GND         |    |                          |

| 143        | GND         |    |                          |

| 144        | FPGA_GPIO51 | IO | It is controlled by FPGA |

| 145        | FPGA_GPIO52 | IO | It is controlled by FPGA |

| 146        | GND         |    |                          |

| 147        | GND         |    |                          |

| 148        | FPGA_GPIO53 | IO | It is controlled by FPGA |

| 149        | GND         |    |                          |

| 150        | GND         |    |                          |

| 151        | GND         |    |                          |

| 152        | GND         |    |                          |

| 153        | 3.3V        |    |                          |

| 154        | 3.3V        |    |                          |

| 155        | 3.3V        |    |                          |

| 156        | 3.3V        |    |                          |

| 157        | 12V         |    |                          |

| 158        | 12V         |    |                          |

| 159        | 12V         |    |                          |

| 160        | 12V         |    |                          |

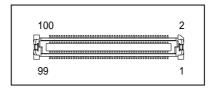

Table 2.9.2 Signal arrangement of SH bus extension interface connector (CN14)

| Pin number | Signal name | IO | Note |

|------------|-------------|----|------|

| 1          | 3.3V        |    |      |

| 2          | 3.3V        |    |      |

| 3          | 3.3V        |    |      |

| 4          | 3.3V        |    |      |

| 5          | 5.0V        |    |      |

| 6          | 5.0V        |    |      |

| 7          | 5.0V        |    |      |

| 8          | 5.0V        |    |      |

| 9          | GND         |    |      |

| 10         | GND         |    |      |

| 11         | EXT_A0      | О  |      |

| 12         | GND         |    |      |

| 13         | GND         |    |      |

| 14         | EXT_A1      | О  |      |

| 15         | EXT_A2      | О  |      |

| 16         | GND         |    |      |

| 17         | GND         |    |      |

| 18         | EXT_A3      | О  |      |

| 19         | EXT_A4      | О  |      |

| 20         | GND         |    |      |

| 21         | GND         |    |      |

| 22         | EXT_A5      | О  |      |

| 23         | EXT_A6      | О  |      |

| 24         | GND         |    |      |

| 25         | GND         |    |      |

| Pin number | Signal name | IO | Note |

|------------|-------------|----|------|

| 26         | EXT_A7      | О  |      |

| 27         | EXT_A8      | О  |      |

| 28         | GND         |    |      |

| 29         | GND         |    |      |

| 30         | EXT_A9      | О  |      |

| 31         | EXT_A10     | О  |      |

| 32         | GND         |    |      |

| 33         | GND         |    |      |

| 34         | EXT_A11     | О  |      |

| 35         | EXT_A12     | О  |      |

| 36         | GND         |    |      |

| 37         | GND         |    |      |

| 38         | EXT_A13     | О  |      |

| 39         | EXT_A14     | О  |      |

| 40         | GND         |    |      |

| 41         | GND         |    |      |

| 42         | EXT_A15     | О  |      |

| 43         | EXT_A16     | О  |      |

| 44         | GND         |    |      |

| 45         | GND         |    |      |

| 46         | EXT_A17     | О  |      |

| 47         | EXT_A18     | О  |      |

| 48         | GND         |    |      |

| 49         | GND         |    |      |

| 50         | EXT_A19     | О  |      |

| 51         | EXT A20     | О  |      |

| 52         | GND         |    |      |

| 53         | GND         |    |      |

| 54         | EXT A21     | О  |      |

| 55         | EXT_A22     | О  |      |

| 56         | GND         |    |      |

| 57         | GND         |    |      |

| 58         | EXT_A23     | О  |      |

| 59         | EXT A24     | О  |      |

| 60         | GND         |    |      |

| 61         | GND         |    |      |

| 62         | EXT_A25     | О  |      |

| 63         | EXT_CS0#    | О  |      |

| 64         | GND         |    |      |

| 65         | GND         |    |      |

| 66         | EXT CS1#    | О  |      |

| 67         | EXT BS#     | О  |      |

| 68         | GND         |    |      |

| 69         | GND         |    |      |

| 70         | EXT RD#     | О  |      |

| 71         | EXT RD/WR#  | 0  |      |

| 72         | GND         |    |      |

| 73         | GND         |    |      |

| 74         | EXT WE0#    | О  |      |

| 75         | EXT WE1#    | 0  |      |

| Pin number | Signal name | IO | Note                                 |

|------------|-------------|----|--------------------------------------|

| 76         | GND         |    |                                      |

| 77         | GND         |    |                                      |

| 78         | EXT_WE2#    | О  |                                      |

| 79         | EXT_WE3#    | О  |                                      |

| 80         | GND         |    |                                      |

| 81         | GND         |    |                                      |

| 82         | EXT_INT0    | I  | Interruption from an expansive board |

| 83         | EXT_INT1    | I  | Interruption from an expansive board |

| 84         | GND         |    |                                      |

| 85         | GND         |    |                                      |

| 86         | EXT_INT2    | I  | Interruption from an expansive board |

| 87         | EXT_INT3    | I  | Interruption from an expansive board |

| 88         | GND         |    |                                      |

| 89         | GND         |    |                                      |

| 90         | EXT_DREQ0#  | I  |                                      |

| 91         | EXT_DREQ1#  | I  |                                      |

| 92         | GND         |    |                                      |

| 93         | GND         |    |                                      |

| 94         | EXT_DRAK0   | О  |                                      |

| 95         | EXT_DRAK1   | O  |                                      |

| 96         | GND         |    |                                      |

| 97         | GND         |    |                                      |

| 98         | EXT_DACK0   | О  |                                      |

| 99         | EXT_DACK1   | O  |                                      |

| 100        | GND         |    |                                      |

| 101        | GND         |    |                                      |

| 102        | EXT_CE2A#   | O  |                                      |

| 103        | EXT_CE2B#   | O  |                                      |

| 104        | GND         |    |                                      |

| 105        | GND         |    |                                      |

| 106        | EXT_RDY#    | I  |                                      |

| 107        | EXT_IOIS16  | IO |                                      |

| 108        | GND         |    |                                      |

| 109        | GND         |    |                                      |

| 110        | GND         |    |                                      |

| 111        | GND         |    |                                      |

| 112        | FPGA_GPIO0  | IO | It is controlled by FPGA             |

| 113        | FPGA_GPIO1  | IO | It is controlled by FPGA             |

| 114        | GND         |    |                                      |

| 115        | GND         |    |                                      |

| 116        | FPGA_GPIO2  | IO | It is controlled by FPGA             |

| 117        | FPGA_GPIO3  | IO | It is controlled by FPGA             |

| 118        | GND         |    |                                      |

| 119        | GND         |    |                                      |