### PIC18F45J10 Family Data Sheet Errata

## Clarifications/Corrections to the Data Sheet:

In the PIC18F45J10 Family Device Data Sheet (DS39682**C**), the following clarifications and corrections should be noted. Any silicon issues related to this device will reported in a separate silicon errata. Please check the Microchip web site for any existing issues.

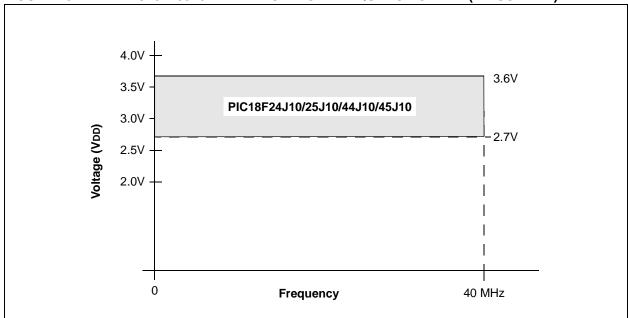

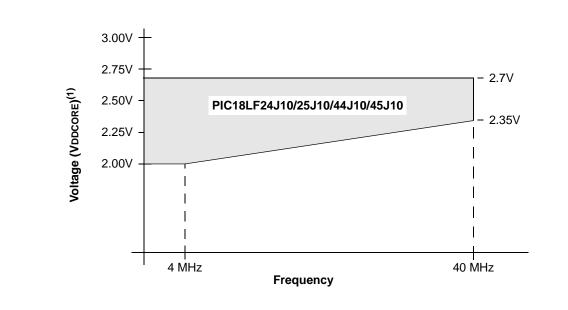

# 1. Module: Electrical Specifications (V/F Performance)

Figures 23-1 and 23-2 of the device data sheet, documenting frequency performance of the devices across the VDD range, have been updated. The new versions of the graphs are presented below.

**Note 1:** For these devices, the regulator BOR circuit will automatically trigger a device Reset before VDD reaches a level at which full-speed operation is not possible.

FIGURE 23-2: PIC18LF45J10 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

For frequencies between 4 MHz and 40 MHz, FMAX = (51.42 MHz/V) \* (VDDCORE - 2V) + 4 MHz

**Note 1:** For devices without the voltage regulator, VDD and VDDCORE must be maintained so that VDDCORE  $\leq$  VDD  $\leq$  3.6V.

# 2. Module: Table 23-1: Memory Programming Requirements

On page 307, the parameter D132, which gives the minimum and maximum voltage levels of the Self-Timed Erase or Write for VDD and VDDCORE, has been included. Parameter D133B and D140 and their corresponding values are added. The changed/appended values are indicated in bold text in the following table:

TABLE 23-1: MEMORY PROGRAMMING REQUIREMENTS

| DC CHARACTERISTICS |       |                                       | Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for industrial |      |     |            |                                                |  |  |

|--------------------|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|-----|------------|------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                        | Min Typ† Max Units                                                                                              |      |     | Conditions |                                                |  |  |

|                    |       | Program Flash Memory                  |                                                                                                                 |      |     |            |                                                |  |  |

| D130               | ЕР    | Cell Endurance                        | 100                                                                                                             | 1K   | _   | E/W        | -40°C to +85°C                                 |  |  |

| D131               | VPR   | VDD for Read                          | VMIN                                                                                                            | _    | 3.6 | V          | VMIN = Minimum operating voltage               |  |  |

| D132               | VPEW  | Voltage for Self-Timed Erase or Write |                                                                                                                 |      |     |            |                                                |  |  |

|                    |       | VDD                                   | 2.7                                                                                                             | _    | 3.6 | V          | PIC18FXXJ10                                    |  |  |

|                    |       | VDDCORE                               | 2.25                                                                                                            | _    | 2.7 | V          | PIC18LFXXJ10                                   |  |  |

| D133A              | Tıw   | Self-Timed Write Cycle Time           | _                                                                                                               | 2.8  | _   | ms         |                                                |  |  |

| D133B              | TIE   | Self-Timed Page Erased Cycle Time     | _                                                                                                               | 33.0 | _   | ms         |                                                |  |  |

| D134               | TRETD | Characteristic Retention              | 20                                                                                                              | _    | _   | Year       | Provided, no other specifications are violated |  |  |

| D135               | IDDP  | Supply Current during<br>Programming  | _                                                                                                               | 10   | _   | mA         |                                                |  |  |

| D140               | TWE   | Writes per Erase Cycle                | _                                                                                                               | _    | 1   | _          | For each physical address                      |  |  |

<sup>†</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 3. Module: Table 23-2: Comparator Specifications

On page 308, the maximum Input Offset Voltage (Param No. D300) is changed to ±25 mV.

The parameter numbers for TRESP, TMC2OV and VIRV are changed to D303 and D304, respectively.

The parameter D305 for Internal Reference Voltage is added.

The note stating "\* These parameters are characterized but not tested." is removed.

The changed content is indicated in bold text in the following table:

#### TABLE 23-2: COMPARATOR SPECIFICATIONS

| Operating Conditions: 3.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |        |                                           |     |       |           |       |          |  |

|---------------------------------------------------------------------------------------|--------|-------------------------------------------|-----|-------|-----------|-------|----------|--|

| Param<br>No.                                                                          | Sym    | Characteristics                           | Min | Тур   | Max       | Units | Comments |  |

| D300                                                                                  | VIOFF  | Input Offset Voltage                      |     | ± 5.0 | ± 25      | mV    |          |  |

| D301                                                                                  | VICM   | Input Common Mode Voltage                 | 0   | _     | VDD - 1.5 | V     |          |  |

| D302                                                                                  | CMRR   | Common Mode Rejection Ratio               | 55  | _     | _         | dB    |          |  |

| D303                                                                                  | TRESP  | Response Time <sup>(1)</sup>              | _   | 150   | 400       | ns    |          |  |

| D304                                                                                  | TMC2OV | Comparator Mode Change to<br>Output Valid | _   | _     | 10        | μS    |          |  |

| D305                                                                                  | VIRV   | Internal Reference Voltage                | 1   | 1.2   | _         | ٧     |          |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

## 4. Module: Table 23-4: Internal Voltage Regulator Specifications

On Page 308, the comment for the External Filter Capacitor value, CEFC, is changed. The note stating "\* These parameters are characterized but not tested. Parameter numbers not yet assigned for these specifications." is removed. The modified value is indicated in bold text in the following table:

### **TABLE 23-4: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS**

| Operating Conditions: -40°C < TA < +85°C (unless otherwise stated)                   |        |                                 |     |     |   |    |                                                   |  |

|--------------------------------------------------------------------------------------|--------|---------------------------------|-----|-----|---|----|---------------------------------------------------|--|

| Param No.     Sym     Characteristics     Min     Typ     Max     Units     Comments |        |                                 |     |     |   |    | Comments                                          |  |

|                                                                                      | VRGOUT | Regulator Output Voltage        | _   | 2.5 | _ | V  | _                                                 |  |

|                                                                                      | CEFC   | External Filter Capacitor Value | 4.7 | 10  | _ | μF | Capacitor must be low series resistance (<5 Ohms) |  |

### 5. Module: Section 23.1 "DC

Characteristics: Supply Voltage"

On page 297, a new parameter, D005, which which gives the voltage limits for Brown-out Reset (BOR) is added. The changed content is indicated in bold text in the following table.

### 23.1 DC Characteristics: Supply Voltage

PIC18F24J10/25J10/44J10/45J10 (Industrial) PIC18LF24J10/25J10/44J10/45J10 (Industrial)

| PIC18F4      | <b>5J10 Fami</b> l<br>strial) | Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for industrial |                    |     |     |       |                                                                                                      |

|--------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-------|------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol                        | Characteristic                                                                                                  | Min                | Тур | Max | Units | Conditions                                                                                           |

| D001         | VDD                           | Supply Voltage                                                                                                  | VDDCORE            | _   | 3.6 | V     | PIC18LF4XJ10, PIC18LF2XJ10                                                                           |

| D001         | Vdd                           | Supply Voltage                                                                                                  | 2.7 <sup>(1)</sup> | _   | 3.6 | V     | PIC18F4X/2XJ10                                                                                       |

| D001B        | VDDCORE                       | External Supply for<br>Microcontroller Core                                                                     | 2.0                | _   | 2.7 | V     | Valid only in parts designated "LF".<br>See Section 20.3 "On-Chip<br>Voltage Regulator" for details. |

| D002         | VDR                           | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                    | 1.5                | _   | _   | V     | _                                                                                                    |

| D003         | VPOR                          | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal                                                | _                  | _   | TBD | V     | See Section 4.3 "Power-on Reset (POR)" for details.                                                  |

| D004         | SVDD                          | VDD Rise Rate<br>to ensure internal<br>Power-on Reset signal                                                    | 0.05               | _   | _   | V/ms  | See Section 4.3 "Power-on Reset (POR)" for details.                                                  |

| D005         | VBOR                          | Brown-out Reset (BOR)<br>Voltage                                                                                | 2.35               | 2.5 | 2.7 | ٧     |                                                                                                      |

**Legend:** TBD = To Be Determined

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

6. Module: Section 23.3 "DC

Characteristics: PIC18F45J10

Family (Industrial)

On page 305, the characteristics and conditions of the Input Leakage Current are updated for the Analog (D060) and included for the Digital (D060A) I/O ports. The changed values are indicated in bold text in the following table:

| DC CHA       | RACTE  | RISTICS                                              | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial |            |            |                                             |  |  |  |

|--------------|--------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|---------------------------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic                                       | Min                                                                                                                                                      | Max        | Units      | Conditions                                  |  |  |  |

|              | VIL    | Input Low Voltage                                    |                                                                                                                                                          |            |            |                                             |  |  |  |

|              |        | All I/O ports:                                       |                                                                                                                                                          |            |            |                                             |  |  |  |

| D030         |        | with TTL buffer                                      | Vss                                                                                                                                                      | 0.15 VDD   | V          | VDD < 3.3V                                  |  |  |  |

| D030A        |        |                                                      | _                                                                                                                                                        | 0.8        | V          | $3.3V \le VDD \le 3.6V$                     |  |  |  |

| D031         |        | with Schmitt Trigger buffer                          | Vss                                                                                                                                                      | 0.2 VDD    | V          |                                             |  |  |  |

| D032         |        | MCLR                                                 | Vss                                                                                                                                                      | 0.2 VDD    | V          |                                             |  |  |  |

| D033         |        | OSC1                                                 | Vss                                                                                                                                                      | 0.3 VDD    | V          | HS, HSPLL modes                             |  |  |  |

| D033A        |        | OSC1                                                 | Vss                                                                                                                                                      | 0.2 VDD    | V          | EC, ECPLL modes <sup>(1)</sup>              |  |  |  |

| D034         |        | T1CKI                                                | Vss                                                                                                                                                      | 0.3        | V          |                                             |  |  |  |

|              | VIH    | Input High Voltage                                   |                                                                                                                                                          |            |            |                                             |  |  |  |

|              |        | I/O ports with 5.5V tolerance: <sup>(4)</sup>        |                                                                                                                                                          |            |            |                                             |  |  |  |

| D040         |        | with TTL buffer                                      | 0.25 VDD + 0.8V                                                                                                                                          | VDD        | V          | VDD < 3.3V                                  |  |  |  |

| D040A        |        |                                                      | 2.0                                                                                                                                                      | VDD        | V          | $3.3V \le VDD \le 3.6V$                     |  |  |  |

| D041         |        | with Schmitt Trigger buffer                          | 0.8 VDD                                                                                                                                                  | VDD        | V          |                                             |  |  |  |

|              |        | I/O ports with non 5.5V tolerance: <sup>(4)</sup>    |                                                                                                                                                          |            |            |                                             |  |  |  |

| Dxxx         |        | with TTL buffer                                      | 0.25 VDD + 0.8V                                                                                                                                          | 5.5        | V          | VDD < 3.3V                                  |  |  |  |

| DxxxA        |        |                                                      | 2.0                                                                                                                                                      | 5.5        | V          | $3.3V \le VDD \le 3.6V$                     |  |  |  |

| Dxxx         |        | with Schmitt Trigger buffer                          | 0.8 VDD                                                                                                                                                  | 5.5        | V          |                                             |  |  |  |

| D042         |        | MCLR                                                 | 0.8 VDD                                                                                                                                                  | VDD        | V          |                                             |  |  |  |

| D043         |        | OSC1                                                 | 0.7 VDD                                                                                                                                                  | VDD        | V          | HS, HSPLL modes                             |  |  |  |

| D043A        |        | OSC1                                                 | 0.8 VDD                                                                                                                                                  | VDD        | V          | EC, ECPLL modes                             |  |  |  |

| D044         |        | T1CKI                                                | 1.6                                                                                                                                                      | VDD        | V          |                                             |  |  |  |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>               |                                                                                                                                                          |            |            |                                             |  |  |  |

| D060         |        | I/O ports with<br>5.5V tolerance: <sup>(4)</sup>     | _                                                                                                                                                        | ±1         | μА         | VSS ≤ VPIN ≤ VDD,<br>Pin at high-impedance  |  |  |  |

| D060A        |        | I/O ports with non<br>5.5V tolerance: <sup>(4)</sup> | _                                                                                                                                                        | ± <b>1</b> | μ <b>Α</b> | Vss ≤ VPIN ≤ 5.5V,<br>Pin at high-impedance |  |  |  |

| D061         |        | MCLR                                                 | _                                                                                                                                                        | ±1         | μΑ         | $Vss \le VPIN \le VDD$                      |  |  |  |

| D063         |        | OSC1                                                 | _                                                                                                                                                        | ±5         | μA         | $Vss \le VPIN \le VDD$                      |  |  |  |

- **Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC® device be driven with an external clock while in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: Refer to Table 9-2 for the pins that have corresponding tolerance limits.

## 7. Module: Section 15.3 "SPI Mode" and Section 15.4 "I<sup>2</sup>C™ Mode"

In **Section 15.3 "SPI Mode"** on page 145 and **Section 15.4 "I<sup>2</sup>C Mode"** on page 155, the following new note is included to describe the procedure to disable the MSSP module:

Note: Disabling the MSSP module by clearing the SSPEN (SSPxCON1<5>) bit may not reset the module. It is recommended to clear the SSPxSTAT, SSPxCON1 and SSPxCON2 registers and select the mode prior to setting the SSPEN bit to enable the MSSP module.

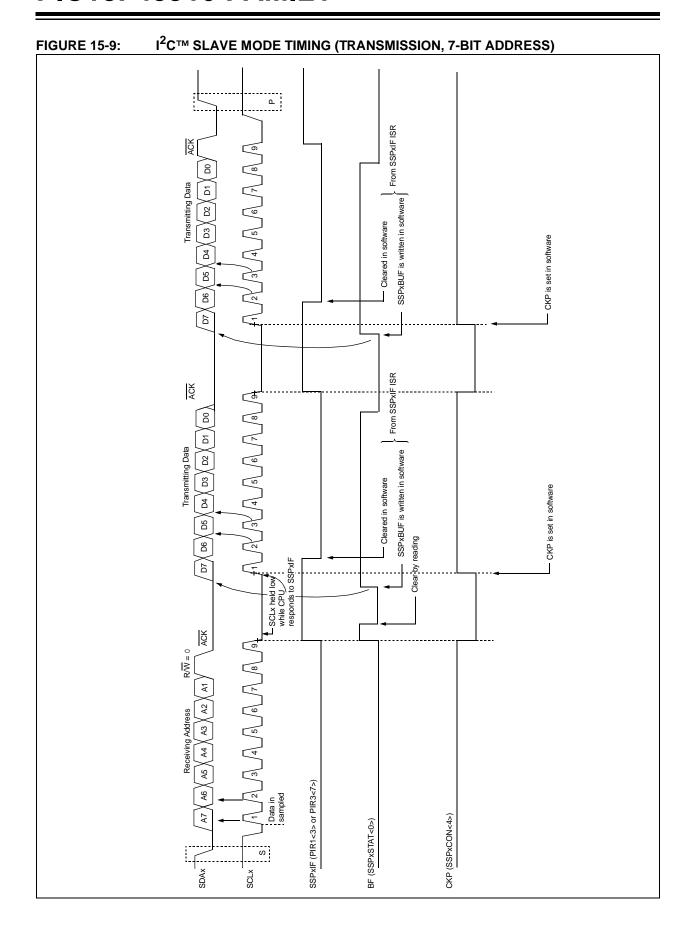

# 8. Module: Figure 15-9: I<sup>2</sup>C<sup>™</sup> Slave Mode Timing (Transmission, 7-Bit Address)

On page 162, the figure is replaced with a new timing diagram provided in Figure 15-9.

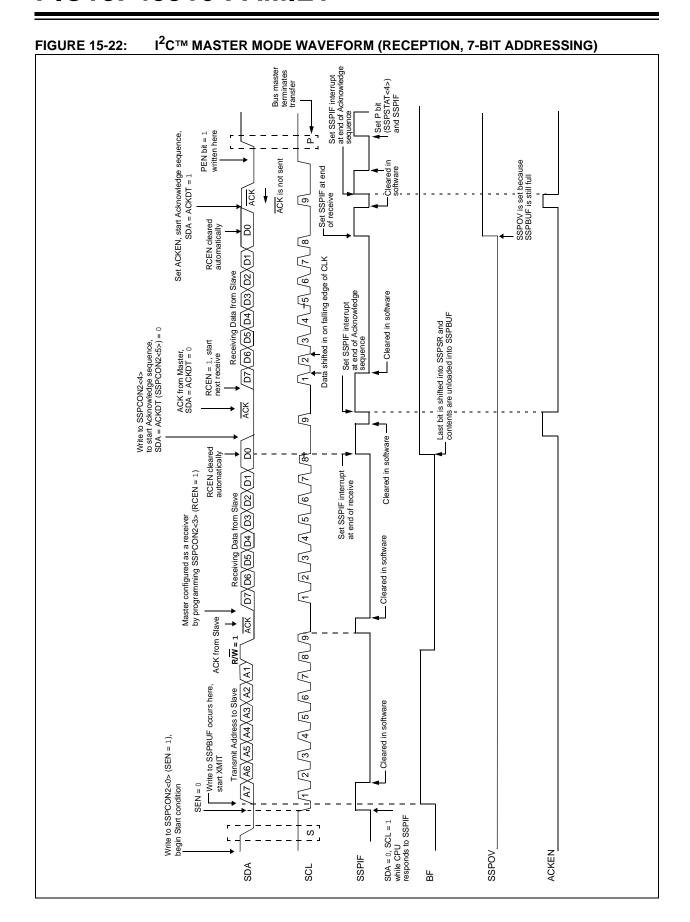

# 9. Module: Figure 15-22: I<sup>2</sup>C™ Master Mode Waveform (Reception, 7-Bit Address)

On page 178, the condition  $(R/\overline{W})$  when the Acknowledge signal (ACK) is received from the slave, after transmitting the address to the slave, is changed to '1'. The changed value is indicated in bold text in Figure 15-22.

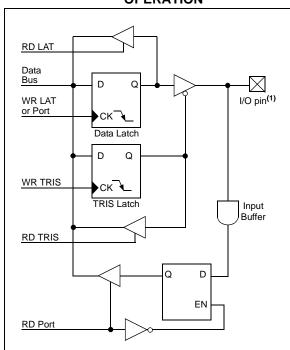

# 10. Module: Figure 9-1: Generic I/O Port Operation

The note in Figure 9-1 on page 93 is removed.

FIGURE 9-1: GENERIC I/O PORT OPERATION

### **REVISION HISTORY**

#### Rev A Document (03/2006)

Original version of this document. Includes Data Sheet Clarification 1 (Electrical Specifications – V/F Performance).

### Rev C Document (10/2008)

Added data sheet clarification issues 2 (Table 23-1: Memory Programming Requirements), 3 (Table 23-2: Comparator Specifications), 4 (Table 23-4: Internal Voltage Regulator Specifications), 5 (Section 23.1 "DC Characteristics"), 6 (Section 23.3 "DC Characteristics"), 7 (Section 15.3 "SPI Mode" and Section 15.4 "I $^2\text{C}^{\text{TM}}$  Mode"), 8 (Figure 15-9:  $I^2\text{C}^{\text{TM}}$  Slave Mode Timing — Transmission, 7-Bit Address), 9 (Figure 15-22:  $I^2\text{C}^{\text{TM}}$  Master Mode Waveform — Reception, 7-Bit Address) and 10 (Figure 9-1: Generic I/O Port Operation).

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

**Toronto**

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040

Fax: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-572-9526 Fax: 886-3-572-6459

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 **UK - Wokingham**

Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/02/08