# LVDS Dual 2x2 Crosspoint/Repeater Switch

#### **Features**

- Dual 2x2 Crosspoint/Repeater Switch

- Meets or Exceeds the Requirements of ANSI TIA/EIA-644-1995

- Designed for Signaling Rates up to 650 Mbit/s (325Mhz)

- Operates from a single 3.3V Supply: -40°C to 85°C

- Low-Voltage Differential Signaling with Output Voltages of ±350mV into:

- $100\Omega$  load (PI90LV044)

- 50Ω load Bus LVDS Signaling (PI90LVB044)

- Accepts ±350mV differential inputs

- Wide common mode input range: 0.2V to 2.7V

- Output drivers are high impedance when disabled or when  $V_{CC} \le 1.5V$

- Inputs are open, short, and terminated fail safe

- Propagation Delay Time: 3.5ns

- ESD protection is 10kV on bus pins

- Bus Pins are High Impedance when disabled or with V<sub>CC</sub> less than 1.5V

- TTL Inputs are 5V Tolerant

- Power Dissipation at 400 Mbit/s of 250mW

- Packaging (Pb-free & Green available):

- 28-pin QSOP (Q)

- 28-pin TSSOP (L)

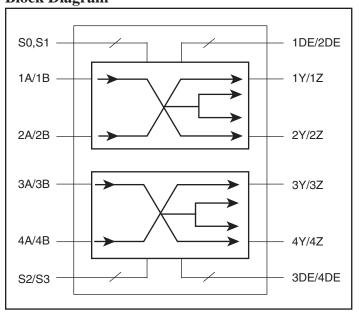

## **Block Diagram**

### **Description**

The PI90LV044 and PI90LVB044 are monolithic dual 2x2 asynchronous crosspoint/repeater switches. The crosspoint function is based on a multiplexer tree architecture. Each 2x2 switch can be considered as a pair of 2:1 multiplexers that share the same inputs. The signal path through each switch is fully differential with minimal propagation delay. The signal path is unregistered, so no clock is required for the data inputs. The signal line drivers and receivers use Low Voltage Differential Signaling (LVDS) to achieve signaling rates as high as 650Mbps.

The LVDS standard provides a minimum differential output voltage magnitude of 247 mV into a  $100\Omega$  load and receipt of 100 mV signals with up to 1V of ground potential difference between a transmitter and receiver. The PI90LVB044 doubles the output drive current to achieve LVDS levels with a 50 ohm load.

The intended application of these devices is for loop-through and redundant channel switching for both point-to-point baseband (PI90LV044) and multipoint (PI90LVB044) data transmissions over controlled impedance media.

### **Pin Configuration**

### **MUX Truth Table**

| Input  |        | Out           | Function      |          |

|--------|--------|---------------|---------------|----------|

| S3, S1 | S2, S0 | 1Y/1Z - 3Y/3Z | 2T/2Z - 4Y/4Z | runction |

| 0      | 0      | 1A/1B - 3A/3B | 1A/1B - 3A/3B | Splitter |

| 0      | 1      | 2A/2B - 4A/4B | 2A/2B - 4A/4B | Splitter |

| 1      | 0      | 1A/1B - 3A/3B | 1A/1B - 3A/3B | Router   |

| 1      | 1      | 2A/2B - 4A/4B | 2A/2B - 4A/4B | Router   |

#### Note:

1. Setting nDE to 0 will set Ouput nY/nZ to High Impedance.

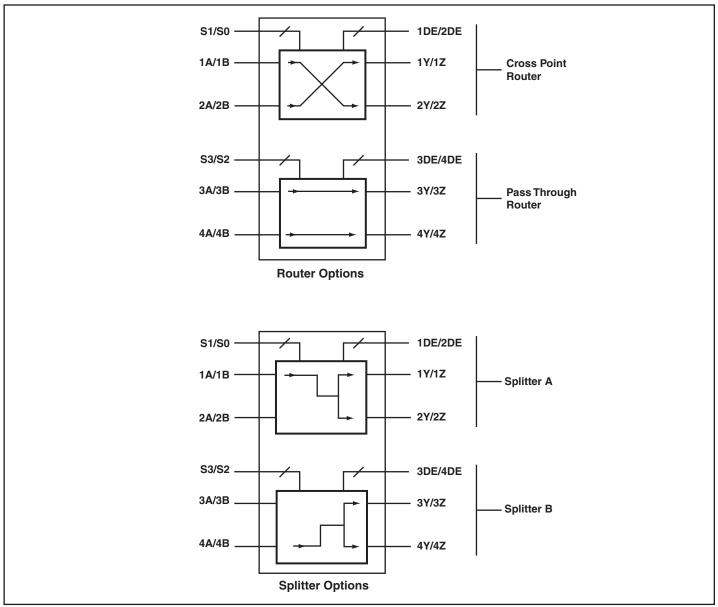

Figure 1. Possible Signal Routing

# Absolute Maximum Ratings Over Operating Free-Air Temperature $^{(1)}$

| Supply Voltage Range, V <sub>CC</sub> <sup>(1)</sup> 0.5V to 4V                      |

|--------------------------------------------------------------------------------------|

| Voltage Range (DE, S0, S1)–0.5 to 6V                                                 |

| Input Voltage Range, V <sub>I</sub> (A or B)0.5V to V <sub>CC</sub> + 0.5V           |

| Electrostatic Discharge: A, B, Y, Z, and GND <sup>(2)</sup> Class 3, A: 16kV, B:600V |

| All Pins                                                                             |

| Storage Temperature Range—65°C to 150°C                                              |

| Lead Temperature 1, 6 mm (1/16 inch) from case for 10 seconds260°C                   |

| 1                                                                                    |

#### **Notes:**

- Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not

implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

- 2. All voltage values, except differential I/O bus voltages, are with respect to ground terminal.

- 3. Tested in accordance with MIL-STD-883C Method 3015.7

# **Recommended Operating Conditions**

|                                                              |     | Min.                | Nom.                  | Max.                    | Units |

|--------------------------------------------------------------|-----|---------------------|-----------------------|-------------------------|-------|

| Supply Voltage, V <sub>CC</sub>                              | 3.0 | 3.3                 | 3.6                   | V                       |       |

| High-Level input voltage, V <sub>IH</sub> S1 - S3, 1DE - 4DE |     | 2                   |                       |                         |       |

| Low-Level input voltage, V <sub>IL</sub>                     |     |                     |                       | 0.8                     |       |

| Magnitude of Differential Input Voltage   V                  | 0.1 |                     | 0.6                   |                         |       |

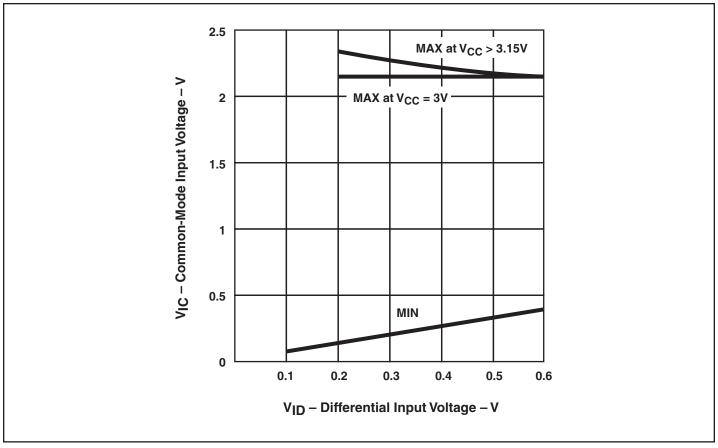

| Common Mode input voltage, V <sub>IC</sub> (see figure 2)    |     | V <sub>ID</sub>   2 |                       | 2.4 -   V <sub>ID</sub> |       |

|                                                              |     |                     | V <sub>CC</sub> - 0.8 |                         |       |

| Operating free-air Temperature, T <sub>A</sub>               | -40 |                     | 85                    | °C                      |       |

08-0295 3 PS8485F 11/11/08

Figure 2. Common-Mode Input Voltage vs. Differential Voltage

# Receiver Electrical Characteristics Over Recommended Operating Conditions (unless otherwise noted)

| Symbol               | Parameter                                           | Test Conditions           | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|----------------------|-----------------------------------------------------|---------------------------|------|---------------------|------|-------|

| V <sub>ITH+</sub>    | Positive going differential input voltage threshold | MCM = 1.2M                |      |                     | 100  | mV    |

| V <sub>ITH</sub> -   | Negative going differential input voltage threshold | tage threshold VCM = 1.2V |      |                     |      | 111 V |

| II                   | Input ourrant (A or D inputs)                       | VI = 0V                   | -2   |                     | -20  |       |

|                      | Input current (A or B inputs)                       | VI = 2.4V                 | -1.2 |                     |      | μΑ    |

| I <sub>I (OFF)</sub> | Power-off input current (A or B inputs)             | VCC = 0V                  |      |                     | 20   |       |

08-0295 4 PS8485F 11/11/08

# Receiver/Driver Electrical Characteristics Over Recommended Operating Conditions (unless otherwise noted)

| Symbol                          | Parameter                                                              |                 | Test Condition                                                    | Min.  | <b>Typ.</b> <sup>(1)</sup> | Max.  | Units |

|---------------------------------|------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------|-------|----------------------------|-------|-------|

| V <sub>OD</sub>                 | Differential Output voltage mag                                        | gnitude         |                                                                   | 247   | 440                        | 590   |       |

| $\Delta V_{\mathrm{OD}}$        | Change in differential Output voltage magnitude between logic states   |                 | $R_{L} = 100\Omega \text{ (LV)}$ $R_{L} = 50\Omega \text{ (LVB)}$ | -50   |                            | 50    | mV    |

| V <sub>OC(SS)</sub>             | Steady-state common-mode output voltage                                |                 |                                                                   | 1.062 |                            | 1.375 | V     |

| $\Delta V_{OC(SS)}$             | Change in steady-state common-mode output voltage between logic states |                 |                                                                   | -50   | 3                          | 50    | mV    |

| V <sub>OC(PP)</sub>             | Peak-to-peak common-mode or                                            | utput voltage   |                                                                   |       |                            | 150   |       |

|                                 |                                                                        | '               | No load                                                           |       | 16                         | 24    |       |

| I                               | Cumple Cumpant                                                         |                 | $R_L = 100\Omega (LV)$                                            |       | 26                         | 40    |       |

| I <sub>CC</sub> Supply Current  |                                                                        |                 | $R_{\rm L} = 50\Omega  ({\rm LVB})$                               |       | 42                         | 54    | mA    |

|                                 |                                                                        |                 | All Channels Disabled                                             |       | 6                          | 12    |       |

| Ivv                             | High level input current                                               | DE              | V <sub>IH</sub> = 5                                               |       |                            | 40    | nA    |

| 1IH                             |                                                                        | S1, S2, S3, S4  |                                                                   |       |                            | -3    | μΑ    |

| ${ m I}_{ m IL}$                | Low level input current                                                | DE              | $V_{\rm IL} = 0.8 V$                                              |       |                            | -20   | nA    |

| 1IL                             | Low level input current                                                | S1, S2, S3, S4  | V <sub>1L</sub> = 0.8 V                                           |       |                            | 10    | μΑ    |

| $I_{OS}$                        | Short circuit output current                                           |                 | $V_{OY}$ or $V_{OZ} = 0V$ ,<br>$V_{OD} = 0V$                      |       |                            | -10   | mA    |

| I High immediance autout aumont |                                                                        |                 | $V_{OD} = 600 \text{mV}$                                          |       | 1.5                        | ±25   |       |

| $I_{OZ}$                        | High impedence output current                                          |                 | V <sub>O</sub> - 0V or V <sub>CC</sub>                            |       | 1.5                        | ±25   | nA    |

| I <sub>O(OFF)</sub>             | Power off output current                                               |                 | $V_{CC} = 0V, V_{O} = 3.6V$                                       |       | 1.5                        | ±40   |       |

| Cny                             | Input Canacitance                                                      | put Capacitance |                                                                   |       | 3                          |       | nE    |

| $C_{IN}$                        | при Сараспансе                                                         |                 |                                                                   |       | 8                          |       | pF    |

### Note:

<sup>1.</sup> All typical values are at 25°C and with a 3.3 supply

## Differential Receiver to Driver Switching Characteristics Over Recommended Operating Conditions (unless otherwise noted)

| Symbol                  | Paran                                                       | <b>Test Condition</b> | Min.          | Typ.(1) | Max. | Units |    |

|-------------------------|-------------------------------------------------------------|-----------------------|---------------|---------|------|-------|----|

| t <sub>PLH</sub>        | Differential propagation delay, low-to-high                 |                       |               |         | 4.0  | 6.0   |    |

| t <sub>PHL</sub>        | Differential propagation delay, l                           | high-to-low           |               |         | 4.0  | 6.0   |    |

| t <sub>sk(p)</sub>      | Pulse skew ( $\mid t_{PHL} = t_{PLH} \mid$ )                |                       |               |         | 0.25 | 0.3   |    |

| 4                       | T                                                           | LV044                 | $C_L = 10 pF$ |         | 1.0  | 1.5   |    |

| l t <sub>r</sub>        | Transition, low-to-high                                     | LVB044                | ]             |         | 0.8  | 1.3   |    |

| ,                       | T '4' 1' 1 4 1                                              | LV044                 |               |         | 1.0  | 1.5   | ns |

| $t_{\rm f}$             | Transition, high-to-low                                     | LVB044                |               |         | 0.8  | 1.3   | 1  |

| t <sub>PHZ</sub>        | Propagation delay time, high-level-to-high-impedence output |                       |               |         | 4.0  | 10    |    |

| t <sub>PLZ</sub>        | Propagation delay time, low-level-to-high-impedance output  |                       |               |         | 4.3  | 10    |    |

| t <sub>PZH</sub>        | Propagation delay time, high-impedence to high-level output |                       |               |         | 3.0  | 10    |    |

| t <sub>PZL</sub>        | Propagation delay time, high-impdeence tolow-level output   |                       |               |         | 2.0  | 10    |    |

| t <sub>PHL</sub> _R1_Dx |                                                             |                       |               | -       | 95   |       |    |

| t <sub>PLH</sub> _R1_Dx | Channel to the sun of all arms are size                     |                       |               | -       | 95   |       |    |

| t <sub>PHL</sub> _R2_Dx | Channel-tochannel skew, receiver to driver <sup>(2)</sup>   |                       |               |         | -    | 95    | ps |

| t <sub>PLH</sub> _R2_Dx |                                                             |                       |               |         | -    | 95    |    |

#### **Notes:**

- 1. All typical values are at 25°C and with a 3.3 supply

- 2. These parametric values are measured over supply voltage and temperature ranges recommended for the device

08-0295 PS8485F 11/11/08 6

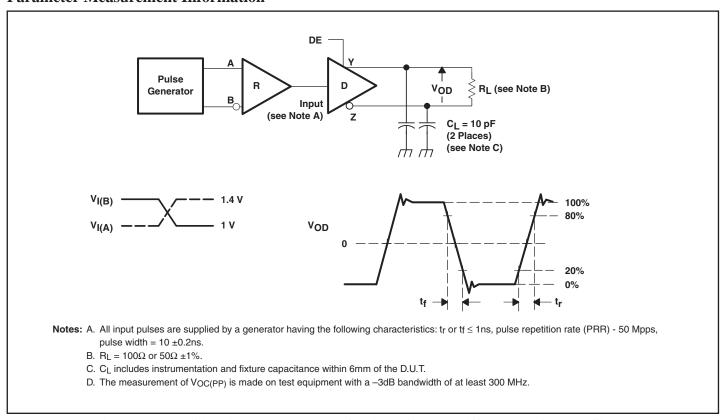

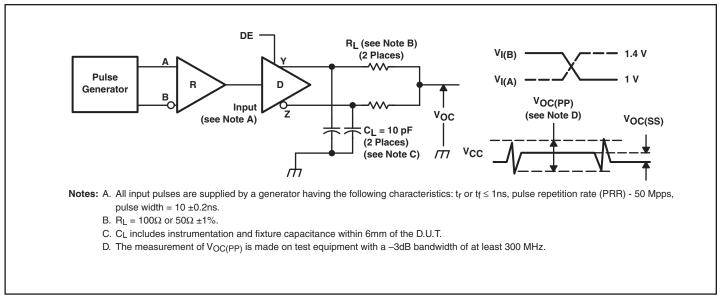

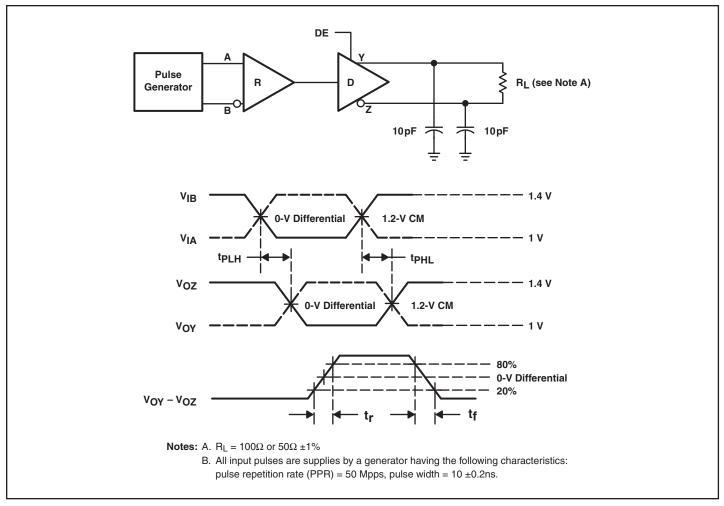

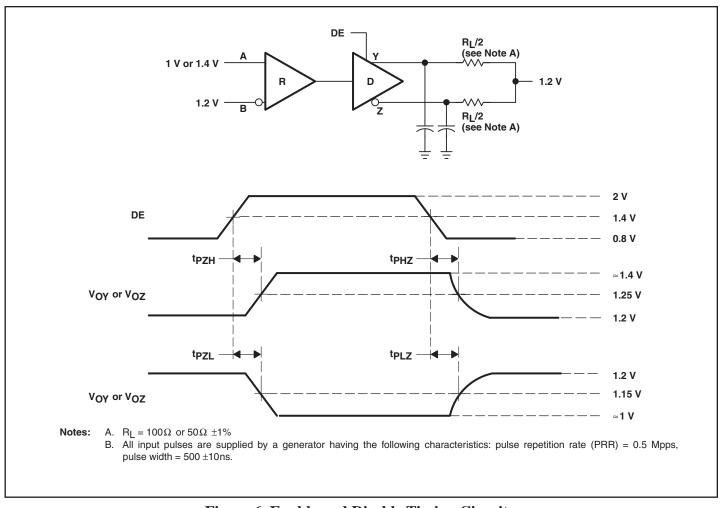

### **Parameter Measurement Information**

Figure 3. Test Circuit and Voltage Definitions for the Differential Output Signal

Figure 4. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

08-0295 7 PS8485F 11/11/08

Figure 5. Differential Receiver to Driver Propagation Delay and Driver Transition Time Waveforms

08-0295 8 PS8485F 11/11/08

Figure 6. Enable and Disable Timing Circuit

08-0295 9 PS8485F 11/11/08

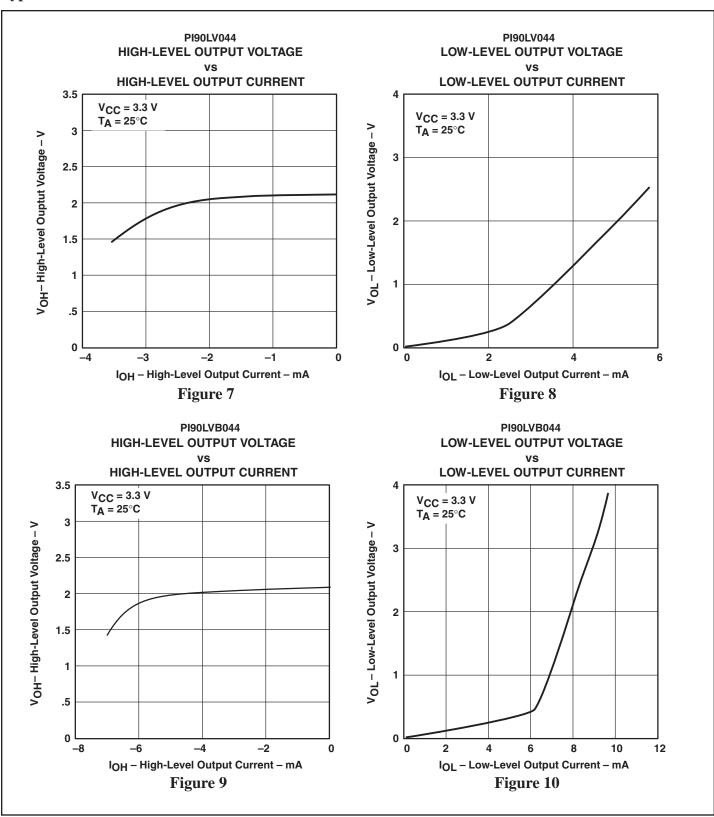

## **Typical Characteristics**

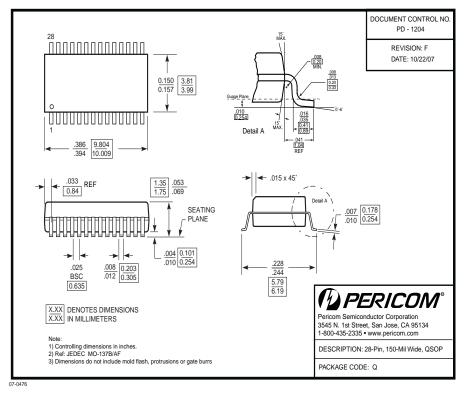

## Packaging Mechanical: 28-Pin QSOP (Q)

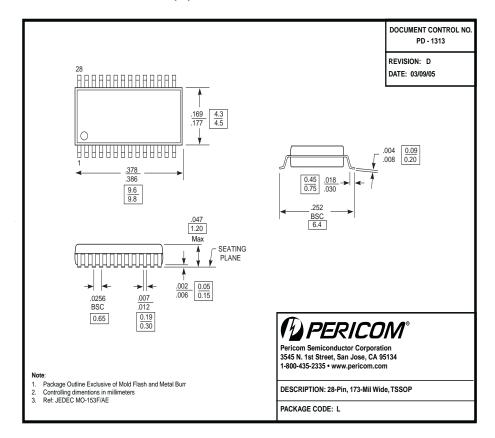

# Packaging Mechanical: 28-Pin TSSOP (L)

11/11/08

# **Ordering Information**

| Ordering Code | Package Code | Package Type                          |

|---------------|--------------|---------------------------------------|

| PI90LV044QE   | Q            | Pb-free & Green, 28-Pin 150-mil QSOP  |

| PI90LV044LE   | L            | Pb-free & Green, 28-pin 170-mil TSSOP |

| PI90LVB044QE  | Q            | Pb-free & Green, 28-Pin 150-mil QSOP  |

| PI90LVB044LE  | L            | Pb-free & Green, 28-pin 170-mil TSSOP |

### **Notes:**

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. Number of Transistors = TBD